Полевой транзистор

Текст

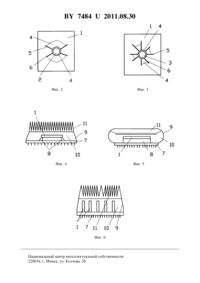

(51) МПК НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ(71) Заявитель Тамков Николай Леонтьевич(72) Автор Тамков Николай Леонтьевич(73) Патентообладатель Тамков Николай Леонтьевич(57) 1. Полевой транзистор на подложке микропроцессора, размещенного на платформе,состоящий из элемента, называемого затвором, и полосок истока и стока, которые входят в состав электронных схем, отличающийся тем, что элементы затвора и полоски истока и стока выполнены на поверхности с двух сторон полупроводниковой подложки и составлены в электронные схемы, причем элементы затвора выполнены отдельно на каждой стороне или соединены сквозным токопроводящим материалом в каждую пару для группы полосок истока и стока. 2. Полевой транзистор по п. 1, отличающийся тем, что элемент затвора выполнен вертикальным по отношению к поверхности полупроводниковой подложки и пропущенным через сквозное отверстие этой подложки, а полоски истока и стока расположены на поверхности подложки перпендикулярно направлению затвора. 3. Полевой транзистор по п. 1 или 2, отличающийся тем, что каждый элемент затвора управляет по меньшей мере одной парой стока и истока. 4. Полевой транзистор по пп. 1-3, отличающийся тем, что каждый элемент транзистора (исток, сток) отделен друг от друга электроизоляционным слоем. 5. Полевой транзистор по пп. 1-3, отличающийся тем, что каждая подложка перпендикулярно или горизонтально установлена на платформе, причем при горизонтальном положении она установлена на специальной подставке, установленной на платформе. 6. Полевой транзистор по пп. 1-4, отличающийся тем, что пространство, в котором расположены одна или более полупроводниковых подложек, заполнено диэлектрической жидкой охлаждающей средой, связанной с пассивной системой охлаждения.(56) 1. Патент РФ 2245589, 2005. Полезная модель относится к области электроники, в частности касается устройств транзисторов электронных схем и их расположения и устройств охлаждения. Известны конструкции транзисторов, в частности полевых, размещенных на полупроводниковой подложке и состоящих из элементов затвора и элементов, состоящих из полосок истока и стока, входящих в состав электронных интегральных схем, которые размещены на поверхности с одной стороны полупроводниковой подложки, а второй стороной подложка приклеена и припаяна к платформе и закрыта защитным корпусом 1. Расположение слоев проводников электронных схем с одной стороны полупроводниковой подложки в значительной степени понижает эффективное использование ее полезной площади и увеличивает относительную толщину слоев микросхем, размещенных в установленных размерах полупроводниковой подложки. С увеличением количества компонентов и слоев для их соединения увеличивается нагрев элементов микросхем, особенно в нижних слоях. Такая конструктивная особенность требует эффективных систем охлаждения, а они являются сложными и объемными устройствами. Причем существующие системы охлаждения охлаждают не сам кристалл, а корпус, в который он упакован. Такая конструкция с трудом позволяет традиционными методами достаточно эффективно держать более или менее стабильную температуру микропроцессора. Важной особенностью охлаждения является не переохлаждать и не допускать значительного повышения температуры, так как большие перепады температур способствуют ускорению разрушения компонентов электронных схем микропроцессора. Также уместным будет отделить понятия платформа для микропроцессора и системная плата. Задачей полезной модели является повышение эффективного использования площади полупроводниковой подложки и экономичного размещения элементов полевых транзисторов и более эффективное их охлаждение. Поставленная задача решается тем, что полевой транзистор и его расположение на полупроводниковой подложке микропроцессора, размещенного на платформе, состоящий из элемента, называемого затвором, и полосок истока и стока, которые входят в состав электронных схем, отличается тем, что элементы затвора и полоски истока и стока выполнены на поверхности с двух сторон полупроводниковой подложки и составлены в электронные схемы, причем элементы затвора выполнены отдельно на каждой стороне или соединены сквозным токопроводящим материалом в каждую пару для группы полосок истока и стока. Для экономичного размещения полевых транзисторов на полупроводниковой подложке элемент затвора выполнен вертикальным по отношению к поверхности полупроводниковой подложки и пропущенным через сквозное отверстие этой подложки, а полоски истока и стока расположены на поверхности подложки перпендикулярно направлению расположения затвора. Каждый элемент затвора управляет по меньшей мере одной парой стока и истока. Каждый элемент транзистора (исток, сток) отделен друг от друга электроизоляционным слоем. С целью эффективного доступа охлаждающей среды к греющимся элементам микросхем каждая полупроводниковая подложка установлена перпендикулярно или горизонтально на платформе, причем при горизонтальном положении, она установлена на специальной подставке, установленной на платформе. Для эффективного охлаждения одной или более полупроводниковых подложек пространство, в котором расположены одна или более полупроводниковых подложек, заполнено диэлектрической жидкой охлаждающей средой, связанной с пассивной системой охлаждения. 2 74842011.08.30 На нынешнем этапе в качестве диэлектрической жидкой среды можно использовать трансформаторное масло. Использование заявленного технического решения позволит в два раза эффективнее использовать поверхность полупроводниковой подложки и тем самым при определенном технологическом процессе в два раза увеличить размещение электронных компонентов на полупроводниковой подложке определенного размера. Использование жидкостной пассивной системы охлаждения позволит с одинаковой эффективностью охлаждать две поверхности полупроводниковой подложки, на которых размещены электронные компоненты. Использование вертикального расположения элементов затвора и перпендикулярного к ним расположения полосок истока и стока позволит существенно сократить площадь размещения полевых транзисторов и, возможно, уменьшит утечку токов и всевозможные нежелательные эффекты, связанные с ними, а также продлит срок действия закона Мура. На представленных чертежах изображены на фиг. 1 - элементы полевого транзистора в разрезе на фиг. 2 - полевой транзистор, вид сверху на фиг. 3 - полевой транзистор вид сверху на вторую поверхность полупроводниковой подложки на фиг. 4 - расположение полупроводниковых подложек на платформе и вид на систему охлаждения (показано горизонтальное расположение подложек) на фиг. 5 - вид на систему охлаждения сбоку. Полевой транзистор на подложке микропроцессора состоит (фиг. 1) из расположенных на полупроводниковой подложке 1 элементов затвора 2 и 3, изолированных слоем 4 оксида кремния. На двух поверхностях полупроводниковой подложки размещены полоски истока 5 и стока 6. На фиг. 4 изображена платформа 7, на которой на специальной подставке 8 размещена полупроводниковая подложка 1. Система охлаждения состоит из корпуса 9, объем 10 которого заполнен диэлектрической жидкой охлаждающей средой,циркуляция которой осуществляется через радиатор 11 по замкнутому кругу. Полевой транзистор и его расположение на подложке микропроцессора действует и охлаждается следующим образом. Во время работы микропроцессора компоненты электронных схем нагревают жидкую охлаждающую среду, которой заполнен объем 10. Нагретая жидкая охлаждающая среда будет замещаться более холодной, поступающей из области радиатора 11, и охлаждать греющиеся компоненты электронных схем. Таким образом будут создаваться благоприятные условия для работы компонентов (в частности, полевых транзисторов), которые входят в состав электронных схем микропроцессоров. Перпендикулярное по отношению к поверхности подложки 1 направление электрического тока в одном или в обратном направлении будет создавать в кремниевой подложке 1 круговое магнитное поле, которое будет управлять движением тока истоков 5 и стоков 6, расположенных вокруг элементов затвора 2 и 3. Предложенная структура расположения элементов затвора 2 и 3, а также расположение полосок истоков 5 и стоков 6 с учетом современных методов обработки и нанесения слоев из полупроводниковых компонентов позволит открыть новое направления создания трехмерного и компактного размещения интегральных микросхем, используемых в микропроцессорах. Использование и дальнейшее усовершенствование системы охлаждения позволит без ограничения наращивать мощность и функциональность микропроцессора. Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20. 4

МПК / Метки

МПК: G05D 23/30, G06F 1/20

Метки: транзистор, полевой

Код ссылки

<a href="https://by.patents.su/4-u7484-polevojj-tranzistor.html" rel="bookmark" title="База патентов Беларуси">Полевой транзистор</a>

Предыдущий патент: Деталь с многослойным покрытием рабочей поверхности

Следующий патент: Учебно-тренировочный комплекс авиационный для обучения летных и кабинных экипажей действиям в чрезвычайных ситуациях

Случайный патент: Лазер с двухсторонней поперечной диодной накачкой