Интегральная микросхема

Номер патента: 15363

Опубликовано: 28.02.2012

Авторы: Листопадов Андрей Викторович, Белоус Виктор Анатольевич, Сякерский Валентин Степанович, Дрозд Сергей Евгеньевич

Текст

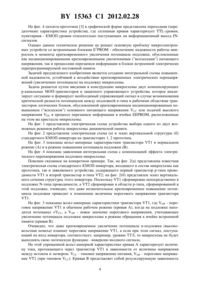

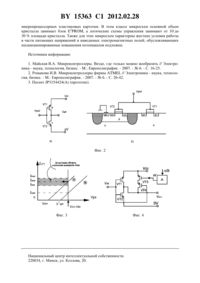

(51) МПК НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ(71) Заявитель Открытое акционерное общество ИНТЕГРАЛ(72) Авторы Сякерский Валентин Степанович Белоус Виктор Анатольевич Листопадов Андрей Викторович Дрозд Сергей Евгеньевич(73) Патентообладатель Открытое акционерное общество ИНТЕГРАЛ(57) Интегральная микросхема, реализующая логическую функцию инверсии, содержащая первый полевой транзистор первого типа проводимости и второй полевой транзистор второго типа проводимости, причем затворы этих транзисторов соединены с информационным входом микросхемы, исток первого полевого транзистора первого типа проводимости соединен с положительной шиной питания микросхемы, его сток соединен с выходом микросхемы и стоком второго полевого транзистора второго типа проводимости, исток которого соединен с общей шиной питания, отличающаяся тем, что содержит защитное управляющее устройство, первый и второй дополнительные транзисторы первого типа проводимости, причем исток первого дополнительного транзистора первого типа проводимости соединен с положительной шиной питания микросхемы, затвор соединен с выходом защитного управляющего устройства, вход которого соединен с входом управления режимом записи-чтения ячеек встроенной электрически перепрограммируемой памяти микросхемы , а его сток соединен с истоком второго дополнительного транзистора первого типа проводимости, сток которого соединен с выходом микросхемы,а затвор соединен с информационным входом микросхемы. 15363 1 2012.02.28 Изобретение относится к области микроэлектроники, в частности к конструкции и схемотехнике интегральных КМОП-микросхем, в том числе как к микросхемам динамической оперативнойпамяти, так и к цифровым и аналоговым микросхемам, содержащим в своем составе блоки встроенныходнократно или многократно электрически перепрограммируемых запоминающих устройств (ЭППЗУ или ). Изобретение также может быть использовано при проектировании и изготовлении различных радиоэлектронных устройств, содержащих перепрограммируемые элементы памяти. Отличительной особенностью широко известных 1 КМОП-микросхем со встроенными блоками 2 является необходимость использования при их эксплуатации как минимум двух типов (номиналов) напряжений - стандартного напряжения питания(обычно 3,0 или 5,0 В) и повышенного(обычно от 10 до 20 В), которые необходимо подавать на специальные или универсальные выводы микросхемы только при осуществлении процесса записи (перезаписи) информации во внутренний встроенныйблок ячеек памяти. В большинстве современных БИС ЭППЗУ и БИС микроконтроллеров со встроенной перепрограммируемой памятью с целью сокращения количества выводов корпуса микросхемы используется только один положительный вывод питания (3 или 5 В), а высокое напряжение формируется уже внутри кристалла специальными блокамиумножителями напряжения. Например, интегральная схема микроконтроллера выполняет набор стандартных логических и (или) арифметических операций (И-НЕ, ИЛИ-НЕ, сложения, умножения и т.д.), при этом часть необходимых для вычислений численных значений различных коэффициентов, параметров, данных берутся из внутренней памяти этого же микроконтроллера 2. При выполнении процедуры стирания предыдущей информации или записи новой информации (данных, коэффициентов, индексов и т.д.) во внутреннюю память на соответствующую управляющую шину встроенного блока памяти (или на высоковольтный вывод микросхемы) подается высокое (до 20 В) напряжение. Поскольку полупроводниковая подложка микросхемы является общей для логических элементов и элементов встроенной памяти, независимо от того, подается это напряжение непосредственно на подложку или нет, оно в любом случае вносит электрические возмущения (кратковременные всплески напряжения) в работу стандартных логических элементов и блоков и приводит к известному эффекту кратковременного электрического перенапряжения подложки микросхемы. Поэтому в большинстве стандартных электронных устройств обычно вводятся временные ограничения на работу логических блоков ИС во время обращения к встроенной памяти. Очевидно, что этот недостаток известных интегральных микросхем со встроенными блоками ячеек памяти ухудшает их производительность (быстродействие), ограничивает их функциональные возможности, уменьшает надежность их работы в составе радиоэлектронных систем и устройств. Проблема усугубляется для случая, когда на входы подобной КМОП схемы поступают логические сигналы, отличные по уровням от стандартных КМОП-уровней, например от биполярной микросхемы ТТЛШ или И 2 Л-типа. Аналогичная задача возникает в динамических ОЗУтак же, как и в 2,принадлежащих к классу микросхем памяти. Здесь обычно требуется алгоритмическим или аппаратным путем выбирать один из двух вариантов либо , работающую с входными -уровнями, либо , работающую с входными -уровнями. В известных из уровня техники средствах решения этой задачи 3 предлагается аппаратный метод путем введения в структуру кристалла микросхемы дополнительной площадки (на каждый информационный вход - одна дополнительная площадка), стандартного инвертора, дополнительного транзистора -типа проходного транзисторного ключа и цепи 15363 1 2012.02.28 транзисторных инверторов обеспечивается аппаратная реализация алгоритма выбора одного из двух вариантов логических уровней - биполярного ТТЛ или КМОП. Известное устройство 3 (фиг. 1) содержит стандартный инвертор на транзисторах 1,2, дополнительный транзистор 3 -типа, проходной ключ на паре -канального 5 и-канального 4 транзисторов и последовательно соединенную цепь инверторов 7, 8, связанных с дополнительной площадкой 6, причем истоки основного 1 и дополнительного 3-канальных транзисторов соединены с положительной шиной питания, их затворы соединены с информационным входомустройства, затвор -канального транзистора 5 проходного ключа соединен с выходом первого дополнительного инвертора 7, затвор второго дополнительного -канального транзистора 4 проходного ключа соединен с выходом второго логического инвертора 8, стоки дополнительных транзисторов 4, 5 проходного ключа соединены с выходом устройства, исток -канального транзистора 2 базового инвертора соединен с общей шиной, выходомустройства и со стоками транзисторов 4,5 проходного ключа, причем затвор -канального транзистора 5 соединен с выходом первого инвертора 7, а затвор -канального транзистора 4 соединен с выходом второго инвертора 8, вход первого инвертора 7 соединен с дополнительной площадкой 6. Кратко опишем работу этого устройства. Если в случае использования 5 В питания на дополнительную площадкупостоянно подавать высокий логический уровень 1 (например, разварить ее на вывод шины питания 5 В , что обычно и делается на практике), и -канальный транзистор 5, и-канальный транзистор 6 проходного ключа будут заперты, соответственно будет заперт и дополнительный транзистор 3. В этом случае базовый инвертор на транзисторах 1, 2 на выходе устройстваформирует сигналы стандартных ТТЛ - логических уровней, которые поступают дальше на управление логикой(схемы обрамления записи/считывания и др.). Если же на дополнительную площадку 6 постоянно подавать во время работы низкий уровень напряжения (аналогично соединив ее с нулевым выводом микросхемы), то данное устройство будет формировать на выходе сигналы с чистыми КМОП-уровнями. Действительно, в этом случае оба плеча 4, 5 проходного ключа открыты, открывается дополнительный транзистор 3. Выбирая соотношение ширин каналов этого транзистора 3 и транзисторов 1, 2 базового инвертора, можно не только обеспечивать стандартные КМОПуровни, но и любые требуемые нестандартные (это решение давно известно и более 20 лет используется схемотехниками-практиками). Недостаток этого решения поскольку дляосновные технико-экономические характеристики (цена прежде всего) определяются размером (площадью) кристалла, а каждая дополнительная площадка приводит к увеличению площади и к потере примерно цента цены, а по сути изобретения таких площадок надо столько, сколько используется информационных входов. Например, для параллельного 32-разрядногопотребуется 32 дополнительные площадки, что практически удваивает площадь кристалла. Если же использовать на кристалле только одну общую площадку (схемотехническими методами это реализуемо), то возникают проблемы с разводкой металлизированных шин соединений выходов общих инверторов 7 и 8 с транзисторами 4, 5 проходных ключей для каждого информационного входа микросхемы. Поэтому в кристаллах -памяти фирмы-заявителя Мицубиси до сих пор в большинстве известных случаев используется техническое решение, взятое заявителем патента Озаки Нидееки в качестве прототипа и представленное на фиг. 2 в тексте описания патента 3. Здесь вместо дополнительной по патенту площадки 6 в цепи инверторов 7, 8 и пары транзисторов 4, 5 применяется плавкая перемычка 9, включенная последовательно между стоком -канального транзистора 3 и выходом . Если перемычку пережечь, устройство работает с -уровнями, если не пережигать - с КМОП-уровнями. 15363 1 2012.02.28 На фиг. 4 патента-прототипа 3 в графической форме представлена переходная (передаточная) характеристика устройства, где сплошная кривая характеризует -уровни,пунктирная - КМОП-уровни относительно поступающих на информационный выход сигналов. Однако данное техническое решение не решает основную проблему микроэлектронных устройств со встроенными блоками 2 - обеспечение надежности работы микросхем в моменты кратковременного увеличения потенциала подложки, обусловленные как несанкционированными кратковременными увеличениями (всплесками) питающего напряжения, так и процессами перезаписи информации в блоках встроенной электрически перепрограммируемой постоянной памяти. Задачей предлагаемого изобретения является создание интегральной схемы повышенной надежности, устойчивой к воздействию кратковременных электрических перенапряжений (увеличению потенциала) на подложку микросхемы. Задача решается путем введения в конструкцию микросхемы двух компенсирующих-канальных МОП-транзисторов и защитного управляющего устройства, которое анализирует ситуацию и формирует необходимый управляющий сигнал в случае возникновения критической разности потенциалов между подложкой -типа и рабочими областями транзисторов логических блоков, обусловленной кратковременным несанкционированным повышением (всплеском) основного питающего напряженияили подачей высокого напряженияв процессе перезаписи информации в ячейки , расположенные на этом же кристалле микросхемы. На фиг. 1 представлена электрическая схема устройства выбора одного из двух возможных режимов работы микросхемы динамической памяти. На фиг. 2 представлена электрическая схема (а) и эскиз вертикальной структуры (б) стандартного КМОП-инвертора на транзисторах 1, 2 прототипа. На фиг. 3 показаны вольт-амперные характеристики транзистора 1 в нормальном режимеи в режиме повышения потенциала подложки . На фиг. 4 показана заявленная интегральная схема с компенсацией эффекта электрического перенапряжения подложки микросхемы. Поясним сказанное на конкретном примере. Так, на фиг. 2(а) представлена известная электрическая схема стандартного КМОП-инвертора, входящего в состав микросхемы как прототипа, так и заявляемого устройства, содержащего первый транзистор -типа проводимости 1 и второй транзистор -типа 2 на фиг. 2(б) представлен эскиз вертикального сечения структуры этого инвертора. Поскольку 1 сформирован непосредственно в подложке -типа проводимости, а 2 сформирован в области -типа, сформированной в этой подложке, очевидно, что даже незначительное кратковременное повышение потенциала подложки приводит к изменению величины порогового напряжения транзистора 1. На фиг. 3 показаны вольт-амперные характеристики транзистора 1, где- пороговое напряжение 1 в обычном рабочем режиме (кривая ), когда на подложке находится потенциал , а- новое значение порогового напряжения, учитывающее увеличение потенциала подложки микросхемы в режиме обращения к ячейке встроенной памяти (кривая ). Очевидно, что даже кратковременное увеличение потенциала -подложки (высоковольтная помеха) изменит пороговое напряжение 1, а если при этом сигнал, поступающий на вход инвертора, соответствует, например, уровню ТТЛ, то микросхема не будет выполнять свою логическую функцию - инверсию входного сигнала. На этой упрощенной вольт-амперной характеристике криваяхарактеризует величину тока, протекающего через транзистор 1 в зависимости от величины напряжения между истоком и затвором- типовое напряжение питания,- пороговое напряжение 1 (при типовом ). Криваяпредставляет собой результирующую зависимость 4 15363 1 2012.02.28 при увеличении потенциала подложки. Здесь отмечено численное значение нового уровня порогового напряжения . Как видно, если входное напряжениесоответствует значению логического нуля, для некоторого значения, равного разнице ( - ),может возникнуть ситуация, когда величина рабочего тока уменьшится ниже минимального допустимого значения, необходимого для обеспечения нормальной работы микросхемы, при . Интегральная микросхема, реализующая логическую функцию инверсии, содержит первый полевой транзистор первого типа проводимости и второй полевой транзистор второго типа проводимости, причем затворы этих транзисторов соединены с информационным входом микросхемы, исток первого полевого транзистора первого типа проводимости соединен с положительной шиной питания микросхемы, его сток соединен с выходом микросхемы и стоком второго полевого транзистора второго типа проводимости, исток которого соединен с общей шиной питания, отличающаяся тем, что содержит защитное управляющее устройство, первый и второй дополнительные транзисторы первого типа проводимости, причем исток первого дополнительного транзистора первого типа проводимости соединен с положительной шиной питания микросхемы, затвор соединен с выходом защитного управляющего устройства, вход которого соединен с входом управления режимом записи-чтения ячеек встроенной электрически перепрограммируемой памяти микросхемы , а его сток соединен с истоком второго дополнительного транзистора первого типа проводимости, сток которого соединен с выходом микросхемы,а затвор соединен с информационным входом микросхемы. Конструкция интегральной микросхемы инвертора 3 известна, однако сравнение свойств заявленного и известного технических решений показало, что именно введение в известную конструкцию первого и второго дополнительных транзисторов первого типа проводимости и защитного управляющего устройства позволяет повысить надежность функционирования интегральной микросхемы за счет исключения (компенсации) эффекта влияния электрических перенапряжений (повышения потенциала) подложки, возникающих как при несанкционированных повышениях питающего напряжения, так и при подаче повышенных напряжений, необходимых для организации процессов перезаписи информации в ячейках блока встроенной в микросхемы электрически перепрограммируемой внутренней памяти типа . На фиг. 4 представлена интегральная микросхема с компенсацией эффекта электрического перенапряжения подложки, поясняющая сущность предлагаемого изобретения. В этой микросхеме, также реализующей логическую функцию инверсии, содержащей первый полевой транзистор первого типа (-типа) проводимости 1 и второй транзистор второго типа (-типа) проводимости 2, причем затворы этих транзисторов соединены с информационным входоммикросхемы и с затвором второго дополнительного-канального транзистора 4, исток первого полевого транзистора 1 соединен с положительной шиной питаниямикросхемы, его сток соединен со стоком второго дополнительного -канального транзистора 4, с выходоммикросхемы и с истоком транзистора 2, сток которого соединен с общей шиной 0, причем исток первого дополнительного -канального транзистора 3 соединен с положительной шиной питания, его сток соединен с истоком второго дополнительного -канального транзистора 4, затвор которого соединен с информационным входомзатворами транзисторов 1 и 2, а затвор первого дополнительного -канального транзистора 3 соединен с выходомзащитного управляющего устройства , вход которого соединен со входом разрешающего сигнала записи/чтения / микросхемы. Как следует из анализа фиг. 4, предложено схемотехническое решение, обеспечивающее надежное функционирование микросхемы даже во время реализации цикла режимов записи (стирания) информации во встроенную в этот же кристалл внутреннюю память 2. 5 15363 1 2012.02.28 Сущность заявляемого решения заключается во введении в состав микросхемы двух-канальных транзисторов 3, 4 и защитного управляющего устройства , которое в процессе записи (считывания) по внешнему сигналу / формирует соответствующий внутренний управляющий сигналв случае возникновения критической разницы потенциалов между подложкой -типа и рабочими областями активной структуры транзисторов 1, 2. В режимах записи (стирания) устройствопосредством управляющего сигнала / делает проводящим или блокирует транзистор 3 в зависимости от появления или отсутствия на подложке предельного напряжения. Цепь активных -канальных транзисторов 3-4 обеспечивает появление необходимого дополнительного тока только в режиме записи и обеспечивает их отключение в нормальном рабочем режиме. Фактически последовательная цепь транзисторов 3-4 включается параллельно между положительной шиной питания и стоком 1 таким образом, что 4 открывается одновременно с 2 (затворы 1, 2 и 4 объединены), увеличивая выходной ток каскада в нужный момент. Затвор транзистора 3 управляется сигналом , формируемым устройством , таким образом, что 3 открывается только в случае повышения потенциала подложки(0), что обычно происходит в режиме записи. В обычном рабочем режиме 3-5 и транзистор 3 блокирован (закрыт). Рассмотрим работу этой микросхемы еще более детально. Когда напряжение на входе микросхемысоответствует уровню логической 1, транзистор 2 открыт, а транзистор 1 блокирован (закрыт). Поскольку транзистор 2 сформирован в -области, соединенной с общей шиной земля, на его режим не влияет наличие на подложке повышенного напряжения, а транзистор 4 выключен и цепь 3-4 не выдает ток подкачки на выход схемы. Когда входное напряжениесоответствует уровню логического 0, а сигналсоответствует низкому логическому уровню, на подложку подается повышенное напряжение, которое ухудшает условия работы транзистора 1 - резко уменьшается выходной ток в силу вышеизложенных причин (фиг. 3). В это же время включается цепь транзисторов 3-4, которая обеспечивает дополнительный ток, необходимый и достаточный для перевода выхода КМОП-инвертора в состояние логической 1, что и требуется. Геометрические параметры 3 и 4 (соотношение длины и ширины затвора) легко рассчитываются стандартными программами САПР БИС для каждого конкретного случая реализации микросхемы в заданном конструктивно-технологическом базисе. Исследования тестовых кристаллов КМОП БИС с , изготовленных на основе предложенного схемотехнического решения базового КМОП-элемента, подтвердили их работоспособность в широком диапазоне изменения питающих напряжений логических блоков КМОП в режимах перепрограммирования тестовых ячеек . Как следует из описания, предложенное в изобретении техническое решение легко применимо при реализации и других логических функций - ИЛИ, ИЛИ-НЕ, исключающее ИЛИ и т.д. В качестве управляющего устройствав составе интегральной микросхемы целесообразно использовать один общий стандартный блок управления чтением/записью (/),который имеется в составе любой КМОП-микросхемы со встроенным блоком 2. Управляющий сигналот этого блока передается по поверхности кристалла к дополнительным транзисторам основных логических блоков микросхемы с помощью систем металлизированных проводников межсоединений, аналогично другим управляющим и информационным шинам. Поскольку введение дополнительных компенсирующих транзисторов также приводит к увеличению площади кристалла (в десятки раз меньшему, чем у прототипа), одна из эффективных областей применения предложенного технического решения - микросхемы для 6 15363 1 2012.02.28 микропроцессорных пластиковых карточек. В этом классе микросхем основной объем кристалла занимает блок 2, а логические схемы управления занимают от 10 до 30 площади кристалла. Также для этих микросхем характерны жесткие условия работы в части питающих напряжений и наводимых электромагнитных полей, обусловливающих несанкционированные повышения потенциалов подложки. Источники информации 1. Майская В.А. Микроконтроллеры. Везде, где только можно вообразить // Электроника - наука, технология, бизнес. - . Европолиграфик. - 2007. -6. - С. 16-25. 2. Романова И.В. Микроконтроллеры фирмы// Электроника - наука, технология, бизнес. - . Европолиграфик. - 2007. -6. - С. 26-42. 3. Патент 3154424 (прототип). Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20. 7

МПК / Метки

МПК: H03K 19/0948

Метки: микросхема, интегральная

Код ссылки

<a href="https://by.patents.su/7-15363-integralnaya-mikroshema.html" rel="bookmark" title="База патентов Беларуси">Интегральная микросхема</a>

Предыдущий патент: Способ стимуляции репродуктивной функции у свиноматки

Следующий патент: Способ получения дезинфицирующего средства

Случайный патент: Зубной протез