Интегральная схема

Номер патента: 2092

Опубликовано: 30.03.1998

Авторы: Горовой Владимир Владимирович, Силин Анатолий Васильевич, Белоус Анатолий Иванович

Текст

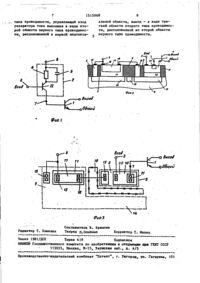

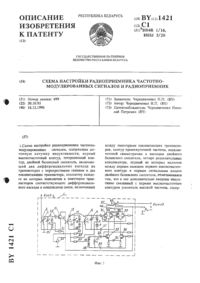

Госуддготвенный номигег по иэоегетениям и покрытиям при п-снт осев(56) Аваев Н. н др. Элементы сверхбольшое интегральная схем. 11. Радиоухвобретення - повьшение быстродейст вшгис, включающей основной переключающий транзистор с подкшаченъдъш к его базе управляемым генератором тока и выполненной на полупроводниковой2 СО СКРНТШШ СЛОЯМИ ЕТОРОГО типа ПРОдводнмости, один из которых вьпзеденна шикарную поверхность схемы с поМОПЕШ Первой области второго типе проводимости. В интегральной схеме повьшенне быстродействия достигается за счет введения двух дополннтелтьньп скрытьпс слоев первого н второго тэта проводимости, ДВУХ областей второго типа проводимости и двух областей первого типа проводимости, причем второй скрытьхй слой второго типа проводиности вьъведен на пленарную по верхность интегральной схемы с поноПСБЮ второй области второго типа проводхшостн, во второй эпитаксиальной области сформирована первая область один из контактов к которой соединен с второй областью второго теша проводимости. 3 ил.водах-псовой электронике, а ноннрет но интегральной микроэлектронике, Целью изобретения является повышение быстродействия интегральной схемы путем уменьшения ВРеМеНН За держкн включения перенлаочательного транзистора .. На фиг. 1 дана электрическая схема вептшш интегральной схемы наньдй разрез не фиг. 3 - топологическая схема интегральной схемы. Интегральная следа вкшочает логические вентили, содержащие основной 38-89переводивший транзистор 1 с подключенннн к его базе управляешь генера- . тором 2 тока, впавший в сноси составе управляющий вход З п резистор А, с - . параллельно подхваченной ему емкостью5, первые вьводьц которых подкшоченьтэотводу 6 пнтащя, а выход 7 гене ратора 2 тока цодктчен к базе перектчаюцего транзистора 1.Интегральная схема выполнена на по- Ъ Пшроводшщовой. подлодке 8 первого типа проодшюстн в выделению неолшптшоа штапеля-решен 9 областях 10 и П нанесенного на поверхности подложки эпитаксиального слоя второготша проводимости. В первой области 10 первый скрытый слой 12 второго гл-ша выведен на пленарную поверхность эштегйадъной схемы с помощью первойв В интегральную схему введен дополни тельный второй скрытый слой 14 второго тиа праведности, введенный на ллаиарНУЮ поверхность интегральной 10 схемы с помощью второй области 15 ВТОРОГО Тиа ПРОВОДНМОСТН. Скрытыйслой 12 отделен от скрытого слоя 14с помощъю третьего скрытого слоя 16 первого типа проводимости и охваты- 15 вает его по меньшей мере с одной. стороны. В области 11 эпитаксиального слоя над скрытым слоем 14 сформрозава первая область 17 первого туша праведности, образующая резистор 4 20 генератора 2 тока с контактами 18 и19 к ней, первый из которым образует первый вывод резистора Е н соединен с ВТОРОЙ Областью 15 второго типа проводиности,а второй - с первой областью 15 13 второго типа проводиости. В перной эпитаксиальной области 10 сферы резака перваяобласть 20 второго ти на проводимости, в которой сформрот вана третья область 21 второто типа 30 проводимости образующая пйход 7 генератора 2 тока и соедиеиная с базой переключающего транзистора 1.0 бласти 10, 20 н 21 со скрытым слоем 12 интегральной схемы образуют соответст- 35 вевно коллектор, базу н эмиттер управляющего транзистора 22,-причембаза (область 20) транзистора 22 образует Управляющий вход 3 генератора тока, а его эмиттер ч выход 7 генера 4 О тора тока, подключений к базе переключателного транзистора 1, область17 с контактами 19 и 18 - токозадающшй элемент - резистор 4 генератора тока, контакт 18 которого подключен 45 к-коллектору транзистора 22, а вы вод к 0 Нт 1 кта.19 - к выводу 6 питания, а паразитная екость между скрытым слоями 12 и 14 и распределенная барьерная еюкость перехода область 11 - 50 подложка 8 первого тише проводимос ти - область 13 образуют емость 5,причем соединение области 11 с выводом 6 питания с помощью скрытогоИнтегральная схема работает следующнн образом.При подаче на управляющий вход 3 генератора 2 тока некого уровня сигнала транзистор 22 находится в закрытом состоянии, выходной ток генератора 2 отсутствует, что обуславливаетзакрытое состояние транзистора 1. Приэтом падение напряжения на резисторе 4 и емости 5 имеет небольшую велиЧннг. При подаче на вход 3 высокого уровня сигнала управляющий транзистор 22 переходит в открытое состоярезистору 4 к коллектору транзистора 22 подлючена емкость 5, которая заряжается иерез открьшающийся трапзистор 22, на выходе 7 генератора 2 тока появляется пульс тока-с макси мальной величиной11- (В) (Ю где 1 - входной токток базы транзистора 22 В - коэффииент усиления токаПосле зарядаемхости 5 значение тока на выходе 7 генератора 2 тока определяется аналогично известному решению резистором 4 и уменьшается до значения 7Чае - прямое падение напряжения перехода база-эмиттер транзистора 1.Таки образом, при подаче на управляющий вход 3 генератора 2 тока высокого уровня сигнала на его выходе 7 появляется имульс тока повышенной величинывтехающий в базы переклчатепьиого транзистора 1 и обеспе чиваюци его форсированое отпираниеи уменьшение времени задержки вклш-2 чения. При подаче на вход 3 генератора 2 тока низкого уровня сигнала транзистор 22 закрывается, вниодой ток генератора 2 уменшается и транзистор 1 переходит в закрытое состоя НИЗ.П р и м е р. Интегральная схема выолвеиа на кремневой монокристалличесхой подлонхе В тиа КД 10 в эпитаксиальном слое КЭФО.5 толшной 2,0 мкм, в котором с помощью описан областей топиной 1 Б 1 В мим выделены области 10 и 11.Под областями 10 и 11 сформированы скрытые слои п-тиа проводимости с поверхностнымсопротивлением Вы 50 ОМ/П. которые выведены на ппанарную поверхность интегральной схем с помощью низко омны областей 13,15 п-типа с поверхностным сопротивлением К 545 Ом/Ц.В участке эпитаксиального слоя сформирована высокоомная область 20 глубиной 1,0 мм и поверхностны сопротивлением К 515 ком/П. ннзкоомныи. металпзированныйконтакт к которойобразует базу управляющего транаистора 22 и вход 3 генератора 2 тока, а в области 20 сформирована нщзноомная область 21 Ьптиа глубиной 0,6 мм и поверхностны сопротипением Е 5 5060 Ом/Е, образующая эмиттер транзистора 22 и выход 7 генератора 2 тока, который посредством металлизированного межсоединенинсоединен сбазой переключательного транзистора 1.В области 11 эпитаксиального слоя сформрована вторая область ртипа глубиной 1,0 мкм с поверхностным со протнленнем В 51,5 ком/Ц, образующая резистор 4 генератора 2 с низкоонными металлизировапии контактами 18 и 19, пей. Контакт 18 металлизирован 153 в-типа, а .контакт 19 образует выт вод питания 6 геператора 2 и соеди нен с областью птипа 15. Между скрытыми слоями 14 и 12 сформирован скрысопротивлением к 52 ооо Ом/п. ВыбранНЫ 2 КОНСТРУКТИВНЫЕ параметры ПОЗВОЛЯют получить коэффициент усиления токаболее 6 В. Это обеспечивает повышенную (до 10 мА при токе базы 1 О 0 мА) велчнну импульса выходного тока генератора 2, что обеспечивает сущест веыное уменьшение времени включения транзистора 1. При этом величина барьерной емкости зпнтаксиальньй слой область 17 р-типа составляет9,23 пФ/мм, а емпость между скрытым слоями 14 и 20,3 пФ/мм, что позволяет получить емкость 5, достаточную для получения импульса вьшодноготока, обеспечивающего уменьшение вре мени включения транзистора 1. Так,например, при напряжении питания 5 В,резисторе 4 величиной 20 ком и вход 30нон тоне 100 мкА максимальный выходной ток генератора составляет 220 мкА, чтопри УКЗЗВННЫ КОНСТРУКТИВНЫХ параметррахинтегральной схемы позволяет по ЛУЧНТЪ эадеРЖКУ переключения.дО нс,в то время какпредлопениое техническое решение позволяет повысить выеднон ток генератора до 5 мА и снизить задержку переключения до 0,8 нс при той же мощности потреблении.Изобретение позволяет повысить быстродействие известной интегральной схемы путем уменьшения задержки включения переклчательного транзнсд тора увеличением его тока базы при вклчении при сохранении мощности потребления за счет использования паразитных емкостей интегральной схемы.на полупроводниковой подложке перво го тиа проводимости, включающая логические вентили с переключательны ТР 3 НЗНСТ 0 Р 0 М Управляеым генератором тока, содержащим управляющий вход,резистор В виде области первого типа проводимости с выводами и параллельно ем ВКЛЮЧЕННЫЙ Конденсатор, причем ПЕРВЫЙ Выод К 5 непи подключен к шине питания, выход, подключенный к базе переключательного транзистора,пегеключательный транзистор и генератор тока расположен-в изолированньш диэлектриком первой и второй областях эпитаксиального слоя второго ТНШ 8 ПР 0 В 0 дНН 0 СТН В первой из которыщ скрытый слой второго типа провоДИМОСТИ ИМЕЕТ ВЫХОД на поверхность посредством первой области второго типа проводимости, о т л и ч а ю щ а я с я тем, что, с цепью повышения быстродействия, подложха дополиително содержит второй и третий скрытые слои второго и первого типов проводимости,вторую и третью области второго тиа проводимости, первую и вторую области первого тиа проводимости, при этом второй скрытый слой второго типа проводимости размещен под второй эпитаксиальной областью второго типа проводиости и выеден на поверхность посредством второй области второго тна проводимости, отделен от первого скрытого слоя второго тиа проводимости третьи скрыты слоем первоготиша проводимости и охватывает его по меньшей мере с одной стороны, первый выч Вод СЦеПН соединен с второй областью второго типа проводимости, а второй соедиен с первой областью второго- д тцпа проводи-шести, управляющий вход альной области, выход в виде ТРе ч Генератора тока вщопнен в виде вто ТЪЕЙ Области ВТРРОГО типа проводимосрой обид-отв первого типа проноднмос- ти, расположенной во ВТОРОЙ дб-дстн. внинпй государственного паштета по-изобретоциш в отхватил при ГКНТ СССР 113035, Москва, ж-зэ, гашеная вы. д. 5/5

МПК / Метки

МПК: H01L 27/08

Метки: интегральная, схема

Код ссылки

<a href="https://by.patents.su/4-2092-integralnaya-shema.html" rel="bookmark" title="База патентов Беларуси">Интегральная схема</a>

Предыдущий патент: Модуль генератора импульсных токов

Следующий патент: RS-триггер

Случайный патент: Трехфазный трансформатор