Центральный процессор для многопроцессорной вычислительной системы

Номер патента: 1192

Опубликовано: 14.06.1996

Авторы: Коваленко Сергей Саввич, Фельдман Владимир Марткович, Зайцев Александр Иванович, Пентковский Владимир Мстиславович

Текст

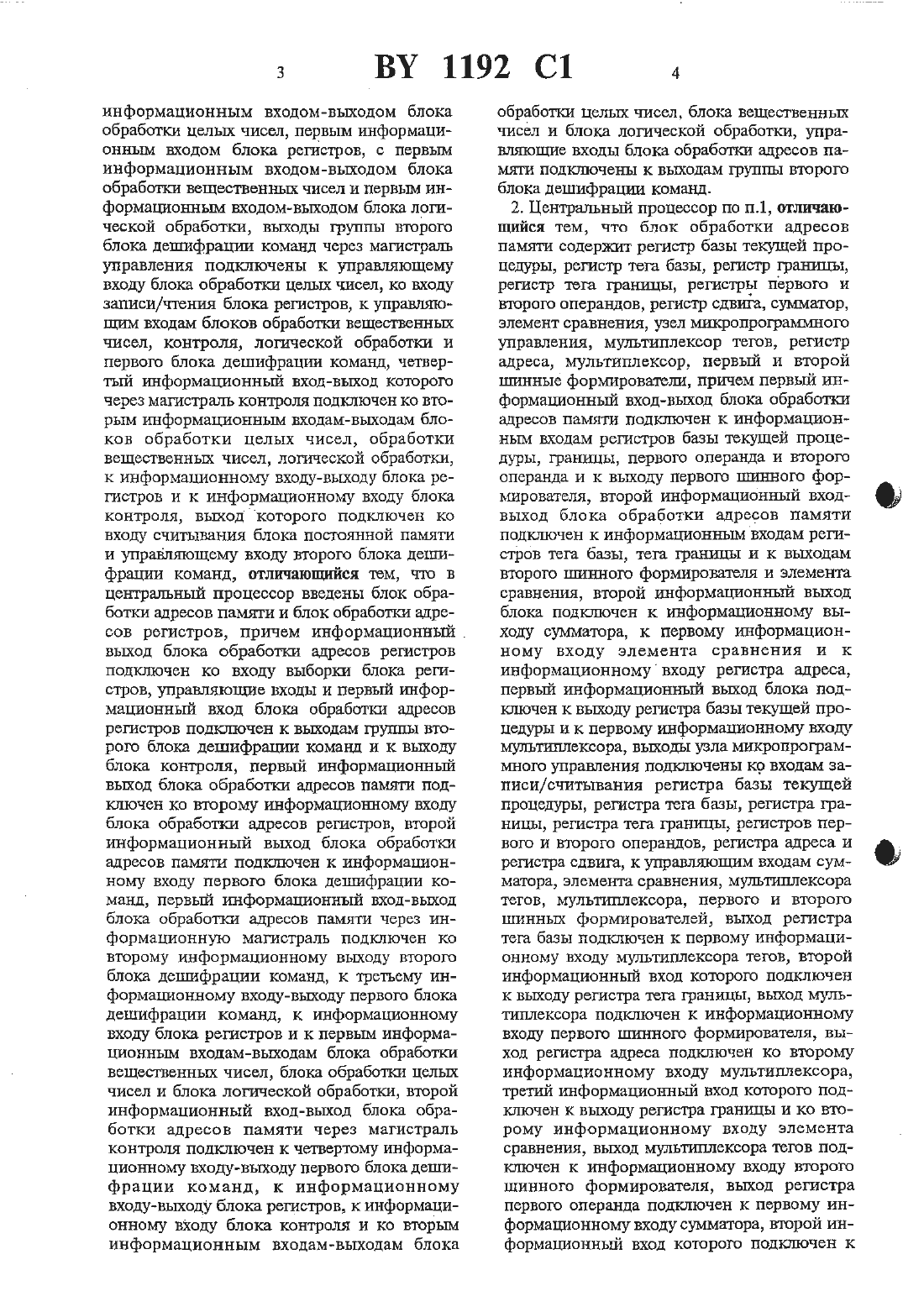

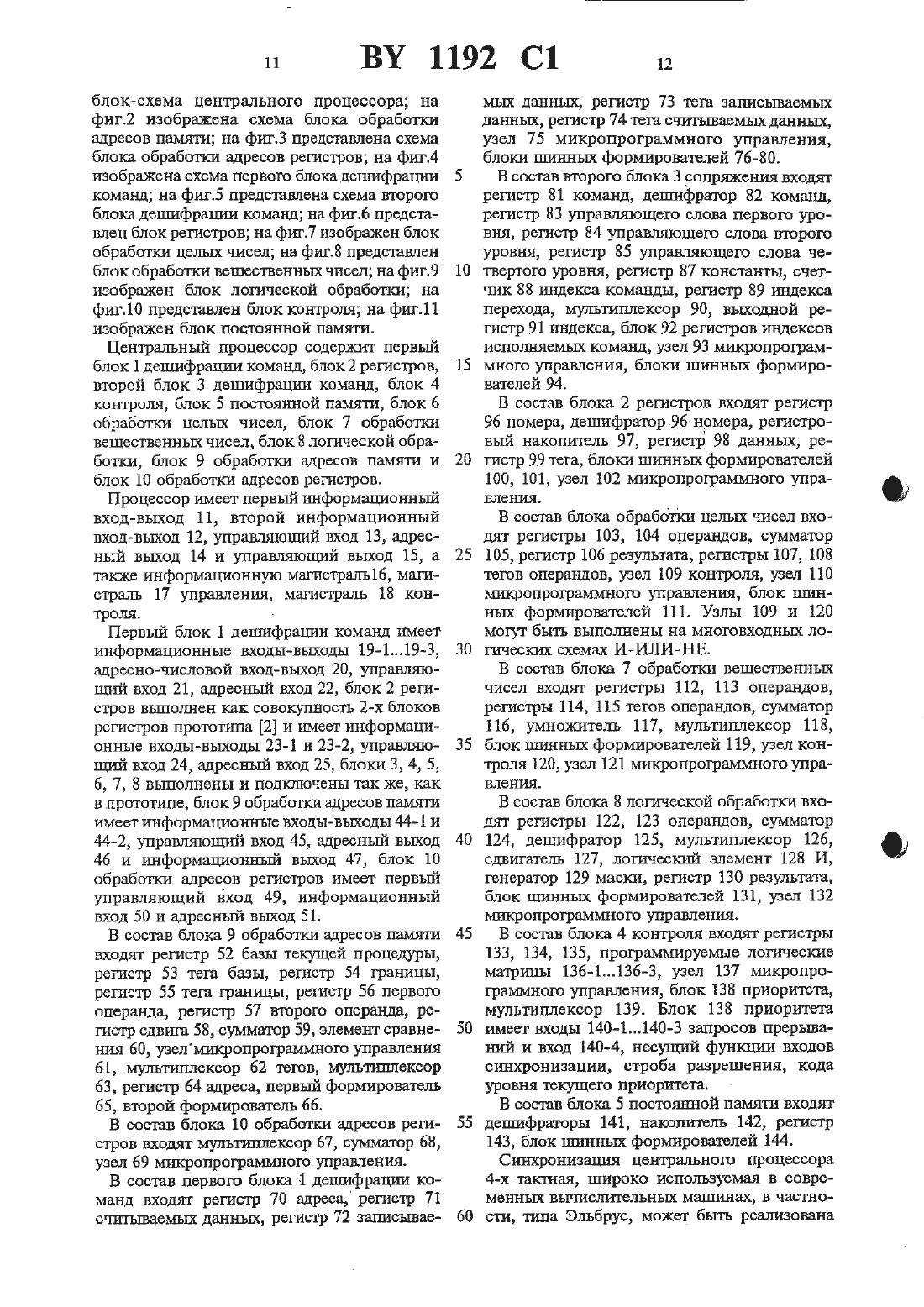

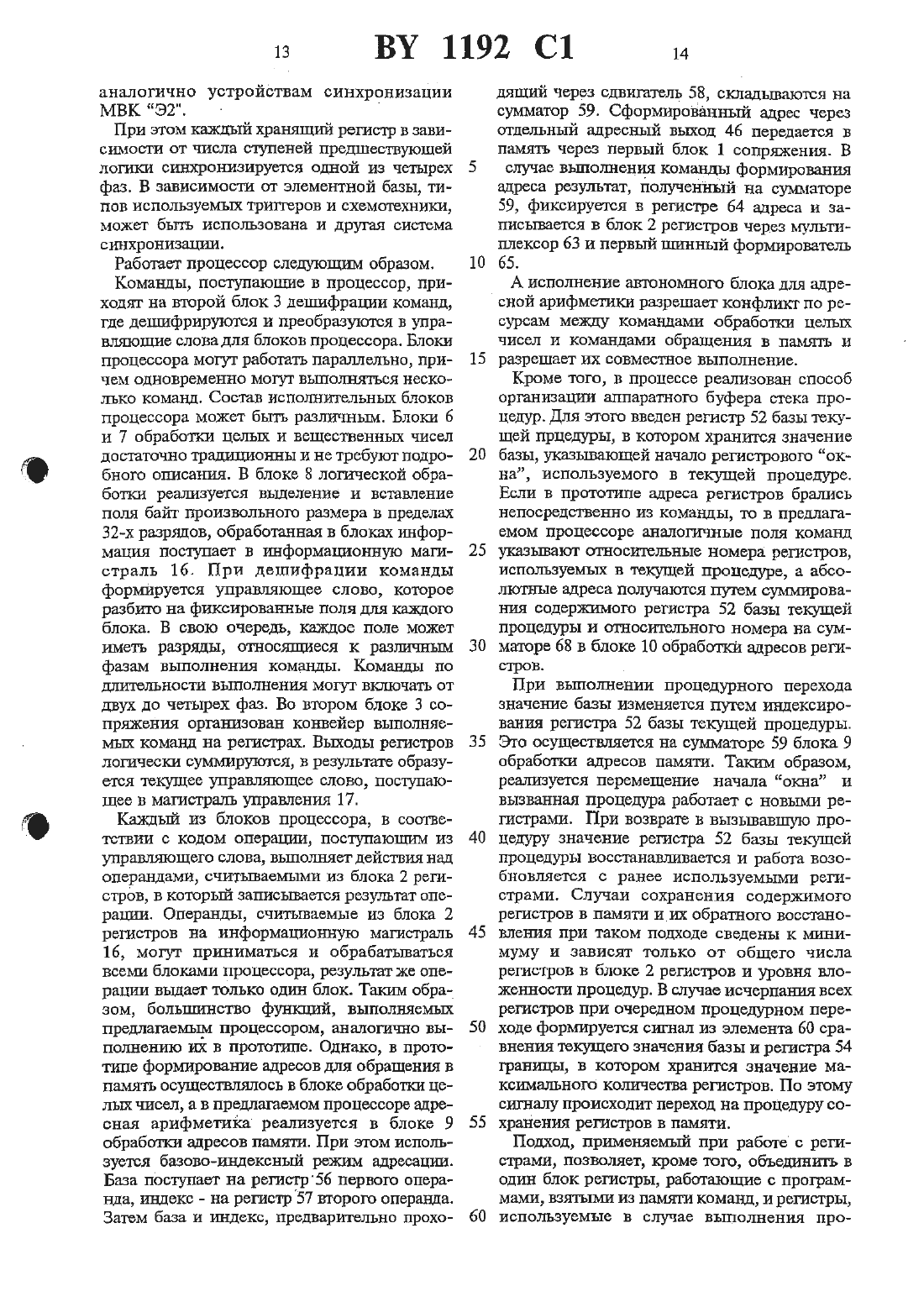

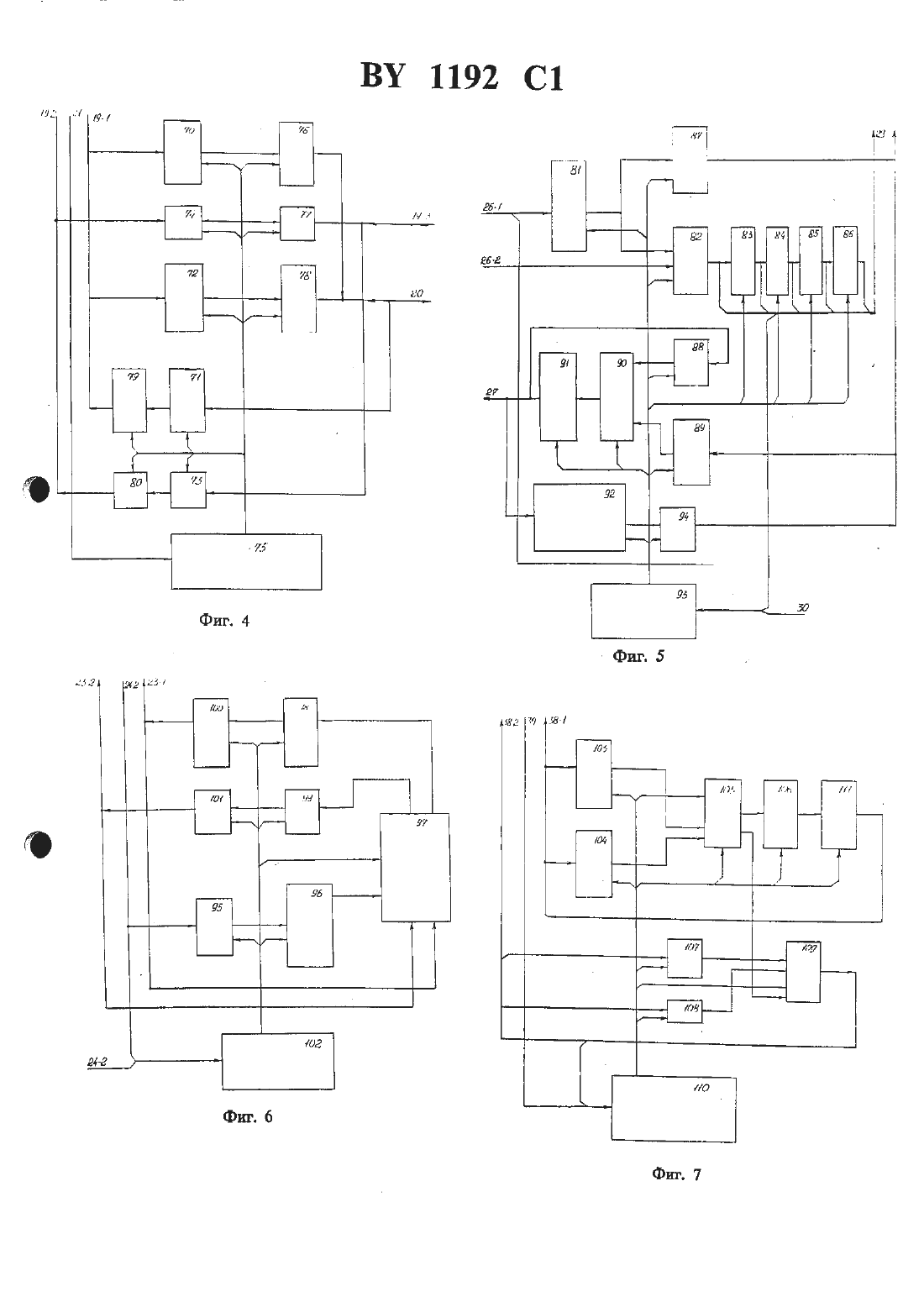

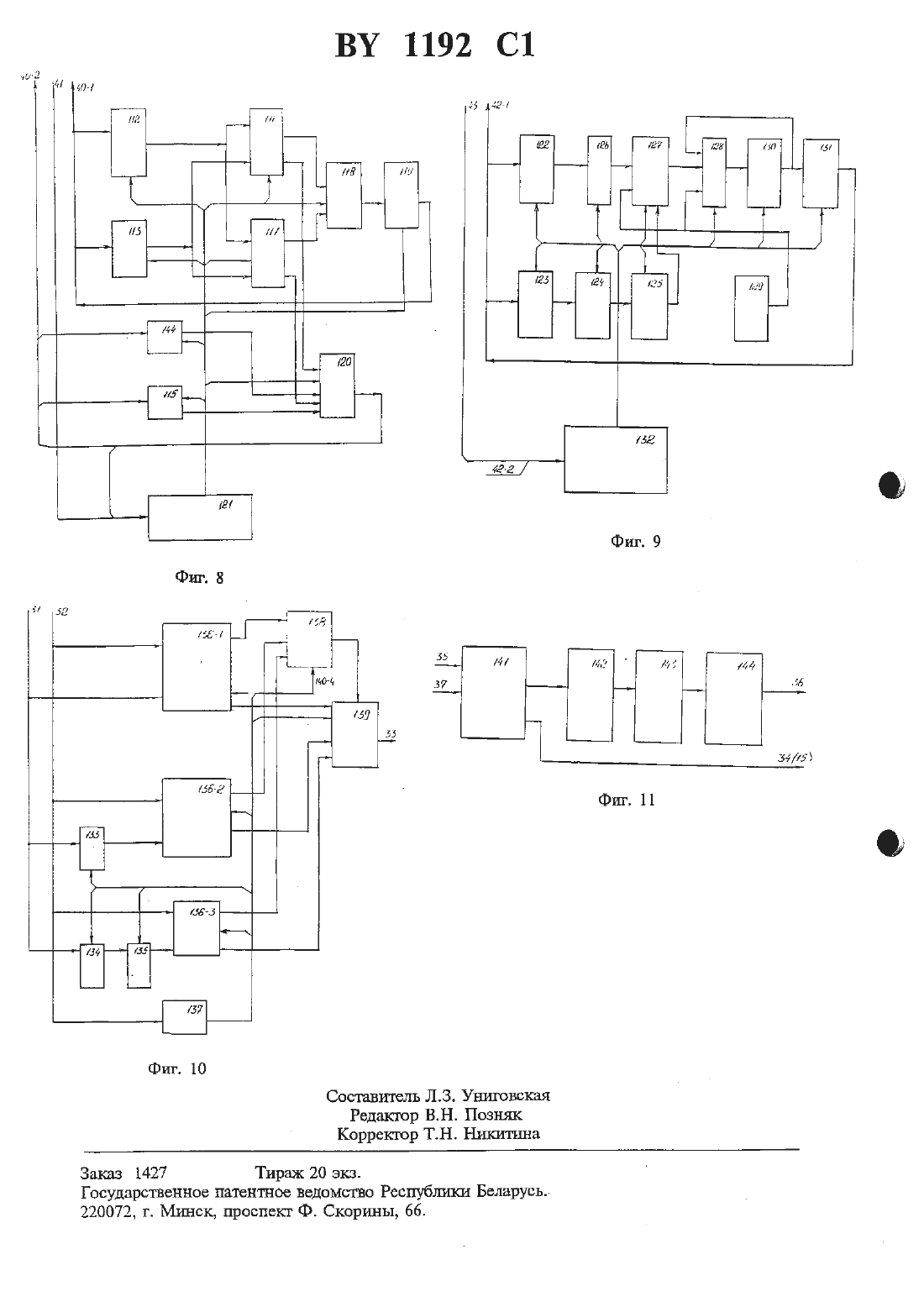

информационным входом-вьтходом блока обработки целых чисел, первым информационным входом блока регистров, с первым информационным входом-выходом блока обработки вещественных чисел и первым информационным входом-выходом блока логической обработки, выходы труппы вюрого блока дешИФРаЦшт команд через магистраль управления подключены к управляющему входу блока обработки Цешях чисел, ко входу заггиси/чгенття блока регистров, к управляло гшш входам блоков обработки вещественных чисел, контроля, логической обработки и первою блока дешифрации команд, четвертый информационный вход-выход которою через магистраль контроля подключен ко вторым штформационнъгм входам-вътходам блоков обработки целых чисел, обработки вещественных чисел, логической обработки,к информационному входу-выходу блока регистров и к информационному входу блока контроля, выход которого подключен ко входу считывания блока постоянной памяти и управляющему входу второю блока леглифрации команд, отличающийся тем, что в центральный процессор введены блок обработки адресов памяти и блок обработки адре сов регистров, причем информационный.выход блока обработки адресов регистров подключен ко входу выборки блока регистров, управляющие входы и первый шафермационньпй вход блока обработки адресов регистров подкшочен к выходам грушты второю блока дешифрашш команд И к выходу блока контроля, первьп 71 информатшонньй выход блока обработки адресов памяти подключен ко второму информационному входу блока обработки адресов регистров, второй информационный выход блока обработки адресов памяти подключен к информационному входу первого блока дешифрадии команд, первый информационный вход-выход блока обработки адресов памяти через информационную магистраль подключен ко второму информационному вътходу второго блока депШФРаЦии команд, к третьему информационнощ входу-выходу первого блока дешифрагши команд, к Ш-формационному входу блока регистров и к первым информационным входам-выходам блока обработтш вещественных чисел, блока обработки целых чисел и блока лопгтческой обработки, второй информационный вход-выход блока обработки адресов памяти через магистраль контроля подключен к четвертому информационному входу-выходу первою блока дешифрации команд, к информационному входу-вьшоцу блока регистров, к информационному входу блока контроля и ко вторым информационным входам-выходам блокаобработки целых чисел, блока вещественных чисел и блока логической обработки, управляющие входы блока обработки адресов памяти подкшочены к выходам труппы второго блока дешифрации команд.2. Централъньп процессор по п.1, отличающийся тем, что блок обработки адресов памяти содержит регистр базы текущей процедуры, регистр тега базы, регистр тратчнцы,регистр тега граг-цшы, регистры первою и второю операндов, регистр сдвига, сумматор,элемент сравнения, узел мтшропрогращшото управления, мультиплексор теюв, регистр адреса, мультиплексор, первъп 7 г и второй плавные формироватетш, причем первый информационный вход-выход блока обработки адресов памяти подключен к информационным входам регистров базы текущей процедуры, границы, первого операнда и второго операнда и к выходу первого пышною формирователя, второй информационный входвыход блока обработки адресов памяти подкшочен к информационным входам решстров тега базы, тега традиция и к выходам второю шинного формирователя и элемента сравнения, второй информационный выход блока подтогпочен к информационному выходу сумматора, к первому штформационному входу элемента сравнения и к информационному входу регистра адреса,первъпй информационный выход блока подключен к выходу регистра базы текущей процедурьт и к первому штформационному входу мультиплексора, выходы узла микропрограммною управления подключены ко входам записи/считывания регистра базы текущей процедуры, регистра тега базы, регистра границы, регистра тега траницьт, регистров первою и второю операндов, регистра адреса и регистра сдвига, к управляющим входам сумматора, элемента сравнения, мультиплексора тегов, мультиплексора, первою и второю шинных формирователей, выход регистра тега базы подключен к первому информационному входу мультиплексора тегов, второй информационный вход которого подключен к выходу регистра тега границы, выход мультиплексора подключен к информационному входу первого шинного формирователя, выход регистра адреса подключен ко второму информационному входу мультиплексора,треттсй информационный вход когюрого подключен к вьпюду регистра границы и ко второму информационному входу элемента сравнения, выход мультиплексора тегов подключен к информационному входу второю шинного формирователя, выход регистра первою операнда подключен к первому информационному входу сумматора, второй информационный вход которого подключен квыходу регистра сдвша, ухнформационньпй вход которого соединен с выходом регистра второго операнда.3. Центральный процессор по п.1 отличающийся тем, что блок обработчик адресов ретистров содержит мультиплексор, сумматор и узел микропрограммного управления, причем первый и второй управляющие входы блока обработки адресов регистров подключены соответственно ко входам синхронизации сумматора и узла микропрограммного управления, третий управляющий вход блока обработки адресов подключен к первому управляющему входу мультиплексора, первый и второй информационные входы которого подключены соответственно к первому и второму информационным входам блока, Изобретение относится к области вычислительной техники и может быть использовано,например, для обработки данных ФИЗИЧВСШШ экспериментов, для решения задач автоматизированного управления в реальном масштабе времени И для научных расчетов,требующих высокой производительности и большого объема памяти.Известен процессор, содержащий первый и второй блоки сопряжения, первый и второй блоки регистров, блок коНТР 0 ЛЯ 5 ЛОК ПОСТОянной палтяти, блок обработки целых чисел,блок обработки вещественных чисел, блок постоянной памяти, блок логической обработки 1.Известный процессор построен на базе архитектуры с сокращенвъш набором команд,в котором болыштнство простых команд выполняется за один период следования СИНХРОимпульсов, при этом обеспечивается конвейерная обработка в большом числе параллельно работающих блоков обработках информации. Например, операции Над ЦЫГЫМИ И ВВЩССТЪЗННЪТМИ ЧИСЛНМИ МОГУТ ВЬШОЛНЯться одновременно в ДВУХ НВЗЭВИСИМО Работюьтхих блоках. Большинство команд данного процессора оперируют с данными , находящимися в блоке регистров, ЧТО УСКОРЯФТ ПРОцесс обработки и повышает быстродействие. Однако, в случае вьптолиения процедурных переходов, то естъ переходов на новые поцпрограммы, возникает необходИМ 00 ТЪ сохранения содержимого регистров в оперативной памяти, что требует допотшигельньтх временпых затрат. Кроме того, выполнение сложных операций, а таюке обработка исключитешньш операций, таких как преобразование форматов и типов, реализуются путем вьптолнения последовательности простых Команд, генерируемых компилятором в процессе трансляции программ. В частности, работа с динамикойинформационный выход которого подключен к информационному выходу сутушатора, первьпй информационный вход которою подключен к выходу мультиплексора, первый и второй выходы узла микропрограммного управления пошопоченьт, соответственно, ко второму управляющему входу Мультиплексора и ко второму штформатшонному входу сумматора.типов операндов требует дополнительных программных затрат. В этом случае, однако,увеличивается количество обращений в оперативную память, что приводит к снижению ПРОИЗВОДИТЕЛЬНОСТИ.Наиболее близким по технической сущности к предлагаемому устройству является процессор вычислительной системы 2,содержащий первый и второй блоки дешифРаЦИи команд, блок регистров, блок контроля, блок постоянной памяти, блок обработки целых чисел, блок обработки вещественных чисел, блок логической обработки,первый и второй тшформашаотптые входывыходы первого блока деипифрашш команд являются соответственно первым и вторым информационными входами-вьтходами процессора, штформатшонный вход и первьпй информационный выход второго блока децтифрации команд являются соответственно информационным входом и информационным выходом процессора, первый выход блока постоянной патияти является выходом признака готовности процессора, второй выход блока постоянной памяти и его адресный ВХОД ПОДКЛЮЧСНЫ СООТВБТСТВВННО К ПБРВЬЕМ И вторым информапионньтм входам-выходам второго блока девтифрацшт команд, второй информационный выход которого через информатшоннуто магистраль соединен с третьим информационным входом-выходом первого блока дешифрашш Команд, первым информационным входом-вьтходом блока обработки целых чисел, первым информационным входом блока регистров, с первым информационным входом-выходом блока обработки вещественных чисел и первым информационным входом-выходом блока логической обработки, выходы группы второю блока дешифрашдш команд через машстралгь управления ПОДКЛЮЧВНЬ К УПРЗВЛЯЮЩСМУвходу блока обработки целых чисел, ко входу записи/чтения блока регистров. к управляющим входам блоков обработки вещественных чисел, контроля, логической обработки и первого блока децгифрашш команд, четвертый информаштонньпй вход-вътход которою через магистраль контроля подключен ко вторым информационным входам-выходам блоков обработки целых чисел, обработки вещественных Чисел, логической обработки,к информационному входу-выходу блока регистров и к информационному входу блока контроля, выход которого подключен ко входу считывания блока постоянной памяти и управляющему входу второю блока дешифрации команд. В этом процессоре большинство исключительных ситуаций, а также случаи работы с динамикой типов и форматов обрабатываются без прерывания процессора и выхода на процедуры операционной систсшя. Выполнение операций ведется с использованием конвейера в блоках обработтощВозможно одновременное выполнение операций над цельтми и вещественными числами. Формирование адресов в командах обращения в память производится в блоке обработки целых чисел, а сформированный адрес передается в первый блок детштфрации команд. Это, однако, снижает производительность, поскольку невозможно параллельное вьптолнение команды обработки Целых чисел и обращений в память. Кроме того, недостатком данного процессора является необходимость сохранения и восстановления содержимого регистров, требующих большого числа обращений В память.Технической задачей изобретения является повышение производитезгьности за счет расттараллештвания выподтнения операций и сокращения числа обращений в память.Достигается это тем, что в процессор, содержащий первый и второй блоки децшфратгии команд, блок регистров, блок контроля, блок постоянной памяти, блок обработки целых чисел, блок обработки вещественных чисел,блок логической обработки и первый и второй штформатгионтгьте входы-выходы первого блока дешифрации команд являются соответственно первым и вторым информационньтми входами-вьтходами процессора,информационный вход и первый информационный выход второго блока дешифрации команд являются соответственно информационным входом и тшформатшонньш выходом процессора, первый выход блока постоянной памяти является выходом признака готовности процессора, второй выход блока постоянной памяти и его адресньп Вход Подключены, соответственно, к первым и вторым информационным входам-вьпкодамвторого блока дешифрацтш команд, второй информационный выход которою через информационную магистраль соединен с третьим информационньтм входом-выходом первого блока децптфрации команд, первьш информационным входом-выходом блока обработки целых чисел, первым информационным входом блока регистров, первым информационным входом-вьтходом блока обработки вещественных чисел и первым информашюнньтм входом-выходом блока логической обработки, выходы группы второго блока дешифрации команд через магистраль управления подключены к управляющему входу блока обработки целых чисел, ко входу записи/чтения блока регистров, к управляющим входам блоков обработки вещественных чисел, контроля, логической обработки и первого блока дешифрации команд, четвертый штформационньпй вход-выход которого через магистраль контроля подключен ко второму информационному входу-выходу блоков обработки целых чисел, обработки вещественных чисел, логической обработки и информаштонному входу блока контроля, выход которого подключен ко входу считывают блока постоянной памяти и управляющему входу второго блока детшгтфратши команд,введены блок обработки адресов памяти и блок обработки адресов памяти и блок обработки адресов регистров, причем информационный выход блока обработки адресов регистров подключен ко входу выборки блока регистров, управляютшае входы и первый информационный вход блока обработки адресов регистров подключен к выходам грутптьт второго блока депшфратлш команд и входу блока контроля, первый штформатлтонньтй выход блока обработки адресов памяти подключен ко второму информационному входу блока обработки адресов регистров, второй Информационный выход блока обработки адресов памяти подключен к информационному входу первого блока дештфрштии команд,первый информационный вход-вьтход блока обработки адресов памяти через информационную магистраль подключен ко второму информационному выходу второго блока депшфрации команд, к третьему информшшонному входу-выходу первого блока леглиФРаЦии команд, к информационному входу блока регистров и к первым информационньш, входам-выходам блока обработки вещественных чисел, блока обработки Целых чисел и блока логической обработки, второй информационный вход-выход контроля подключен к четвертому информационному входу-выходу первого блока дешифраШШ КОманд, к информационному входу-выходу блока регистров, к информационному входуным входам-выходам блока обработтш Целых чисел, блока вещественных чисел и блока логической обработки, управляющие входы блока обработки адресов памяти подключены к выходам грутптьт второго блока дептифрашш команд.А также тем, что блок обработки адресов памяти содержит регистр базы текущей процедурьт, регистр тега базы, регистр границы,регистр тега границы, регистры первою и второго операндов, регистр сдвига, сутчтматор,элемент сравнения, узел микропрограммного управления, мультиплексор тегов, регистр адреса, мультиплексор, первый и второй шинные формироватешит, причем первый информашитонньпй вход-вьтход блока обработки адресов памяти подклюнен к информационным входам регистров базьт текущей процедуры, гратпщьт, первого операнда и второю операнда и к выходу первою шинного формирователя, второй Информационный входвьтход блока обработки адресов памяти подкшочен к информационным входам регистров тега базы, тега траниъш и к выходам второю цшнного формирователя и элемента сравнения, вюрой информационный выход блока подкшочен к информационному выходу сумматора, к первому информационному входу элемента сравнения и к информационному входу регистра адреса,первый информационный выход блока подключен к выходу регистра бшы текущей процедуры и к первому информационному входу мулътитшексора, выходы узла микропрограммного управления подключены ко входам записи/считывания регистра базы текущей процедуры, регистра тега базы, регистра град ницы, регистра тега границьт регистров первою и второю операндов, регистра адреса и регистра сдвига, к управляющим входам сумматора, элемента сравнения, мультиплексора тегов, мультиплексора, первою и второю шинных формирователей, выход регистра тега базы подключен к первому информационному входу мультиплексора тегов, второй информационный вход которою подключен к выходу регистра тега границы, выход мультиплексора подюпочен к информационному входу первого тштнттото формирователя, выход регистра адреса подключен ко второмутретий информационный вход которого подключен к выходу регистра границы и ко второму информационному входу элемента сравнения, выход мультиплексора теюв подтопочен к информационному входу второю шинного формирователя, выход регистра первою операнда подключен к первому информационному входу сумматора, второй ин 10форменного-льна вход которою подключен к ВЪШОДУ РВГИСТРЗ сдвша, информационный вход которого соединен с выходом регистра вюрою операнда.А также тем, что блок обработки адресов регистров содержит мультиплексор, сут/шатор, узел микропрограммною управления,причем первый и второй управляющие входы блока обработки адресов регистров подкшочены соответственно ко входам синхрот-шэации сумматора и узла микропрограммного сумматора и управления, треп/п управляющий вход блока обработки адресов регистров подключен к первому управляющему входу мультиплексора, первый и второй информационные входы которого подкшочены соответственно к информационным входам блока,информационный выход которою подключен к информационному выходу сумматора, первый информационный вход которою подключен к выходу мультиплексора, первьпа и второй выходы узла микропрограммного управления подключены, соответственно, ко второму управляющему входу мультиплексора и ко второму информационному входу сумматора.Технических решений с совокупностью признаков, сходной с совокупностью отличительных признаков обьекта изобретения не имеется.Сущность изобретения заключается в том,что введение новых блоков, а также наличие дополнительной связи между блоком обработтси адресов памяти и первым блоком сопряжения реализует адресную арифметику в блоке обработки адресов памяти и позволяет организовать работу с регистрами как с аппаратным буфером стека процедур, что разрешает конфликт по ресурсам между командами обработки целых чисел и командами/т обращения в память и допускает их совместное выполнение, а также сокращает число обратцений в память для сохранения и восстановления содержимого регистров, что и приводит к достижению поставленной цели, а именно, к повышению производительности.Сравнение заявляемого технического решения с прототипом позвошитло установить соответствие его критерию новизна. При изучении других технических решений в данной области техники признаки, оггличатотште заявляемое изобретение от прототипа, не быдш выявлены и потому они обеспечивают заявляемому техническому решению соответствие критерию изобретательский уровонь. Испытания макетного образца предложенного устройства показатш возможность ею промышленною использования.заявляемое устройство представлено следуторшми чертежами на фит.1 представлена

МПК / Метки

МПК: G06F 15/16, G06F 15/00

Метки: процессор, центральный, системы, вычислительной, многопроцессорной

Код ссылки

<a href="https://by.patents.su/10-1192-centralnyjj-processor-dlya-mnogoprocessornojj-vychislitelnojj-sistemy.html" rel="bookmark" title="База патентов Беларуси">Центральный процессор для многопроцессорной вычислительной системы</a>

Предыдущий патент: Устройство управления буферной памятью

Следующий патент: Способ получения производного [3Н]-имидазо-[5,1-а]-1,2,3,5-тетразин-4-она

Случайный патент: Ручное приспособление для уборки плодов и ягод