Урбанович Павел Павлович

Запоминающее устройство

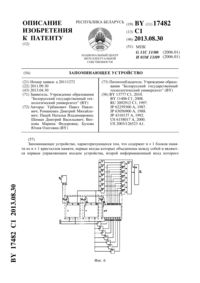

Номер патента: 17482

Опубликовано: 30.08.2013

Авторы: Булова Юлия Олеговна, Пацей Наталья Владимировна, Урбанович Павел Павлович, Шиман Дмитрий Васильевич, Виткова Марина Федоровна, Романенко Дмитрий Михайлович

МПК: G11C 11/00, H03M 13/09

Метки: устройство, запоминающее

Текст:

...- третьи паритеты), 60 - вторые паритеты между плоскостями(со сдвигом по горизонтали)(81-96) (в формуле изобретения - шестые паритеты), 61 третьи паритеты между плоскостями (со сдвигом по вертикали)(97-112) (в формуле изобретения - седьмые паритеты). Фиг. 3 - фрагмент порождающей матрицы трехмерного итеративного кода с семью линейно-независимыми паритетами, отображающий принцип формирования горизонтальных и вертикальных паритетов (на...

Устройство для кодирования кодов низкой плотности проверок на четность с переменной скоростью и длиной блока

Номер патента: 16168

Опубликовано: 30.08.2012

Авторы: Шиман Дмитрий Васильевич, Пацей Наталья Владимировна, Романенко Дмитрий Михайлович, Урбанович Павел Павлович

МПК: H03M 13/11, H04L 1/00

Метки: переменной, четность, длиной, скоростью, устройство, кодирования, проверок, низкой, блока, кодов, плотности

Текст:

...параметров ИСПОЛЬЗУСМЫХ КО ДОВ.Широко распространенными на сегодняшний день в системах беспро 3водной передачи являются турбокодь 1 И коды низкой плотности проверок на четность. В силу того, что декодер для НППЧ использует основанный на алгоритме суммы-произведения итерационный алгоритм декодирования, ОН ЯВЛЯСТСЯ МСНОС СЛОЖНЫМ, ЧСМ декодер ТУрОО-КОДЗ И ИМССТ ПрОСТуЮ РОЗЛИ зацию.Код с низкой плотностью проверок на четность относится к...

Устройство перемежения/обратного перемежения для системы связи

Номер патента: 16167

Опубликовано: 30.08.2012

Авторы: Чуриков Константин Валерьевич, Пацей Наталья Владимировна, Горбунова Юлия Олеговна, Шиман Дмитрий Васильевич, Романенко Дмитрий Михайлович, Урбанович Павел Павлович

МПК: H04L 1/00, H03M 13/27

Метки: перемежения, связи, системы, устройство

Текст:

...Известный способ и устройство перемежения/обратного перемежения характеризуется постоянной глубиной перемежения, что позволяет легко исправить группирующиеся ошибки (пакет) определенной кратности. Однако известно, что кратность ошибки может быть различной. Причем при передаче данных достаточно большой длительности и объема (минуты и более мегабайты и более) могут встречаться пакеты ошибок разной длины. Вместе с тем на практике вероятность...

Устройство перемежения/обратного перемежения для системы связи

Номер патента: U 8292

Опубликовано: 30.06.2012

Авторы: Булова Юлия Олеговна, Урбанович Павел Павлович, Романенко Дмитрий Михайлович, Пацей Наталья Владимировна, Шиман Дмитрий Васильевич

МПК: H03M 13/27

Метки: связи, перемежения, системы, устройство

Текст:

...управляющих сигналов. Изобретение поясняется чертежами фиг. 1 - схема устройства перемежения/обратного перемежения фиг. 2 - принцип перестановки строк матрицы данных фиг. 3 - блок-схема работы блока анализа. Процессор (на фиг. 1 не показан) связан с памятью и используется для разделения пакетов данных на части. Он также предназначен для генерации перемежения последовательного множества частей данных и индексации символов. На фиг. 1...

Адаптивное устройство кодирования/декодирования данных на основе кодов низкой плотности проверок на четность

Номер патента: U 8296

Опубликовано: 30.06.2012

Авторы: Романенко Дмитрий Михайлович, Шиман Дмитрий Васильевич, Урбанович Павел Павлович, Пацей Наталья Владимировна

МПК: H03M 13/11, H04L 1/00

Метки: плотности, основе, четность, устройство, данных, низкой, адаптивное, кодов, проверок

Текст:

...передачи будет медленно адаптируемая, поэтому в данном техническом решении период измерения будет зависеть от числа переданных бит. Анализатор выполняет деление качества канала на шесть категорий и от 10 до 14 подкатегорий в каждой категории на основании . Категории/подкатегории качества канала представлены в табл. 1. В зависимости от категории/подкатегории и текущих параметров кода (, , , ) блок анализа 20 выполняет переключение ПНППЧ-кода...

Устройство обмена конфиденциальной информацией на основе нейросетевых технологий

Номер патента: U 7114

Опубликовано: 30.04.2011

Авторы: Чуриков Константин Валерьевич, Урбанович Павел Павлович, Плонковски Мартин Даниел

МПК: H04L 9/00

Метки: основе, устройство, технологий, обмена, нейросетевых, конфиденциальной, информацией

Текст:

...между соответствующими величинами векторов весов. Для двух персептронов с -мерными векторами весов существуетдвухэлементных групп (пар величин), которые движутся в промежутке -, . Опыты показывают, что для набора параметров 100 и 3 две сети ( и ) синхронизируют свои внутренние векторы весов приблизительно за 100 шагов обучения. Вдобавок время синхронизации логарифмически увеличивается с ростом величины . Нужно также добавить, что...

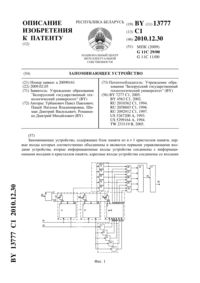

Запоминающее устройство

Номер патента: 13777

Опубликовано: 30.12.2010

Авторы: Пацей Наталья Владимировна, Романенко Дмитрий Михайлович, Шиман Дмитрий Васильевич, Урбанович Павел Павлович

МПК: G11C 29/00, G11C 11/00

Метки: запоминающее, устройство

Текст:

...диагональными проверками (16). Сущность метода заключается в том, что система памяти состоит из 1 кристаллов, из которых имеют внутренние схемы дешифрации адреса, а (1)-й кристалл является устройством для хранения паритетов строк и столбцов (, ), первых и вторых объединенных диагональных паритетов (1 и 2), а также паритета контрольной суммы . Из этого следует, что вычисление проверочных символов осуществляется в четырех направлениях (, ,...

Запоминающее устройство

Номер патента: 11406

Опубликовано: 30.12.2008

Авторы: Пацей Наталья Владимировна, Урбанович Павел Павлович, Романенко Дмитрий Михайлович, Шиман Дмитрий Васильевич

МПК: G11C 11/00, H03M 13/00

Метки: запоминающее, устройство

Текст:

...вычисления первых, вторых диагональных паритетов и контрольной суммы соединены с третьей, четвертой и пятой группой информационных входов (и 1)-го кристалла памяти. Изобретение поясняется чертежами фиг. 1 - фиг. 3. Фиг. 1 - Порождающая матрица линейного итеративного кода с двойными диагональными проверками (16). Фиг. 2 - Принцип формирования избыточных символов для линейного итеративного с двойными диагональными проверками (16), где 1 -...

Устройство перемежения/обратного перемежения для системы связи

Номер патента: 11268

Опубликовано: 30.10.2008

Авторы: Урбанович Павел Павлович, Романенко Дмитрий Михайлович, Шиман Дмитрий Васильевич, Пацей Наталья Владимировна

МПК: H03M 13/00

Метки: системы, перемежения, устройство, связи

Текст:

...размеров строк (1) и столбцов (2) соответствует объему блока данных (12). Перемежение данных базируется на алгоритме разбрасывания данных за счет обработки бит по частям. Блок перемежения содержит память, предназначенную для обработки и хранения пакетов данных. Он построен и функционирует по тому же принципу, что и блок перемежения известного устройства 3. Изобретение поясняется чертежами фиг. 1 - схема устройства перемежения/обратного...

Запоминающее устройство

Номер патента: 7277

Опубликовано: 30.09.2005

Авторы: Романенко Дмитрий Михайлович, Урбанович Павел Павлович

МПК: G11C 29/00, G11C 11/00

Метки: запоминающее, устройство

Текст:

...-паритета связаны со вторыми информационными входами устройства, выходы второго блока вычисления -паритета соединены с третьей группой информационных входов (1)-го кристалла памяти. Сущность метода заключается в том, что система памяти состоит из 1 кристаллов, из которых имеют внутренние схемы дешифрации адреса и формирования паритетов строк и столбцов (, ), а (1)-ый кристалл является устройством для хранения вертикального паритета ....

Устройство криптографического преобразования информации с обнаружением и коррекцией ошибок

Номер патента: 5121

Опубликовано: 30.06.2003

Авторы: Пацей Наталья Владимировна, Урбанович Павел Павлович

МПК: H04K 01/00, H04L 09/00

Метки: преобразования, ошибок, криптографического, информации, обнаружением, коррекцией, устройство

Текст:

...выполнения основных арифметических и логических операций алгоритма при помощи методов контроля, основанных на свойствах сравнений (контроля по модулю) 4. Предлагаемое устройство криптографического преобразования (фиг. 1) содержит КЗУ на 256 бит, состоящее из восьми 32-разрядных накопителей 1 и соответствующих им восьми -разрядных дополнительных накопителей 2 (количество разрядов в дополнительных накопителях определяется мощностью...

Устройство крипто-корректирующего преобразования информации

Номер патента: 4997

Опубликовано: 30.03.2003

Авторы: Пацей Наталья Владимировна, Урбанович Павел Павлович

МПК: H04L 9/00, G06F 11/08

Метки: информации, устройство, преобразования, крипто-корректирующего

Текст:

...по выходу 40 подается на выход 6 до начала поступления бинарного кода 6. Блок помехоустойчивого кодирования 7 может быть реализован на основе сверточных кодов. На фиг. 3 для примера приведена схема блока 7 на основе сверточного кода (9,6),исправляющего одиночные ошибки с порождающей матрицей, представленной в виде многочленов 7 542. Блок 7 содержит последовательно-параллельный регистр 41 размером 2 бита с выходами 42 и 43, первый...

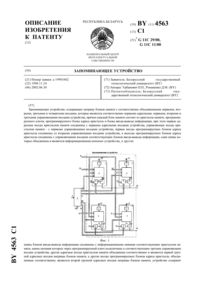

Запоминающее устройство

Номер патента: 4563

Опубликовано: 30.06.2002

Авторы: Романенко Дмитрий Михайлович, Урбанович Павел Павлович

МПК: G11C 29/00, G11C 11/00

Метки: запоминающее, устройство

Текст:

...и назначение шин 8 и 9 будет рассмотрено ниже на конкретном примере). В соответствии с кодом адреса на шинах 9 формируется новый (внутренний) код адреса 10, 11, соответствующий адресу годного поднакопителя (часть накопителя) кристаллов 4 и адресу кристалла, имеющего годные накопители. Блок внешней памяти 2 может представлять собой программируемое или оперативное ЗУ. В первом случае входы 15 являются управляющими для программирования, во...

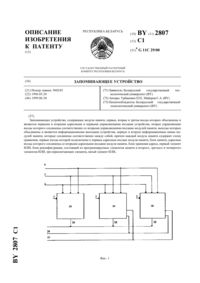

Запоминающее устройство

Номер патента: 2807

Опубликовано: 30.06.1999

Авторы: Майоров Сергей Александрович, Урбанович Павел Павлович

МПК: G11C 29/00

Метки: запоминающее, устройство

Текст:

...выходу блока реконфигурации, соединенному с первым выходом программируемых элементов памяти, а переключающие элементы выполнены в виде транзисторных ключей. Сущность изобретения заключается в том, что на входах мажоритарнго элемента, входами соединенного с триадой блоков памяти (бездефектных или содержащих дефектные элементы памяти по разным, не совпадающим адресам), всегда два считанных символа из трех будут верными. При этом, если...