Запоминающее устройство

Номер патента: 4563

Опубликовано: 30.06.2002

Авторы: Романенко Дмитрий Михайлович, Урбанович Павел Павлович

Текст

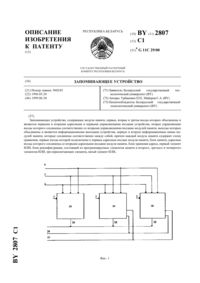

(71) Заявитель Белорусский государственный технологический университет(73) Патентообладатель Белорусский государственный технологический университет(57) Запоминающее устройство, содержащее матрицу блоков памяти с соответственно объединенными первыми, вторыми, третьими и четвертыми входами, которые являются соответственно первыми адресными, первыми, вторыми и третьими управляющими входами устройства, причем каждый блок памяти состоит из кристалла памяти, программируемого ключа, программируемого блока адреса кристалла и блока ввода-вывода информации, при этом первые адресные входы кристаллов памяти соединены с первыми адресными входами устройства, управляющие входы кристаллов памяти - с первыми управляющими входами устройства, первые входы программируемых блоков адреса кристалла соединены со вторыми управляющими входами устройства, а выходы программируемых блоков адреса кристалла соединены с управляющими входами соответствующих блоков ввода-вывода информации, одни шины которых объединены и являются информационными шинами устройства, а другие Фиг. 1 шины блоков ввода-вывода информации соединены с информационными шинами соответствующих кристаллов памяти, шины питания которых через программируемый ключ подключены к соответствующим третьим управляющим входам устройства, другие адресные входы кристаллов памяти объединены соответственно и являются первой группой адресных входов матрицы блоков памяти, а другие входы программируемых блоков адреса кристалла, объединенные соответственно, являются второй группой адресных входов матрицы блоков памяти, устройство содержит 4563 1 также вторые адресные и четвертые управляющие входы, отличающееся тем, что включает блок внешней памяти,первая и вторая группы выходов которого соединены соответственно с первой группой и второй группой адресных входов матрицы блоков памяти, а адресные и управляющие входы блока внешней памяти связаны соответственно со вторыми адресными и четвертыми управляющими входами устройства.(56) Экспресс-информация. Сер. Вычислительная техника. - 1981. -28. - С. 7-11.03150798 А, 1991.05198198 , 1993.02294999 , 1990.5303192 , 1994.95120832 , 1997.94009963 1, 1996. Изобретение относится к вычислительной технике и может быть использовано при производстве СБИС запоминающих устройств (ЗУ) высокой информационной емкости, а также при создании ЗУ на целой полупроводниковой пластине. Известно запоминающее устройство, содержащее элементы памяти, схемы логики обрамления, позволяющие производить обращение при записи и считывании информации только к одному элементу памяти матрицы и осуществлять коррекцию сигналов с дефектных элементов памяти 1. Недостатками этого запоминающего устройства являются невысокие надежность и быстродействие из-за сложности блоков контроля, большой задержки сигналов в них, введения большого числа разрядных элементов памяти. Другим из известных устройств является система памяти, содержащая устройства памяти, первые и вторые адресные входы, управляющие входы, выход системы, соединенный с первыми выходами устройств,причем первые адресные и управляющие входы системы соединены с первыми и вторыми входами запоминающих блоков в каждом устройстве. Эта система позволяет производить коррекцию как отдельных дефектных элементов памяти, слов, разрядов в запоминающих блоках, так и замену дефектных блоков на исправные 2. Однако известная система характеризуется большой избыточностью и не позволяет использовать для хранения информации отдельные дефектные блоки, что уменьшает эффективно используемую емкость памяти. Наиболее близким техническим решением к предлагаемому изобретению является запоминающее устройство 3,содержащее блок памяти, первые и вторые входы которых соответственно объединены и являются одним из адресных и управляющим входами устройства, блоки выборки информации (программируемые блоки адреса кристалла),блоки реконфигурации памяти, группы элементов И с первого по пятый, мажоритарные элементы, группы элементов ИЛИ, причем входы блоков выборки информации являются другим адресным входом устройства, выходы блоков выборки информации соединены с первыми входами первых элементов ИЛИ групп, вторые входы которых и входы соответствующих блоков реконфигурации памяти являются контрольными входами устройства, первые входы элементов И каждой группы подключены к выходам одноименного блока реконфигурации памяти, вторые входы элементов И каждой группы с первого по четвертый подключены к выходу одноименного блока памяти, второй вход пятого элемента И каждой группы соединен с выходом второго элемента ИЛИ одноименной группы, входы которого соединены с выходами первого элемента одноименной группы одноименного мажоритарного элемента, первый, второй и третий входы которого соединены соответственно с выходами второго, третьего и четвертого элементов И одноименной группы, выход первого элемента ИЛИ каждой группы соединен с третьим входом одноименного блока памяти и третьими входами третьего, четвертого и пятого элементов И одноименной группы, выходы пятых элементов И групп являются выходом устройства, выходы третьих и четвертых элементов И групп соответственно объединены, кроме того, каждый блок выборки информации содержит первую группу элементов памяти и блок сравнения, одни из входов которого являются входами блока, а другие соединены с выходами элементов памяти первой группы, причем выход блока сравнения является выходом блока, а также каждый блок реконфигурации памяти содержит вторую группу элементов памяти и элементов ИЛИ, причем первые входы элементов ИЛИ с первого по четвертый являются входом блока, вторые входы соединены с выходами элементов памяти второй группы, выходы первого и второго элементов ИЛИ соединены с выходами пятого элемента ИЛИ, выходы элементов ИЛИ являются выходами блока. В этом устройстве блоки (кристаллы) памяти, имеющие дефектные элементы памяти (ЭП) накопителя (по данным адресам), объединяются в триады мажоритарным элементам и представляют собой по существу отдельный блок памяти. Это позволяет использовать частично годные накопители, что повышает общую эффективную емкость ЗУ. Однако такое объединение не может считаться эффективным, если блоки памяти имеют единичные дефекты накопителей. В наиболее простом и часто встречающемся случае накопитель может иметь лишь один неработоспособный ЭП. Объединение воедино трех таких блоков, особенно большой потенциальной информационной емкости, не может считаться оптимальным и снижает эффективную емкость ЗУ. Задачей изобретения является повышение эффективной емкости запоминающего устройства. 4563 1 Поставленная задача решается тем, что в запоминающее устройство, содержащее матрицу блоков памяти с соответственно объединенными первыми, вторыми, третьими и четвертыми входами, которые являются соответственно первыми адресными, первыми, и вторыми и третьими управляющими входами устройства, причем каждый блок памяти состоит из кристалла памяти, программируемого ключа, программируемого блока адреса кристалла и блока ввода/вывода информации, при этом первые адресные входы кристаллов памяти соединены с первыми адресными входами устройства, управляющие входы кристаллов - с первыми управляющими входами устройства,первые входы программируемых блоков адреса кристалла соединены с вторыми управляющими входами устройства, а выходы программируемых блоков адреса кристалла соединены с управляющими входами соответствующих блоков ввода-вывода информации, одни шины которых объединены и являются информационными шинами устройства, а другие шины блоков ввода-вывода информации соединены с информационными шинами соответствующих кристаллов памяти, шины питания которых через программируемый ключ подключены к соответствующим третьим управляющим входам устройства, другие адресные входы кристаллов памяти объединены соответственно и являются первой группой адресных входов матрицы блоков памяти, а другие входы программируемых блоков адреса кристалла, объединенные соответственно, являются другой группой адресных входов матрицы блоков памяти, устройство содержит также вторые адресные и четвертые управляющие входы, отличающееся тем, что включает блок внешней памяти, первая и вторая группы выходов которого соединены соответственно с первой группой и второй группой адресных входов матрицы блоков памяти, а адресные и управляющие входы блока внешней памяти связаны соответственно со вторыми адресными и четвертыми управляющими входами устройства. Сущность изобретения заключается в том, что накопитель каждого кристалла памяти условно разбивается на поднакопители, число которых кратно степени двойки (размер такого поднакопителя определяется дефектностью кристалла при малом числе дефектов целесообразно уменьшить размер поднакопителя), и дефектные накопители,адрес которых запоминается, из обращения исключаются. Общая емкость ЗУ набирается из числа годных поднакопителей вне зависимости от того, в каком кристалле данной группы блоков памяти этот поднакопитель расположен. ЗУ (фиг. 1) содержитгрупп блоков (матрицу) памяти 1, блок внешней памяти 2. Каждый блок 3 памяти состоит из кристалла памяти 4, программируемого блока 5 адреса кристалла, блока 6 ввода/вывода информации,программируемого ключа 7. Устройство содержит также первые адресные входы 8, соединенные с соответствующими адресными входами кристаллов памяти, вторые адресные входы 9, соединенные с адресными входами блока 2, первую группу 10 адресных входов блоков памяти 1, являющихся другими адресными входами кристаллов памяти 4 и соединенных соответственно с выходами первой группы блока 2, выходы 11 второй группы которого подключены соответственно ко вторым входам блоков 5 соответствующей группы блоков 3 (соответствующей строки матрицы блоков 3), первые входы 12 которых соединены с другими управляющими входами устройства,третьи 13 входы которого подключены к входам программирования ключей 7. Кроме того, устройство содержит информационные входы/выходы 14 (количество их равно числу групп(строк)блоков 3 при одноразрядных кристаллах памяти 4), входы 15 программирования блока 2, соединенные с четвертыми управляющими входами устройства, первые 16 входы которого связаны с управляющими входами кристаллов памяти 4, выходы 17 блоков 5, соединенные соответственно с управляющими входами блоков 6, другие информационные шины 18 которого соединены с информационными шинами соответствующих кристаллов памяти 4. На фиг. 2 показан вариант построения программируемого ключа 7. Группы блоков памяти 3 врядов(строк) поштук в каждом формируются на полупроводниковой пластине. Кристалл памяти 4 представляет собой стандартную БИС ОЗУ (блок ввода/вывода информации показан отдельно, 6). Блоки 3 с соответствующими информационными, адресными и управляющими шинами формируются одновременно в едином технологическом цикле. На управляющие входы 16 подаются стандартные сигналы (разрешение записи/чтения) для соответствующего типа памяти. На адресные входы 8 и 9 устройства подается под адреса опрашиваемого ЭП (соответственно младшие и старшие разряды количество и назначение шин 8 и 9 будет рассмотрено ниже на конкретном примере). В соответствии с кодом адреса на шинах 9 формируется новый (внутренний) код адреса 10, 11, соответствующий адресу годного поднакопителя (часть накопителя) кристаллов 4 и адресу кристалла, имеющего годные накопители. Блок внешней памяти 2 может представлять собой программируемое или оперативное ЗУ. В первом случае входы 15 являются управляющими для программирования, во втором -управляющими, задающими режим работы (запись/чтение). Программируемый блок 5 имеет то же функциональное назначение, что и блок памяти 2. Блок 6 ввода/вывода стандартный, стробируется единичным сигналом на шине 17. При нулевом сигнале на шине 17 входы/выходы соответствующего блока 6 имеют третье состояние. Программирование осуществляется общеизвестными методами (п. 3.5 из 4). Поскольку в накопителе блока 4 могут быть дефектные (отказавшие) ЭП, то все поле накопителя блока 4 условно разбивается на поднакопители, информационная емкость которых составляет 1/2, 1/4, 1/16 и т.д. общей информационной емкости накопителя блока 4. Это делается с целью исключения из обращения поднакопителей с дефектными ЭП. Таким образом, полный адрес ЭП разделяется на адрес 11 кристалла 4 (Ак),3 4563 1 адрес 10 поднакопителя в кристалле (Ап) и адрес 8 ЭП в поднакопителе. Если информационная емкость одного кристалла 4 (количество ЭП) составляет(каждый накопитель разбивается на(блоков поднакопителей) и количество кристаллов в линии , то условие на разрядность кода адреса (количество адресных входов) будет следующим разрядность адреса Ак - 2, разрядность адреса А - 2, разрядность адреса ЭП 2-22(/). Так как в блоке 2 запоминается адрес (в процессе функционального контроля каждого кристалла 4) годных кристаллов 4 и поднакопителей в них, то необходимая разрядность блока 2 для одной линии равна, а общая разрядность блока 2 составит 2 разрядов. Полное число блоков 3 в линии есть. Это число определяет максимальную требуемую емкость блока памяти 2 (это максимальное количество слов разрядностью 2, которые нужно занести в блок памяти 2). Практически же это число меньше,т.е. имеются дефектные блоки 4, адреса которых запоминать не надо. Полная реальная емкость системы определяется как произведение 1, где 1 - минимальное количество(кратное 2) годных блоков в линии,- количество линий. Избыточные блоки, имеющиеся в некоторых линиях, могут использоваться как резервные. Работа устройства включает в себя 3 этапа, которые условно назовем следующим образом- настройка,- тестирование,- эксплуатация. Настройка. Этот этап относится только к матрице . При этом производится поочередное тестирование каждого блока 3, а также программирование блоков адреса кристалла 5 и ключей 7. В исходном состоянии все блоки 5 настроены на какой-либо адрес (например, 111), т.е. при подаче на адресные входы 11 (для этого должны быть предусмотрены соответствующие контактные площадки) указанного адреса на выходе 17 блока 5 появляется сигнал, разрешающий работу блока 6 ввода/вывода. Программируемый ключ 7 в исходном состоянии разрывает цепь питания для соответствующего кристалла 4 и подключает питание только при подаче на управляющий вход 13 сигнала лог. 0. Таким образом, в начальный момент времени на управляющий вход 13 тестируемого кристалла 4 подается сигнал лог. 1, который включает цепь питания для этого кристалла, а на входы 11 - исходный разрешающий адрес (например, как отмечалось, 111), что обеспечивает подключение тестируемого кристалла к магистрали данных 14. После этого известными методами производится тестирование накопителя кристалла 4 с помощью адресных входов 8 и 10 и шины данных 14. Все остальные кристаллы в линии при этом отключены, т.к. на управляющих входах 13 у них отсутствует сигнал лог. 1. По результатам тестирования принимается решение если в накопителе кристалла 4 отсутствуют бездефектные накопители (кристалл полностью неработоспособен), то все управляющие напряжения снимаются следует перейти к тестированию следующего кристалла. Неработоспособные кристаллы в таком случае оказываются отключеными или от линии питания. При обнаружении хотя бы одного годного поднакопителя в накопителе кристалла 4 производится программирование блоков 5 и 7. Для этого на адресных входах 11 устанавливается начальный адрес 000, а на программирующий вход 12 подаются программирующие импульсы. После этого подаются программирующие импульсы на вход 13, осуществляя тем самым программирование ключа 7 и обеспечивая постоянное подключение питания к указанному кристаллу. Таким образом, этот кристалл 4 оказывается постоянно подключен к шине питания и настроен на адрес 000, т.е. обращение к нему возможно при появлении на адресных входах 11 000. Далее вся процедура повторяется для следующего кристалла, с той лишь разницей, что в блок 5 будет заноситься следующий адрес 00 1 и т.д., пока не будут протестированы и настроены все кристаллы в линии. В других линиях процедура тестирования повторяется, опять начиная с адреса Ак (000).этап - тестирование. На этом этапе производится тестирование блоков 3 в линии с помощью адресных входов 8,10, 11 определение адресов годных поднакопителей в накопителях и запись адресов кристаллов и годных блоков в кристаллах - в блок внешней памяти 2. Например, пусть в накопителе имеется один дефект. Тогда этот дефект выводит из строя один блок накопителя при размере блока 1/2 общей емкости используемая емкость также составляет 1/2 от общей, при размере блока 1/4 - используемая емкость 3/4 и т.д. С другой стороны, чем больше блоков в системе, тем больший объем внешнего ЗУ требуется для запоминания адресов. Таким образом, размер блока сверху ограничен емкостью накопителя 4 и плотностью дефектов, а снизу - объемом внешнего ЗУ 2. Тестирование производится с помощью стандартного измерительного оборудования (на фиг. не показано 4, с. 31) и по завершению тестирования в памяти этой установки хранятся адреса годных кристаллов 4 и поднакопителей в них (отдельно для каждой линии). После этого с помощью этой же установки приступают к программированию блока памяти 2. Для этого на адресных входах 9 блока 2 выставляется начальный адрес (000) и с помощью управляющих сигналов 15 по этому адресу записывается номер первого годного кристалла 4 и первого годного накопителя для каждой линии. Затем на входах 9 устанавливается следующий адрес (001) и записываются адреса следующих годных блоков и т.п. Процесс продолжается до тех пор, пока не будет набрана требуемая информационная емкость системы или пока не закончатся годные блоки 4 в какой-либо из линий. Пусть, например, есть матрица их двух линий по 4 кристалла в каждой кристаллы емкостью 1 Мбит набор осуществляется по 256 Кбит, т.е.2,4,1,4. Количество разрядов, определяющих адрес кристалла , равно 2 (, 1) определяющих адрес поднакопителя-также 2 (18 п, 19 п) и адрес ЭП в поднакопителе 18 (Ао 17). Пусть в результате тестирования на этапе настройки определено, что первый кристалл первой линии 4 4563 1 и четвертый кристалл второй линии не имеет годных поднакопителей. Тогда эти кристаллы не подключаются к линии питания. Остальные кристаллы подключены к линии питания с помощью программируемого ключа 7 и настроены на соответствующие адреса кристаллов, как показано в табл. 1. Таблица 1 На втором этапе при тестировании определяются конкретные адреса годных кристаллов и поднакопителей (первый и второй этапы могут быть совмещены, но в общем случае второй этап - тестирование - может проводиться неоднократно с целью обнаружения и замены блоков, отказавших даже в процессе эксплуатации ЗУ, как это делается, например, в ПЭВМ). После тестирования в регистре тестирующей машины содержится информация о годных поднакопителях(табл. 2). То есть из табл. 2 видно, что в первой линии оказалось 8 годных поднакопителей (по 256 Кбит), а во второй - 9. Таким образом, имеется возможность собрать ЗУ емкостью 2 Мбит х 2 (2 Мбит 8 х 256 К). Для этого необходимо занести адреса восьми годных поднакопителей каждой линии в блок памяти 2. Поскольку необходимо запомнить адреса восьми поднакопителей, а адрес блока для каждой из 2 линий содержит 4 разряда (А), то необходимая организация блока 2 будет 8 бит х 8, т.е. необходимо осуществить перекодировку внешнего 3-х разрядного адреса (18, 19, А 20) во внутренний четырехразрядный (А, А) согласно табл. 3. Таблица 2 Адрес линия Результат тестирования 1-годен 0-брак 1 1 0 1 1 0 1 1 1 1 0 0 линия Результат тестирования 1 -годен 0-брак 0 1 1 1 1 0 1 1 1 1 1 0 Таблица 3 Таблица перекодировки заносится из регистра тестирующей машины в блок памяти 2. При этом 18, 19,А 20 являются адресами этого ЗУ, а значение ,- записываемой информацией. Если в качестве блокад используется ППЗУ, то операция перекодировки осуществляется изготовителем ЗУ и потребителю нет необходимости каждый раз перед работой производить тестирование. Если же в качестве блока 2 используется ОЗУ, то перед началом работы системы (после включения питания) необходимо производить тестирование ЗУ и занесение перекодировки адресов в соответствии с наличием годных поднакопителей в кристаллах 4. 5 4563 1 При этом появляется возможность обходить отказавшие поднакопители за счет резервных. В нашем примере резервный поднакопитель имеется во 2-ой линии. Его адрес А, А 1010. Поэтому если произойдет отказ,например, поднакопителя с адресом А, А 0001 во второй линии, то после очередного тестирования блок 2 ОЗУ вместо адреса ,0001 будет записан адрес ,1010 и система вновь станет работоспособной. Итак, второй этап заканчивается занесением таблицы перекодировки в блок памяти 2. После этого тестирующее устройство отключают и подключают блок 2 к матрице памяти 1, как это показано на фиг. 1.этап. Эксплуатация. На этом этапе система имеет вид, показанный на фиг. 1, и работает как обычное ЗУ большой емкости с первыми адресными входами 8, входами внешнего адреса блока 9 и входом/выходом информации 14. На адресный вход 9 подается внешний адрес блока, а на входы 8 - адрес ЭП в этом блоке. На входах первой и второй групп 10, 11 устанавливается адрес годного блока, записанный в ЗУ 2 по адресу 9. Производится выбор ЭП, в который можно записать (или считать) информацию по шине данных 14. Все линии работают одновременно и параллельно. Таким образом, предлагаемое ЗУ выполняет те же функции,что и известное. Однако преимущество предлагаемого устройства очевидно. Оно состоит в более эффективном использовании информационной емкости отдельных кристаллов памяти 4. Возьмем для примера типичный случай в нескольких кристаллах по разным адресам в одном из четырех поднакопителей каждого кристалла имеются дефектные ЭП. Объединение трех кристаллов в один мажоритарным элементом в известном устройстве позволяет получить эффективную емкость, равную емкости одного кристалла, а в предлагаемом ЗУ эффективная информационная емкость трех отмеченных кристаллов составит (3/4) х 32,3 емкости одного кристалла, т.е. увеличится более, чем в 2 раза. Это увеличение может быть еще выше, если кристалл разбивается на более мелкие поднакопители. Источники информации 1.СССР 957273, МПК 011 С 11/00, 1982. 2. АС СССР 433542, МПК 011 С 29/00, 1974. 3. Экспресс-информация. Сер. Вычислительная техника. - 1981. -28. - С. 7-11. 4. Полупроводниковые БИС запоминающих устройств Справочник /В.В. Базанов, Н.В. Бекин, А.Ю. Гордонов и др. - М. Радио и связь, 1986. - С. 360. Национальный центр интеллектуальной собственности. 220072, г. Минск, проспект Ф. Скорины, 66.

МПК / Метки

МПК: G11C 11/00, G11C 29/00

Метки: устройство, запоминающее

Код ссылки

<a href="https://by.patents.su/6-4563-zapominayushhee-ustrojjstvo.html" rel="bookmark" title="База патентов Беларуси">Запоминающее устройство</a>

Предыдущий патент: Способ определения плотности крупнообломочного грунта и устройство для контроля заполнения лунки электролитом

Следующий патент: Способ конденсаторной сварки металлических деталей малых размеров

Случайный патент: Теплогенератор