Запоминающее устройство

Номер патента: 2807

Опубликовано: 30.06.1999

Авторы: Урбанович Павел Павлович, Майоров Сергей Александрович

Текст

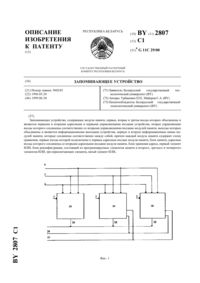

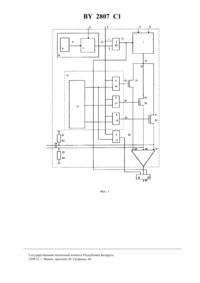

ГОСУДАРСТВЕННЫЙ ПАТЕНТНЫЙ КОМИТЕТ РЕСПУБЛИКИ БЕЛАРУСЬ(71) Заявитель Белорусский государственный технологический университет(73) Патентообладатель Белорусский государственный технологический университет(57) Запоминающее устройство, содержащее модули памяти, первые, вторые и третьи входы которых объединены и являются первыми и вторыми адресными и первыми управляющими входами устройства, вторые управляющие входы которого соединены соответственно со вторыми управляющими входами модулей памяти, выходы которых объединены и являются информационными выходами устройства, первую и вторую информационные шины модулей памяти, которые соединены соответственно между собой, причем каждый модуль памяти содержит схему сравнения, первые входы которой подключены к первым адресным входам модуля памяти, блок памяти, адресные входы которого соединены со вторыми адресными входами модуля памяти, блок хранения адреса, первый элемент ИЛИ, блок реконфигурации, состоящий из программируемых элементов памяти и второго, третьего и четвертого элементов ИЛИ, три переключающих элемента, пятый элемент ИЛИ, Фиг. 1 2807 1 мажоритарный элемент и элемент И, причем первый и второй управляющие входы блока памяти связаны соответственно с первым управляющим входом модуля памяти и выходом первого элемента ИЛИ, соединенным также с первым входом элемента И, а первый и второй входы первого элемента ИЛИ соединены соответственно со вторым управляющим входом модуля памяти, соединенным также с первыми входами второго, третьего и четвертого элементов ИЛИ, и с выходом схемы сравнения, вторыми входами связанной с выходом блока хранения адреса,выход блока памяти соединен с первыми входами переключающих элементов, вторые входы которых соединены с выходами соответственно второго, третьего и четвертого элементов ИЛИ, вторые входы которых связаны с выходами программируемых элементов памяти, выходы первого, второго и третьего переключающих элементов соединены с первым, вторым и третьим входами мажоритарного элемента, второй и третий входы которого соединены соответственно с первой и второй информационными шинами модулей памяти, а выход пятого элемента ИЛИ соединен со вторым входом элемента И, выход которого подключен к информационному выходу устройства,отличающееся тем, что в каждый из модулей памяти введены первый и второй резисторы, причем через первый резистор первая информационная шина подключена к шине питания, а через второй резистор вторая информационная шина подключена к нулевому проводу, третий вход элемента И соединен с выходом мажоритарного элемента, первый вход пятого элемента ИЛИ связан с первым управляющим входом устройства, второй - со вторым входом второго элемента ИЛИ, а переключающие элементы выполнены в виде транзисторных ключей. Изобретение относится к вычислительной технике и может быть использовано при производстве сверхбольших интегральных схем памяти с матричной организацией, имеющих большую площадь кристалла, где требуется высокая емкость памяти, а также при создании ЗУ с интеграцией на целой пластине. Известно запоминающее устройство, содержащее элементы памяти, схемы логики обрамления, позволяющие производить обращение при записи и считывании информации только к одному элементу памяти матрицы и осуществлять коррекцию сигналов с дефектных элементов памяти 1. Недостатками этого запоминающего устройства являются невысокие надежность и быстродействие из-за сложности блоков контроля, большой задержки сигналов в них, введения большого числа разрядных элементов памяти. Другим из известных устройств является система памяти, содержащая устройства памяти, первые и вторые адресные входы, управляющие входы, выход системы, соединенный с первыми выходами устройств,причем первые адресные и управляющие входы системы соединены с первыми и вторыми входами запоминающих блоков в каждом устройстве. Эта система позволяет производить коррекцию как отдельных дефектных элементов памяти, слов, разрядов в запоминающих блоках, так и замену дефектных блоков на исправные 2. Однако известная система характеризуется большой избыточностью и не позволяет использовать для хранения информации отдельные дефектные блоки, что уменьшает эффективно используемую емкость памяти. Наиболее близким техническим решением к предлагаемому изобретению является запоминающее устройство 3, содержащее блоки памяти, первые и вторые входы которых соответственно объединены и являются одним из адресных и управляющим входами устройства, блоки выборки информации, блоки реконфигурации памяти, группы элементов И с первого по пятый, мажоритарные элементы, группы элементов ИЛИ, причем входы блоков выборки информации являются другим адресным входом устройства, выходы блоков выборки информации соединены с первыми входами первых элементов ИЛИ групп, вторые входы которых и входы соответствующих блоков реконфигурации памяти являются контрольными входами устройства, первые входы элементов И каждой группы подключены к выходам одноименного блока реконфигурации памяти, вторые входы элементов И каждой группы с первого по четвертый подключены к выходу одноименного блока реконфигурации памяти, вторые входы элементов И каждой группы с первого по четвертый подключены к выходу одноименного блока памяти, второй вход пятого элемента И каждой группы соединен с выходом второго элемента ИЛИ одноименной группы, входы которого соединены с выходами первого элемента одноименной группы и одноименного мажоритарного элемента, первый, второй и третий входы которого соединены соответственно с выходами второго, третьего и четвертого элементов И одноименной группы, выход первого элемента ИЛИ каждой группы соединен с третьим входом одноименного блока памяти и третьими входами третьего, четвертого и пятого элементов И одноименной группы, выходы пятых элементов И групп являются выходом устройства, выходы третьих и четвертых элементов И групп соответственно объединены, кроме того, каждый блок выборки информации содержит первую группу элементов памяти и блок сравнения, одни из выходов которого являются входами блока, а другие -соединены с 2 2807 1 выходами элементов памяти первой группы, причем выход блока сравнения является выходом блока, а также каждый блок реконфигурации памяти содержит вторую группы элементов памяти и элементов ИЛИ,причем первые входы элементов ИЛИ с первого по четвертый являются входом блока, вторые входы соединены с выходами элементов памяти второй группы, выходы первого и второго элементов памяти второй группы, выходы первого и второго элементов ИЛИ соединены с входами пятого элемента ИЛИ, выходы элементов ИЛИ являются выходами блока. В данном устройстве обеспечивается использование частично годных блоков памяти, что приводит к увеличению эффективной емкости устройства благодаря объединению частично годных блоков в триады, подключаемые к мажоритарному элементу. Каждый из абсолютно годных блоков памяти и каждая из триад блоков памяти имеют свой индивидуальный адрес, присваиваемый при тестировании блоков в процессе цехового контроля ЗУ. Быстродействие этого ЗУ в режиме записи информации практически равно быстродействию безизбыточного, и в режиме считывания - определяется дополнительной задержкой информации на трех логических элементах и мажоритарном элементе и не является оптимальным для данной структуры ЗУ. Задача изобретения - повышение быстродействия устройства и его упрощение. Поставленная задача достигается тем, что в запоминающее устройство содержащее модули памяти, первые, вторые и третьи входы которых объединены и являются первыми и вторыми адресными и первыми управляющими входами устройства, вторые управляющие входы которого соединены соответственно со вторыми управляющими входами модулей памяти, выходы которых объединены и являются информационными выходами устройства, а первая и вторая информационные шины модулей памяти соединены соответственно между собой, причем каждый модуль памяти содержит схему сравнения, первые входы которой подключены к первым адресным входам модуля памяти, блок памяти, адресные входы которого соединены со вторыми адресными входами модуля памяти, а первый и второй управляющие входы блока памяти связаны соответственно с первым управляющим входом модуля памяти и выходом первого элемента ИЛИ, соединенным также с первым входом элемента И, а первый и второй входы первого элемента ИЛИ соединены соответственно со вторым управляющим входом модуля памяти и с выходом схемы сравнения, другими входами связанной с выходом блока хранения адреса, выход блока памяти соединен с первыми входами переключающих элементов, вторые входы которых соединены с выходами с первого по третий блока реконфигурации, состоящего из программируемых элементов памяти и элементов ИЛИ со второго по четвертый, выходами соединенных соответственно с первым, вторым и третьим выходами блока реконфигурации, а первые входы элементов ИЛИ со второго по четвертый блока реконфигурации и первый вход пятого элемента ИЛИ соединены со вторым управляющим входом модуля памяти, вторые входы элементов ИЛИ блока реконфигурации соединены соответственно с выходами программируемых элементов памяти, выходы переключающих элементов соединены соответственно с первым, вторым и третьим входами мажоритарного элемента, первым и вторым входом соединенного также с информационными шинами модулей памяти, введены первый и второй резисторы, причем через первый резистор одна из информационных шин подключена к шине питания, а через другой резистор - вторая информационная шина подключена к земляному (нулевому) проводу, второй и третий входы элемента И соединены с выходами мажоритарного элемента, и пятого элемента ИЛИ, второй вход которого подключен к четвертому выходу блока реконфигурации, соединенному с первым выходом программируемых элементов памяти, а переключающие элементы выполнены в виде транзисторных ключей. Сущность изобретения заключается в том, что на входах мажоритарнго элемента, входами соединенного с триадой блоков памяти (бездефектных или содержащих дефектные элементы памяти по разным, не совпадающим адресам), всегда два считанных символа из трех будут верными. При этом, если считывание производится из блока памяти без дефектов, то на втором и на третьем входах мажоритарного элемента будут разные уровни сигналов, т.к. эти входы через введенные в устройство высокоомные резисторы подключены к шинам питания и земли. Если же считывание осуществляется из триады блоков, то резисторы на считываемую из действующих блоков информацию влияния не оказывают. Совокупность введенных в устройство элементов, связей между ними и остальными элементами устройства обеспечивают требуемый технический результат, выражаемый во взаимосвязанных в данном случае характеристиках повышении быстродействия ЗУ и его упрощении. На фиг. 1 приведена структурная схема одного из модулей памяти, на фиг. 2 - структурная схема всего устройства. Модуль памяти (фиг. 1) содержит блок памяти 1, первые и вторые адресные входы 2 и 3, первые и второй управляющие входы 4 и 5, а также блок хранения адреса 6 и схему сравнения 7, составляющие единый блок выборки 8, первый элемент ИЛИ 11, блок реконфигурации 12, состоящий из программируемых элементов 13 и элементов ИЛИ со второго по четвертый 14-16, и пятый элемент ИЛИ 17, мажоритарный элемент 18,группу транзисторных ключей 19-21, резисторы 1 22 и 2 23, соединяющие собой одну из информационных шин 24 с шиной питания и другую информационную шину 25 - с шиной земли, а выход 26 модуля памяти соединен с выходом элемента И 27, входы 28, 29 и 30 мажоритарного элемента 18, соединенные с выходами ключей 19-21, входами объединенных с выходом 31 блока памяти 1. Пятый элемент ИЛИ 17 имеет 3 2807 1 выход 32, а блок реконфигурации 12 - выходы с первого по третий 33-35, четвертый выход блока реконфигурации 12, соединенных со вторым и входом элемента ИЛИ 17, выход 37 первого элемента ИЛИ 11. Все блоки и элементы, показанные на фиг. 1, составляют модуль памяти 38. Блок памяти 1 представляет собой обычный кристалл памяти со схемами адресации и управления. Блоки 6 и элементы памяти 13 представляют собой программируемые энергонезависимые элементы памяти (ПЗУ,ППЗУ или РПЗУ), которые программируются общеизвестными методам (см., например П.3.5. из 4), ключи 20 и 21 и элемент И 27 при отсутствии единичных сигналов, соответственно на выходах элементов ИЛИ 1517, находятся в закрытом состоянии, характеризующимся высоким входным сопротивлением. Устройство работает следующим образом. При производстве до программирования блока 6 и элементов 13 проводится функциональный контроль каждого блока памяти 1 путем подачи на управляющий вход контроля 5 разрешающего сигнала (логич.1) и соответствующих управляющих сигналов - на адресные и управляющие входы 3 и 4. При этом на выходе 37 элемента ИЛИ 11 появляется сигнал, разрешающий опрос блока 1 для записи/считывания информации. Кроме того, сигнал 5 формирует сигналы 1 на выходах логических элементов ИЛИ 14-17. Сигнал 1 на выходе 32 разрешает прохождение на выход 26 информации с выхода мажоритарного элемента 18, на входы 28-30 которого через открытые транзисторные ключи 19-21 поступает одна и таже информация с выхода 31 накопителя блока 1, поэтому на выходе мажоритарного элемента будет информация, установленная на выходе 31. В это же время все остальные модули 38 не опрашиваются. После функционального контроля, в зависимости от исправности (или неисправности) блоков 1,проводится программирование блока 6 и элементов 13. При исправности модуля памяти 38 (не содержит отказывавших элементов памяти) в блок 6 заносится код адреса этого блока в порядке очередности следования исправных блоков. Например, если необходимо собрать ЗУ из 16 блоков памяти, то адресные входы 2 состоят из 4-х шин (2 16-4). В этом случае первому исправному блоку присваивается код - 0000, второму - 0001,третьему - 0010 и т.д. Кроме того, элементы памяти 13 программируются таким образом, что только на выходе первого элемента памяти, соединенного со входом элемента ИЛИ 17, устанавливается сигнал лог. 1,который открывает через элемент ИЛИ 14 транзисторный ключ 19. Так как на выходах 34 и 35 будут сигналы лог. 0, (на входе 5 - также лог. 0), то транзисторные ключи 20, 21 всегда закрыты. В этом случае на входе 28 мажоритарного элемента 18 будет установлена информация с выхода 31 (лог.0 или лог. 1). На входе 29 - сигнал лог.0 (из-за подключенного резистора 23), на входе 30 - сигнал лог. 1 (из-за включенного резистора 22). Таким образом, на выходах мажориратрного элемента всегда будут два одинаковых по уровню сигнала из трех, и, следовательно, на выходе 20 будет формироваться истинная информация, соответствующая считанной из накопителя. Если в результате контроля окажется, что число годных блоков памяти меньше необходимого (в данном случае меньше 16), то недостающие годные блоки формируются из триад дефектных блоков 1, соединяющихся по мажоритарному принципу информационными шинами 24 и 25. В триады формируются дефектные блоки 1, у которых по одному и тому же адресу 3 содержится не более одного дефектного элемента памяти. Адреса дефектных элементов определяются в процессе функционального контроля блока и заносятся в память контролирующего устройства (на фиг. не показан). Каждой триаде присваивается свой 4-х разрядный адресный код путем занесения одного и того же кода в блок 6 соответствующих модулей памяти 38. Для подключения блоков памяти 1 по мажоритарному принципу элементы блока памяти реконфигурации 12 в триаде программируются следующим образом. В 1-ом блоке (путем программирования) на выходе первого элемента устанавливается лог.1, на выходах других остаются сигналы лог.0. Во втором блоке на выходе второго элемента памяти устанавливается лог.1, на других выходах - лог.0, в третьем на выходе третьего элемента памяти устанавливается лог.1, на выходах других элементов - лог.0. В соответствии с этим выходы мажоритарных элементов 18 во 2-м и 3-ем модулях памяти триады будут отключены от шины 26 сигналом лог.0, поступающим на вход элемента 27 с выхода 32 элемента ИЛИ 17, и только в первом блоке мажоритарный элемент будет включен (на выходе 33 и, следовательно, на входе 27 - сигнал лог. 1). При этом на его входы 28, 29, 30 поступят сигналы с 3-х блоков триады. Так как одновременно по одному и тому же адресу допускается дефект только в одном из блоков, то на выходе 26 мажоритарного элемента первого в триаде модуля во время работы будет истинная информация. Режим работы ЗУ. Запись информации. На входы 2-4 соответствующих модулей памяти (их количество определяется разрядностью устройства и разрядностью каждого блока памяти) подаются адресные и управляющие сигналы. При совпадении адреса на входах 2 и адреса, хранящегося в блоке 6, единичный сигнал на выходе 37 элемента ИЛИ 11 (на шине 5 в режиме работы - лог.0) разрешает обращение к блоку 1. В выбранные ячейки памяти накопителей заносится информация (шины записи на фиг. не показаны). Считывание информации. Обращение к соответствующим ячейкам памяти происходит как и в режиме записи. Если информация считывается из абсолютно бездефектного модуля памяти (только на выходе 33 блока 12 - единичный сигнал), информация с выхода 31 блока 1 через ключ 19 по входу 23 мажоритарного элемента 18, через этот элемент и открытый единичными сигналами 32 и 37 элемент И 27 поступает на выход 26 устройства. При этом на входе 29 элемента 18 будет нулевой сигнал, а на входе 30 - единичный. На 4 2807 1 личие этих сигналов не изменит считываемый по шине 31 бит (или несколько битов) информации. Если же происходит обращение к триаде модулей 38, у которых по некоторым одинаковым адресам 3 имеются дефектные ячейки памяти, то выбор ячеек блоков 1 осуществляется как и в режиме записи. В каждом из модулей триады блок 7 настроен на одинаковый адрес, а на выходах блоков 12 этих модулей единичные сигналы будут установлены следующим образом на выходе 33 первого, на выходе 34 второго и на выходе 35 третьего модуля, т.е. разрешение на прохождение считанной информации будет обеспечено единичным сигналом на шине 32 только в первом из модулей. При этом информация с выхода 31 первого из опрашиваемых блоков 1 через соответствующий элемент 19 поступает непосредственно на выход 28 элемента 18, информация с выхода 31 второго модуля через соответствующий ключ 20 по шине 25 поступает на выход 29 того же элемента 18, а информация с выхода 31 третьего блока 1 через соответствующий ключ 21 по шине 24 поступает на выход 30 того же элемента 18. По крайней мере, два из трех сигналов будут истинными, и на выходе 26 также будет истинная информация. Таким образом, предлагаемое устройство выполняет те же функции, что и известное. Однако, при одинаковой структуре блоков 1 и одинаковой общей информационной емкости устройств предлагаемое ЗУ проще известного. Действительно, блок 12 имеет вместо четырех три программируемых элемента (в общем объеме это на 25 меньше). По сравнению с 12-ю логическими элементами (И и ИЛИ) в известном устройстве (в одном модуле) предлагаемое имеет 9, три из которых - простые ключи, т.е. сложность дополнительных схем также примерно на 25 меньше в предлагаемом устройстве, что очень важно для больших ЗУ с интеграцией на целой пластине. Сравниваемые показатели быстродействия у обоих устройств при одинаковых блоках 1 и элементах 18 определяются задержкой сигнала на трех логических элементах - в известном устройстве, и на одном логическом элементе и одном транзисторе - в предлагаемом, что составляет примерно 25-40(в зависимости от технологии изготовления ЗУ). Следовательно, в упрощении устройства и в повышении его быстродействия по сравнению с известным и заключаются технико-экономические преимущества изобретения. Государственный патентный комитет Республики Беларусь. 220072, г. Минск, проспект Ф. Скорины, 66.

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, устройство

Код ссылки

<a href="https://by.patents.su/6-2807-zapominayushhee-ustrojjstvo.html" rel="bookmark" title="База патентов Беларуси">Запоминающее устройство</a>

Предыдущий патент: Механизированный склад

Следующий патент: Преобразователь выходного сигнала дифференциально-трансформаторного датчика

Случайный патент: Плазмотрон для нанесения покрытия