Устройство для передачи данных на железнодорожные маяки

Текст

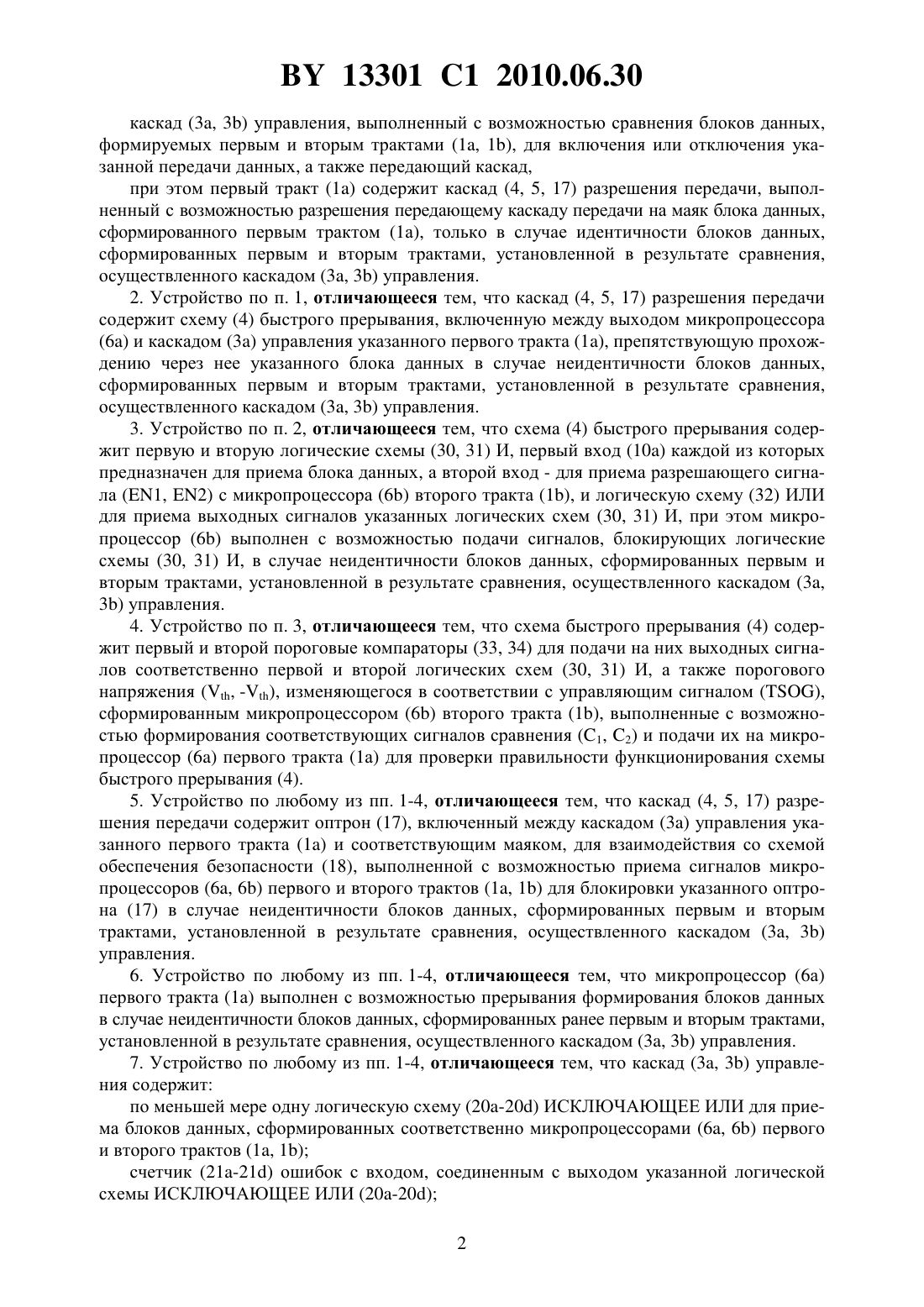

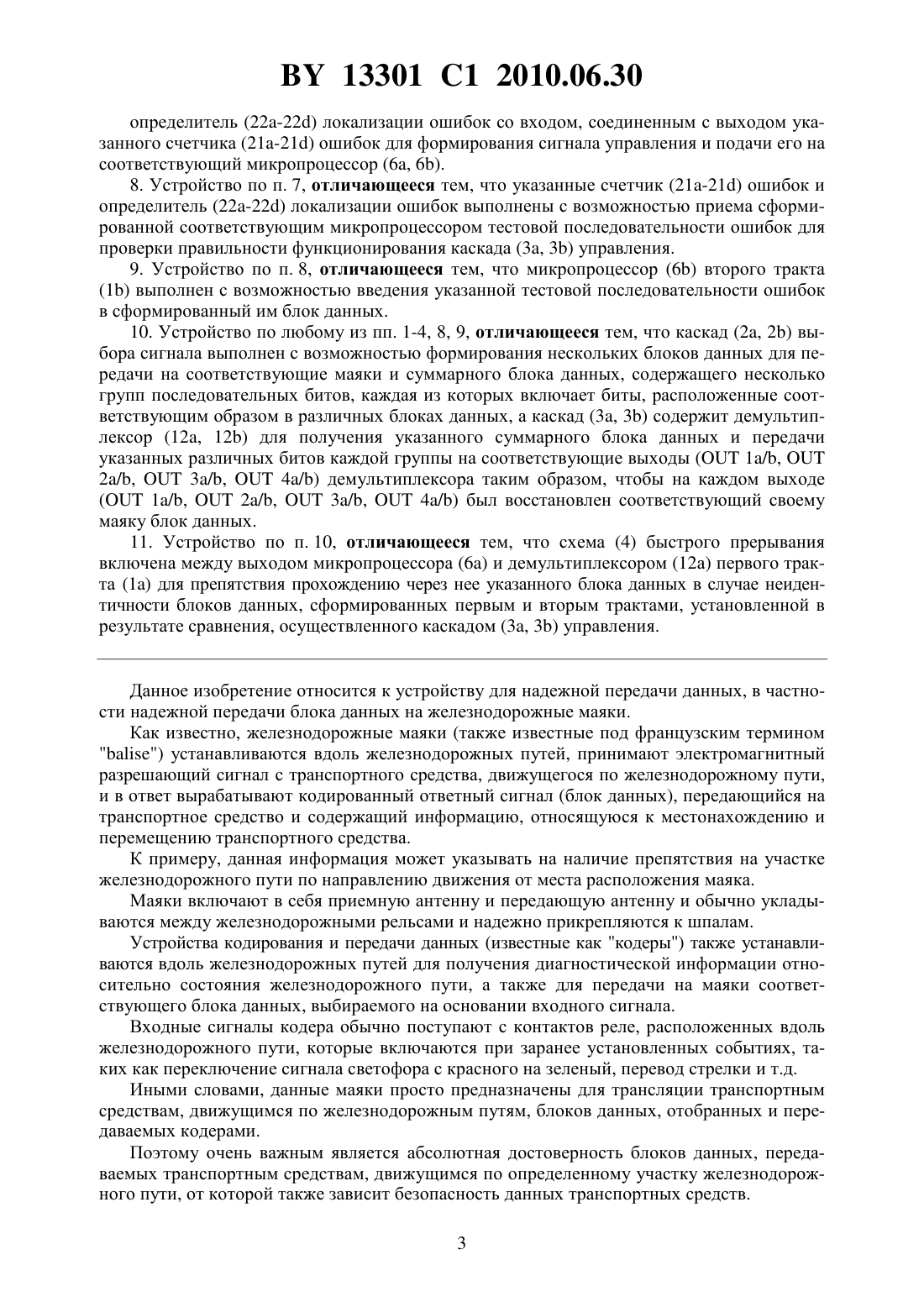

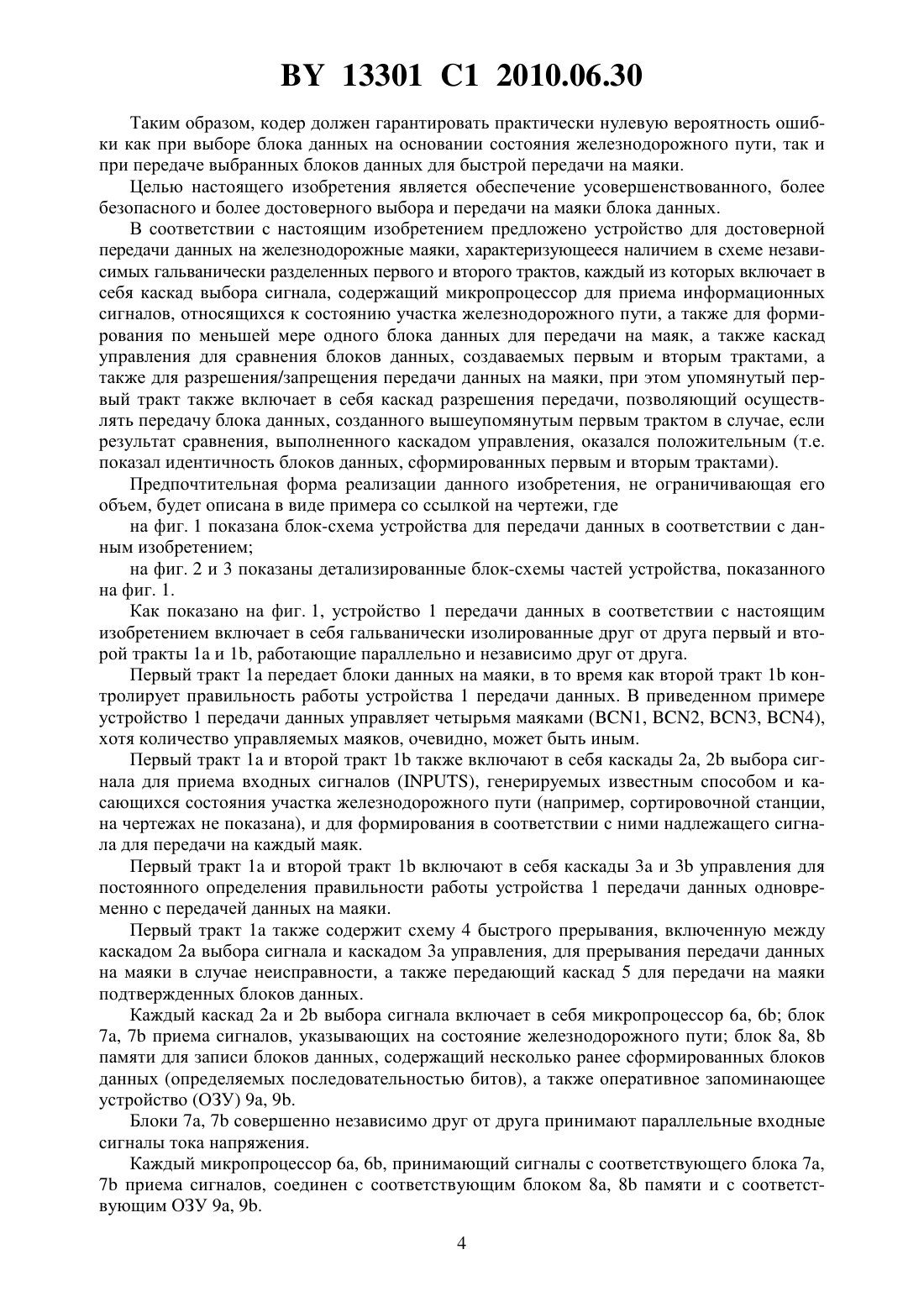

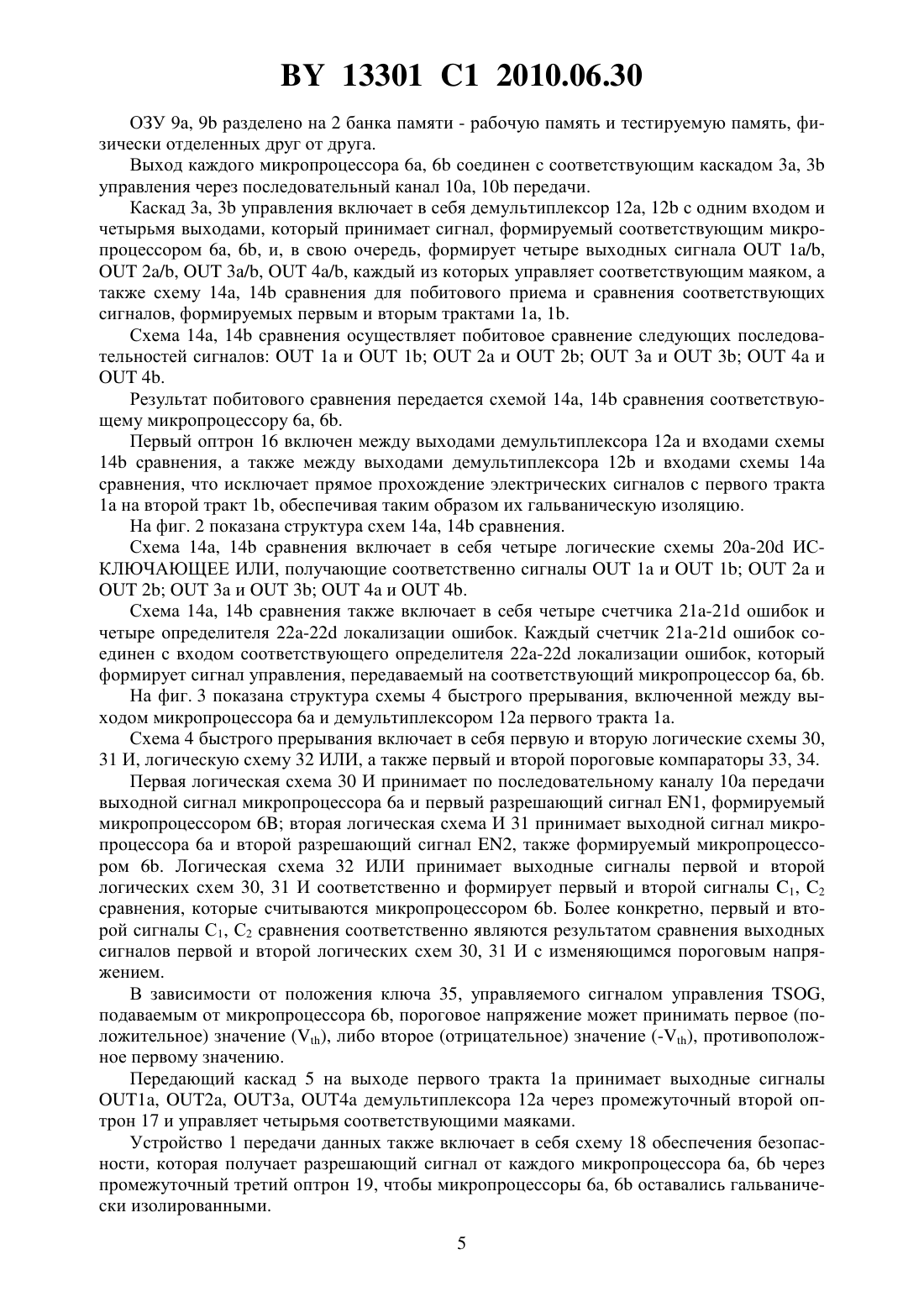

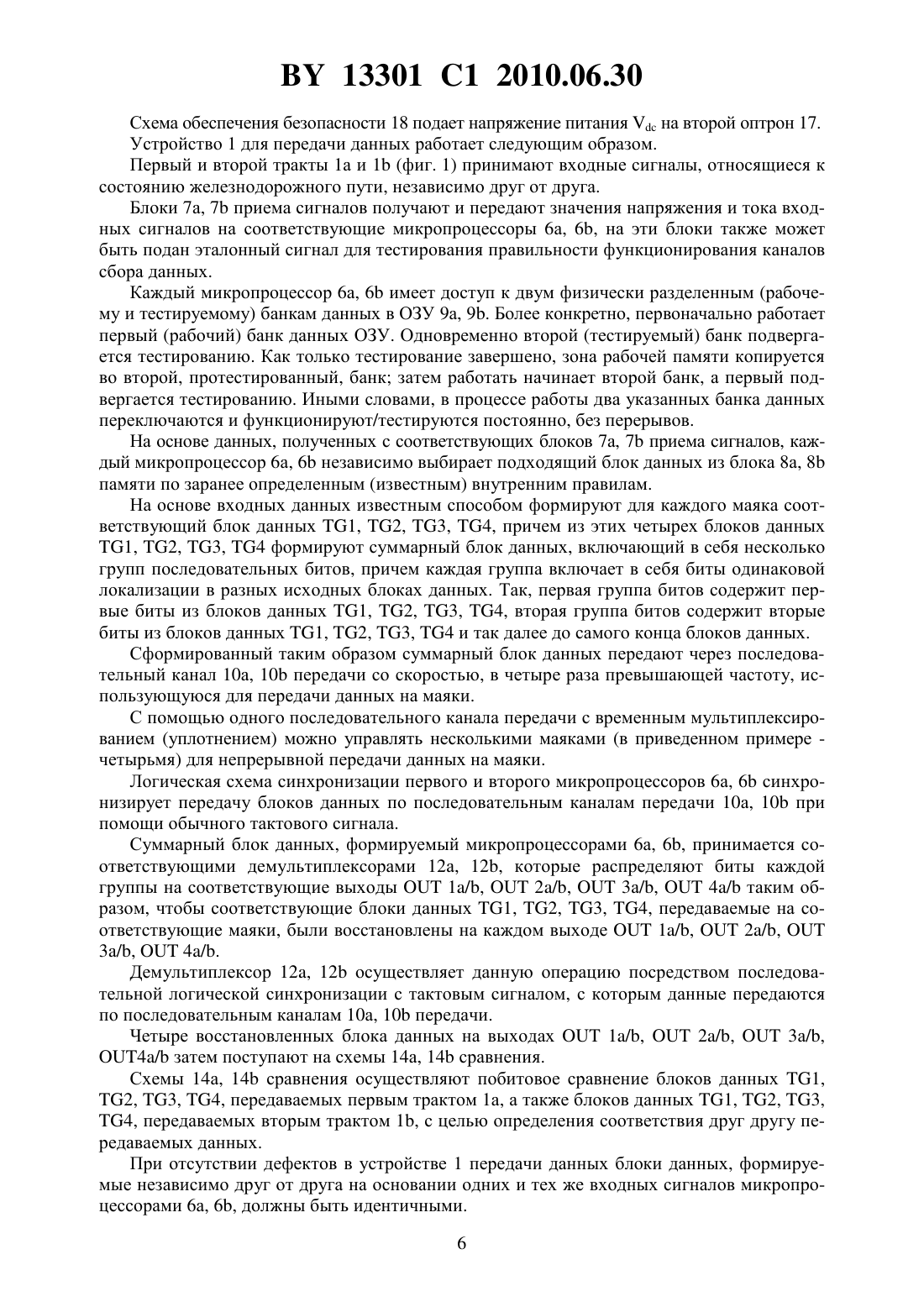

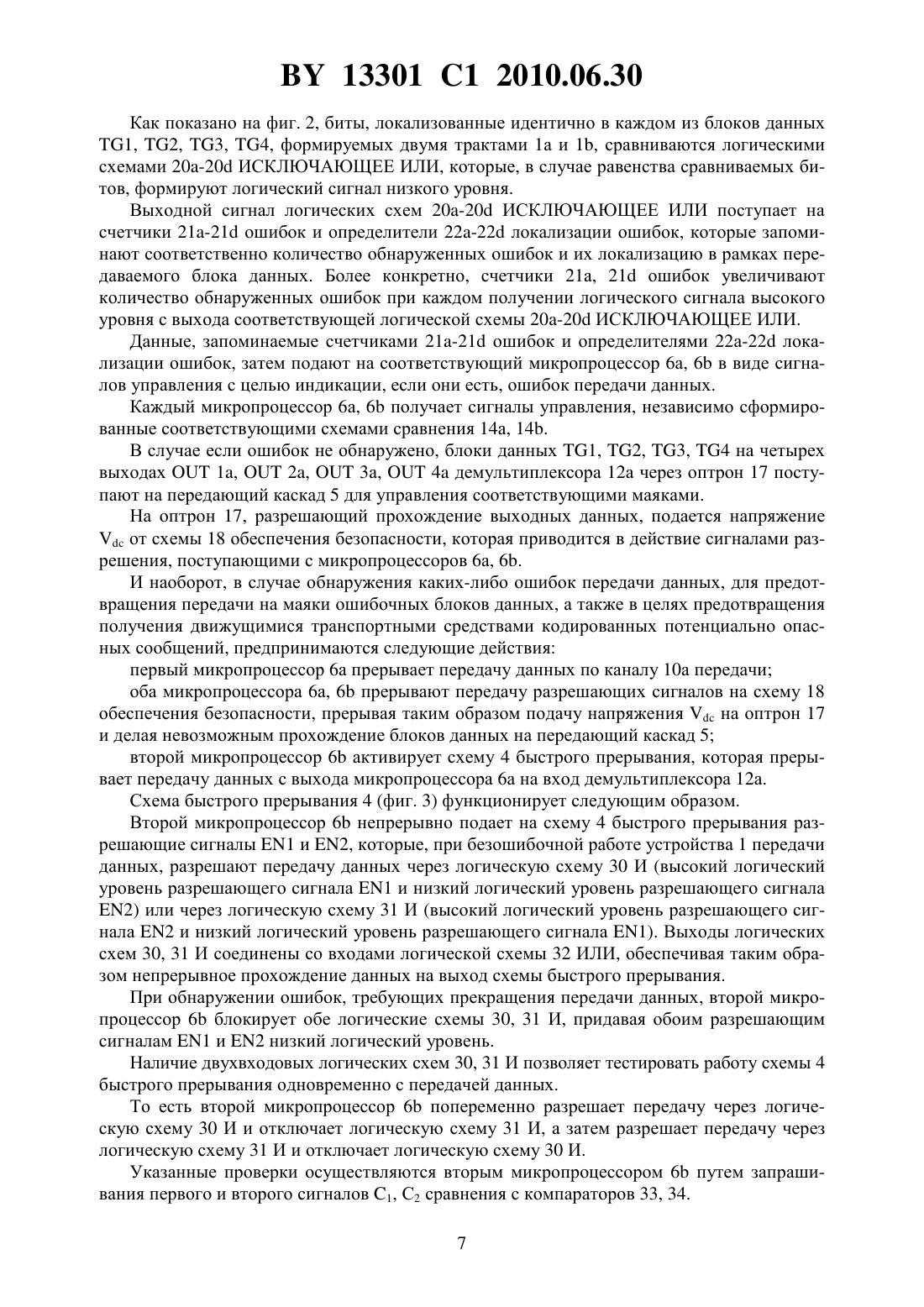

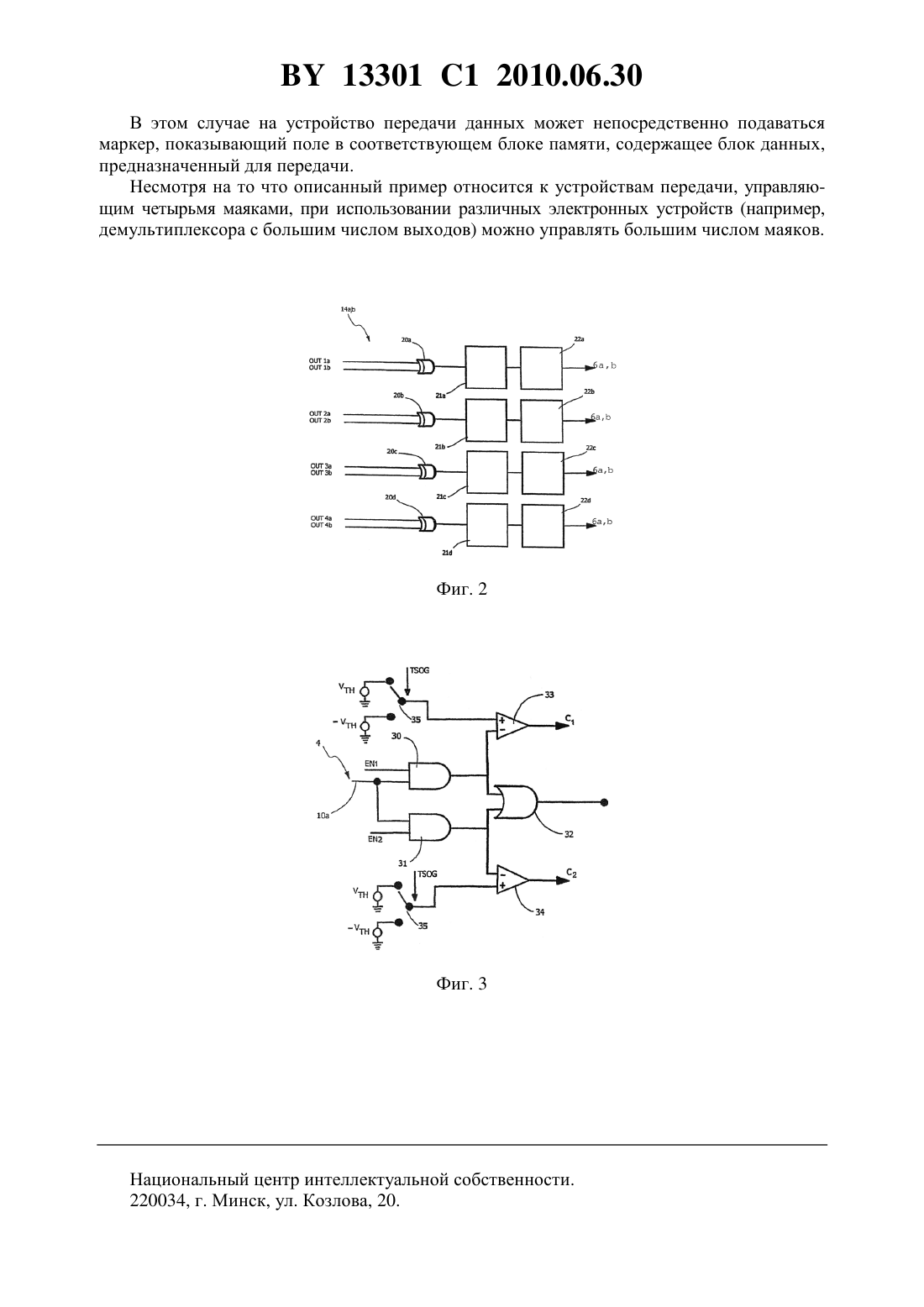

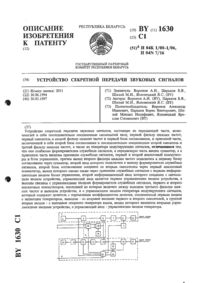

(51) МПК (2009) НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ НА ЖЕЛЕЗНОДОРОЖНЫЕ МАЯКИ(71) Заявитель АНСАЛЬДО СТС С.П.А.(73) Патентообладатель АНСАЛЬДО СТС С.П.А.(57) 1. Устройство (1) для передачи данных на железнодорожные маяки, содержащее независимые и гальванически изолированные друг от друга первый и второй тракты (1, 1),каждый из которых содержит каскад (2, 2) выбора сигнала, содержащий микропроцессор (6, 6) и выполненный с возможностью как приема информационных сигналов относительно состояния участка железнодорожного пути, так и формирования по меньшей мере одного блока данных для передачи на соответствующий маяк 13301 1 2010.06.30 каскад (3, 3) управления, выполненный с возможностью сравнения блоков данных,формируемых первым и вторым трактами (1, 1), для включения или отключения указанной передачи данных, а также передающий каскад,при этом первый тракт (1) содержит каскад (4, 5, 17) разрешения передачи, выполненный с возможностью разрешения передающему каскаду передачи на маяк блока данных,сформированного первым трактом (1 а), только в случае идентичности блоков данных,сформированных первым и вторым трактами, установленной в результате сравнения,осуществленного каскадом (3, 3) управления. 2. Устройство по п. 1, отличающееся тем, что каскад (4, 5, 17) разрешения передачи содержит схему (4) быстрого прерывания, включенную между выходом микропроцессора(6) и каскадом (3) управления указанного первого тракта (1), препятствующую прохождению через нее указанного блока данных в случае неидентичности блоков данных,сформированных первым и вторым трактами, установленной в результате сравнения,осуществленного каскадом (3, 3) управления. 3. Устройство по п. 2, отличающееся тем, что схема (4) быстрого прерывания содержит первую и вторую логические схемы (30, 31) И, первый вход (10) каждой из которых предназначен для приема блока данных, а второй вход - для приема разрешающего сигнала (1, 2) с микропроцессора (6) второго тракта (1), и логическую схему (32) ИЛИ для приема выходных сигналов указанных логических схем (30, 31) И, при этом микропроцессор (6) выполнен с возможностью подачи сигналов, блокирующих логические схемы (30, 31) И, в случае неидентичности блоков данных, сформированных первым и вторым трактами, установленной в результате сравнения, осуществленного каскадом (3,3) управления. 4. Устройство по п. 3, отличающееся тем, что схема быстрого прерывания (4) содержит первый и второй пороговые компараторы (33, 34) для подачи на них выходных сигналов соответственно первой и второй логических схем (30, 31) И, а также порогового напряжения (, -), изменяющегося в соответствии с управляющим сигналом ,сформированным микропроцессором (6) второго тракта (1), выполненные с возможностью формирования соответствующих сигналов сравнения (1, 2) и подачи их на микропроцессор (6) первого тракта (1 а) для проверки правильности функционирования схемы быстрого прерывания (4). 5. Устройство по любому из пп. 1-4, отличающееся тем, что каскад (4, 5, 17) разрешения передачи содержит оптрон (17), включенный между каскадом (3) управления указанного первого тракта (1) и соответствующим маяком, для взаимодействия со схемой обеспечения безопасности (18), выполненной с возможностью приема сигналов микропроцессоров (6, 6) первого и второго трактов (1, 1) для блокировки указанного оптрона (17) в случае неидентичности блоков данных, сформированных первым и вторым трактами, установленной в результате сравнения, осуществленного каскадом (3, 3) управления. 6. Устройство по любому из пп. 1-4, отличающееся тем, что микропроцессор (6 а) первого тракта (1 а) выполнен с возможностью прерывания формирования блоков данных в случае неидентичности блоков данных, сформированных ранее первым и вторым трактами,установленной в результате сравнения, осуществленного каскадом (3, 3) управления. 7. Устройство по любому из пп. 1-4, отличающееся тем, что каскад (3, 3) управления содержит по меньшей мере одну логическую схему (20-20) ИСКЛЮЧАЮЩЕЕ ИЛИ для приема блоков данных, сформированных соответственно микропроцессорами (6, 6) первого и второго трактов (1, 1) счетчик (21-21) ошибок с входом, соединенным с выходом указанной логической схемы ИСКЛЮЧАЮЩЕЕ ИЛИ (20-20) 2 13301 1 2010.06.30 определитель (22-22) локализации ошибок со входом, соединенным с выходом указанного счетчика (21-21) ошибок для формирования сигнала управления и подачи его на соответствующий микропроцессор (6, 6). 8. Устройство по п. 7, отличающееся тем, что указанные счетчик (21-21) ошибок и определитель (22-22) локализации ошибок выполнены с возможностью приема сформированной соответствующим микропроцессором тестовой последовательности ошибок для проверки правильности функционирования каскада (3, 3) управления. 9. Устройство по п. 8, отличающееся тем, что микропроцессор (6) второго тракта(1) выполнен с возможностью введения указанной тестовой последовательности ошибок в сформированный им блок данных. 10. Устройство по любому из пп. 1-4, 8, 9, отличающееся тем, что каскад (2, 2) выбора сигнала выполнен с возможностью формирования нескольких блоков данных для передачи на соответствующие маяки и суммарного блока данных, содержащего несколько групп последовательных битов, каждая из которых включает биты, расположенные соответствующим образом в различных блоках данных, а каскад (3, 3) содержит демультиплексор (12, 12) для получения указанного суммарного блока данных и передачи указанных различных битов каждой группы на соответствующие выходы ( 1/,2/,3/,4/) демультиплексора таким образом, чтобы на каждом выходе( 1/,2/,3/,4/) был восстановлен соответствующий своему маяку блок данных. 11. Устройство по п. 10, отличающееся тем, что схема (4) быстрого прерывания включена между выходом микропроцессора (6) и демультиплексором (12 а) первого тракта (1) для препятствия прохождению через нее указанного блока данных в случае неидентичности блоков данных, сформированных первым и вторым трактами, установленной в результате сравнения, осуществленного каскадом (3, 3) управления. Данное изобретение относится к устройству для надежной передачи данных, в частности надежной передачи блока данных на железнодорожные маяки. Как известно, железнодорожные маяки (также известные под французским термином) устанавливаются вдоль железнодорожных путей, принимают электромагнитный разрешающий сигнал с транспортного средства, движущегося по железнодорожному пути,и в ответ вырабатывают кодированный ответный сигнал (блок данных), передающийся на транспортное средство и содержащий информацию, относящуюся к местонахождению и перемещению транспортного средства. К примеру, данная информация может указывать на наличие препятствия на участке железнодорожного пути по направлению движения от места расположения маяка. Маяки включают в себя приемную антенну и передающую антенну и обычно укладываются между железнодорожными рельсами и надежно прикрепляются к шпалам. Устройства кодирования и передачи данных (известные как кодеры) также устанавливаются вдоль железнодорожных путей для получения диагностической информации относительно состояния железнодорожного пути, а также для передачи на маяки соответствующего блока данных, выбираемого на основании входного сигнала. Входные сигналы кодера обычно поступают с контактов реле, расположенных вдоль железнодорожного пути, которые включаются при заранее установленных событиях, таких как переключение сигнала светофора с красного на зеленый, перевод стрелки и т.д. Иными словами, данные маяки просто предназначены для трансляции транспортным средствам, движущимся по железнодорожным путям, блоков данных, отобранных и передаваемых кодерами. Поэтому очень важным является абсолютная достоверность блоков данных, передаваемых транспортным средствам, движущимся по определенному участку железнодорожного пути, от которой также зависит безопасность данных транспортных средств. 3 13301 1 2010.06.30 Таким образом, кодер должен гарантировать практически нулевую вероятность ошибки как при выборе блока данных на основании состояния железнодорожного пути, так и при передаче выбранных блоков данных для быстрой передачи на маяки. Целью настоящего изобретения является обеспечение усовершенствованного, более безопасного и более достоверного выбора и передачи на маяки блока данных. В соответствии с настоящим изобретением предложено устройство для достоверной передачи данных на железнодорожные маяки, характеризующееся наличием в схеме независимых гальванически разделенных первого и второго трактов, каждый из которых включает в себя каскад выбора сигнала, содержащий микропроцессор для приема информационных сигналов, относящихся к состоянию участка железнодорожного пути, а также для формирования по меньшей мере одного блока данных для передачи на маяк, а также каскад управления для сравнения блоков данных, создаваемых первым и вторым трактами, а также для разрешения/запрещения передачи данных на маяки, при этом упомянутый первый тракт также включает в себя каскад разрешения передачи, позволяющий осуществлять передачу блока данных, созданного вышеупомянутым первым трактом в случае, если результат сравнения, выполненного каскадом управления, оказался положительным (т.е. показал идентичность блоков данных, сформированных первым и вторым трактами). Предпочтительная форма реализации данного изобретения, не ограничивающая его объем, будет описана в виде примера со ссылкой на чертежи, где на фиг. 1 показана блок-схема устройства для передачи данных в соответствии с данным изобретением на фиг. 2 и 3 показаны детализированные блок-схемы частей устройства, показанного на фиг. 1. Как показано на фиг. 1, устройство 1 передачи данных в соответствии с настоящим изобретением включает в себя гальванически изолированные друг от друга первый и второй тракты 1 и 1, работающие параллельно и независимо друг от друга. Первый тракт 1 передает блоки данных на маяки, в то время как второй тракт 1 контролирует правильность работы устройства 1 передачи данных. В приведенном примере устройство 1 передачи данных управляет четырьмя маяками (1, 2, 3, 4),хотя количество управляемых маяков, очевидно, может быть иным. Первый тракт 1 и второй тракт 1 также включают в себя каскады 2, 2 выбора сигнала для приема входных сигналов , генерируемых известным способом и касающихся состояния участка железнодорожного пути (например, сортировочной станции,на чертежах не показана), и для формирования в соответствии с ними надлежащего сигнала для передачи на каждый маяк. Первый тракт 1 и второй тракт 1 включают в себя каскады 3 и 3 управления для постоянного определения правильности работы устройства 1 передачи данных одновременно с передачей данных на маяки. Первый тракт 1 также содержит схему 4 быстрого прерывания, включенную между каскадом 2 а выбора сигнала и каскадом 3 управления, для прерывания передачи данных на маяки в случае неисправности, а также передающий каскад 5 для передачи на маяки подтвержденных блоков данных. Каждый каскад 2 и 2 выбора сигнала включает в себя микропроцессор 6, 6 блок 7, 7 приема сигналов, указывающих на состояние железнодорожного пути блок 8 а, 8 памяти для записи блоков данных, содержащий несколько ранее сформированных блоков данных (определяемых последовательностью битов), а также оперативное запоминающее устройство (ОЗУ) 9 а, 9. Блоки 7 а, 7 совершенно независимо друг от друга принимают параллельные входные сигналы тока напряжения. Каждый микропроцессор 6 а, 6, принимающий сигналы с соответствующего блока 7 а,7 приема сигналов, соединен с соответствующим блоком 8 а, 8 памяти и с соответствующим ОЗУ 9 а, 9. 4 13301 1 2010.06.30 ОЗУ 9 а, 9 разделено на 2 банка памяти - рабочую память и тестируемую память, физически отделенных друг от друга. Выход каждого микропроцессора 6 а, 6 соединен с соответствующим каскадом 3, 3 управления через последовательный канал 10 а, 10 передачи. Каскад 3, 3 управления включает в себя демультиплексор 12 а, 12 с одним входом и четырьмя выходами, который принимает сигнал, формируемый соответствующим микропроцессором 6 а, 6, и, в свою очередь, формирует четыре выходных сигнала 1/, 2/,3 а/,4/, каждый из которых управляет соответствующим маяком, а также схему 14 а, 14 сравнения для побитового приема и сравнения соответствующих сигналов, формируемых первым и вторым трактами 1 а, 1. Схема 14 а, 14 сравнения осуществляет побитовое сравнение следующих последовательностей сигналов 1 а и 12 и 23 а и 34 и 4. Результат побитового сравнения передается схемой 14 а, 14 сравнения соответствующему микропроцессору 6 а, 6. Первый оптрон 16 включен между выходами демультиплексора 12 а и входами схемы 14 сравнения, а также между выходами демультиплексора 12 и входами схемы 14 а сравнения, что исключает прямое прохождение электрических сигналов с первого тракта 1 а на второй тракт 1, обеспечивая таким образом их гальваническую изоляцию. На фиг. 2 показана структура схем 14 а, 14 сравнения. Схема 14 а, 14 сравнения включает в себя четыре логические схемы 20 а-20 ИСКЛЮЧАЮЩЕЕ ИЛИ, получающие соответственно сигналы 1 и 12 а и 23 а и 34 и 4. Схема 14, 14 сравнения также включает в себя четыре счетчика 21-21 ошибок и четыре определителя 22-22 локализации ошибок. Каждый счетчик 21-21 ошибок соединен с входом соответствующего определителя 22-22 локализации ошибок, который формирует сигнал управления, передаваемый на соответствующий микропроцессор 6 а, 6. На фиг. 3 показана структура схемы 4 быстрого прерывания, включенной между выходом микропроцессора 6 а и демультиплексором 12 а первого тракта 1 а. Схема 4 быстрого прерывания включает в себя первую и вторую логические схемы 30,31 И, логическую схему 32 ИЛИ, а также первый и второй пороговые компараторы 33, 34. Первая логическая схема 30 И принимает по последовательному каналу 10 а передачи выходной сигнал микропроцессора 6 а и первый разрешающий сигнал 1, формируемый микропроцессором 6 вторая логическая схема И 31 принимает выходной сигнал микропроцессора 6 а и второй разрешающий сигнал 2, также формируемый микропроцессором 6. Логическая схема 32 ИЛИ принимает выходные сигналы первой и второй логических схем 30, 31 И соответственно и формирует первый и второй сигналы 1, 2 сравнения, которые считываются микропроцессором 6. Более конкретно, первый и второй сигналы С 1, С 2 сравнения соответственно являются результатом сравнения выходных сигналов первой и второй логических схем 30, 31 И с изменяющимся пороговым напряжением. В зависимости от положения ключа 35, управляемого сигналом управления ,подаваемым от микропроцессора 6, пороговое напряжение может принимать первое (положительное) значение , либо второе (отрицательное) значение (-), противоположное первому значению. Передающий каскад 5 на выходе первого тракта 1 а принимает выходные сигналы 1, 2, 3, 4 демультиплексора 12 а через промежуточный второй оптрон 17 и управляет четырьмя соответствующими маяками. Устройство 1 передачи данных также включает в себя схему 18 обеспечения безопасности, которая получает разрешающий сигнал от каждого микропроцессора 6 а, 6 через промежуточный третий оптрон 19, чтобы микропроцессоры 6 а, 6 оставались гальванически изолированными. 5 13301 1 2010.06.30 Схема обеспечения безопасности 18 подает напряжение питанияна второй оптрон 17. Устройство 1 для передачи данных работает следующим образом. Первый и второй тракты 1 а и 1 (фиг. 1) принимают входные сигналы, относящиеся к состоянию железнодорожного пути, независимо друг от друга. Блоки 7 а, 7 приема сигналов получают и передают значения напряжения и тока входных сигналов на соответствующие микропроцессоры 6 а, 6, на эти блоки также может быть подан эталонный сигнал для тестирования правильности функционирования каналов сбора данных. Каждый микропроцессор 6 а, 6 имеет доступ к двум физически разделенным (рабочему и тестируемому) банкам данных в ОЗУ 9 а, 9. Более конкретно, первоначально работает первый (рабочий) банк данных ОЗУ. Одновременно второй (тестируемый) банк подвергается тестированию. Как только тестирование завершено, зона рабочей памяти копируется во второй, протестированный, банк затем работать начинает второй банк, а первый подвергается тестированию. Иными словами, в процессе работы два указанных банка данных переключаются и функционируют/тестируются постоянно, без перерывов. На основе данных, полученных с соответствующих блоков 7 а, 7 приема сигналов, каждый микропроцессор 6 а, 6 независимо выбирает подходящий блок данных из блока 8 а, 8 памяти по заранее определенным (известным) внутренним правилам. На основе входных данных известным способом формируют для каждого маяка соответствующий блок данных 1, 2, 3, 4, причем из этих четырех блоков данных 1, 2, 3, 4 формируют суммарный блок данных, включающий в себя несколько групп последовательных битов, причем каждая группа включает в себя биты одинаковой локализации в разных исходных блоках данных. Так, первая группа битов содержит первые биты из блоков данных 1, 2, 3, 4, вторая группа битов содержит вторые биты из блоков данных 1, 2, 3, 4 и так далее до самого конца блоков данных. Сформированный таким образом суммарный блок данных передают через последовательный канал 10 а, 10 передачи со скоростью, в четыре раза превышающей частоту, использующуюся для передачи данных на маяки. С помощью одного последовательного канала передачи с временным мультиплексированием (уплотнением) можно управлять несколькими маяками (в приведенном примере четырьмя) для непрерывной передачи данных на маяки. Логическая схема синхронизации первого и второго микропроцессоров 6 а, 6 синхронизирует передачу блоков данных по последовательным каналам передачи 10 а, 10 при помощи обычного тактового сигнала. Суммарный блок данных, формируемый микропроцессорами 6 а, 6, принимается соответствующими демультиплексорами 12 а, 12, которые распределяют биты каждой группы на соответствующие выходы 1/,2/,3 а/,4/ таким образом, чтобы соответствующие блоки данных 1, 2, 3, 4, передаваемые на соответствующие маяки, были восстановлены на каждом выходе 1/,2/,3 а/,4/. Демультиплексор 12, 12 осуществляет данную операцию посредством последовательной логической синхронизации с тактовым сигналом, с которым данные передаются по последовательным каналам 10 а, 10 передачи. Четыре восстановленных блока данных на выходах 1/,2/,3 а/,4/ затем поступают на схемы 14 а, 14 сравнения. Схемы 14 а, 14 сравнения осуществляют побитовое сравнение блоков данных 1,2, 3, 4, передаваемых первым трактом 1 а, а также блоков данных 1, 2, 3,4, передаваемых вторым трактом 1, с целью определения соответствия друг другу передаваемых данных. При отсутствии дефектов в устройстве 1 передачи данных блоки данных, формируемые независимо друг от друга на основании одних и тех же входных сигналов микропроцессорами 6 а, 6, должны быть идентичными. 6 13301 1 2010.06.30 Как показано на фиг. 2, биты, локализованные идентично в каждом из блоков данных 1, 2, 3, 4, формируемых двумя трактами 1 а и 1, сравниваются логическими схемами 20-20 ИСКЛЮЧАЮЩЕЕ ИЛИ, которые, в случае равенства сравниваемых битов, формируют логический сигнал низкого уровня. Выходной сигнал логических схем 20-20 ИСКЛЮЧАЮЩЕЕ ИЛИ поступает на счетчики 21-21 ошибок и определители 22-22 локализации ошибок, которые запоминают соответственно количество обнаруженных ошибок и их локализацию в рамках передаваемого блока данных. Более конкретно, счетчики 21 а, 21 ошибок увеличивают количество обнаруженных ошибок при каждом получении логического сигнала высокого уровня с выхода соответствующей логической схемы 20-20 ИСКЛЮЧАЮЩЕЕ ИЛИ. Данные, запоминаемые счетчиками 21-21 ошибок и определителями 22 а-22 локализации ошибок, затем подают на соответствующий микропроцессор 6 а, 6 в виде сигналов управления с целью индикации, если они есть, ошибок передачи данных. Каждый микропроцессор 6 а, 6 получает сигналы управления, независимо сформированные соответствующими схемами сравнения 14 а, 14. В случае если ошибок не обнаружено, блоки данных 1, 2, 3, 4 на четырех выходах 1,2,3 а,4 демультиплексора 12 а через оптрон 17 поступают на передающий каскад 5 для управления соответствующими маяками. На оптрон 17, разрешающий прохождение выходных данных, подается напряжениеот схемы 18 обеспечения безопасности, которая приводится в действие сигналами разрешения, поступающими с микропроцессоров 6 а, 6. И наоборот, в случае обнаружения каких-либо ошибок передачи данных, для предотвращения передачи на маяки ошибочных блоков данных, а также в целях предотвращения получения движущимися транспортными средствами кодированных потенциально опасных сообщений, предпринимаются следующие действия первый микропроцессор 6 а прерывает передачу данных по каналу 10 а передачи оба микропроцессора 6 а, 6 прерывают передачу разрешающих сигналов на схему 18 обеспечения безопасности, прерывая таким образом подачу напряженияна оптрон 17 и делая невозможным прохождение блоков данных на передающий каскад 5 второй микропроцессор 6 активирует схему 4 быстрого прерывания, которая прерывает передачу данных с выхода микропроцессора 6 а на вход демультиплексора 12 а. Схема быстрого прерывания 4 (фиг. 3) функционирует следующим образом. Второй микропроцессор 6 непрерывно подает на схему 4 быстрого прерывания разрешающие сигналы 1 и 2, которые, при безошибочной работе устройства 1 передачи данных, разрешают передачу данных через логическую схему 30 И (высокий логический уровень разрешающего сигнала 1 и низкий логический уровень разрешающего сигнала 2) или через логическую схему 31 И (высокий логический уровень разрешающего сигнала 2 и низкий логический уровень разрешающего сигнала 1). Выходы логических схем 30, 31 И соединены со входами логической схемы 32 ИЛИ, обеспечивая таким образом непрерывное прохождение данных на выход схемы быстрого прерывания. При обнаружении ошибок, требующих прекращения передачи данных, второй микропроцессор 6 блокирует обе логические схемы 30, 31 И, придавая обоим разрешающим сигналам 1 и 2 низкий логический уровень. Наличие двухвходовых логических схем 30, 31 И позволяет тестировать работу схемы 4 быстрого прерывания одновременно с передачей данных. То есть второй микропроцессор 6 попеременно разрешает передачу через логическую схему 30 И и отключает логическую схему 31 И, а затем разрешает передачу через логическую схему 31 И и отключает логическую схему 30 И. Указанные проверки осуществляются вторым микропроцессором 6 путем запрашивания первого и второго сигналов 1, С 2 сравнения с компараторов 33, 34. 7 13301 1 2010.06.30 Для этого микропроцессор 6 выполнен с возможностью размыкания ключа 35 (посредством управляющего сигнала ) и изменения тем самым порога компараторов 33,34, а также с возможностью проверки отключения выходов логических схем 30, 31 И. При отключенной логической схеме 30 И проверка осуществляется путем считывания выходного сигнала 1 соответствующего компаратора 33 наряду с изменением значения его входного порогового напряжения. На выходе логической схемы И 30 (отключенной) появляется, таким образом, опорное значение (например, нулевое), которое поступает на вход компаратора 33, на второй вход которого поступает положительное либо отрицательное пороговое напряжение (, - ) так, что фактическое отключение логической схемы 30 И может определяться просто определением переключения выхода компаратора 33, а также изменением порогового напряжения. То же применимо к определению фактического отключения логической схемы 31 И. Устройство 1 передачи данных также предусматривает тестирование работы схем 14 а,14 сравнения, в частности выявление ошибок детекторов и запоминающих ячеек, одновременно с передачей блоков данных на маяки. Микропроцессор 6 вводит в блок данных, передаваемый по последовательному каналу 10 передачи, последовательность ошибок в известном количестве и с заранее заданной локализацией в блоке данных. Это возможно, если на маяки передают блоки данных, сформированные микропроцессором 6 а, передаваемые по последовательному каналу 10 а передачи и не содержащие ошибок. Как только заданное число битов блока данных передано, каждый микропроцессор 6 а,6 независимо друг от друга проверяет, соответствует ли число и локализация запрограммированных ошибок (в рамках тестовой последовательности ошибок) числу и локализации обнаруженных ошибок. Таким образом можно осуществлять тестирование правильности работы схем 14 а, 14 сравнения, а в случае несоответствия обнаруженных ошибок прерывать передачу блоков данных. Преимущества данного изобретения указаны ниже. В частности, при использовании двух независимых друг от друга, гальваническиизолированных трактов для независимого приема входных сигналов и формирования соответствующих блоков данных, а также двух независимых схем сравнения для сравнения и подтверждения соответствия двух блоков данных значительно повышается степень достоверности передачи данных на маяки. Устройство передачи данных согласно настоящему изобретению предусматривает три взаимодействующих способа скорейшего прерывания передачи данных при обнаружении каких-либо ошибок прерывание передачи данных по выходному последовательному каналу включение схемы быстрого прерывания отключение схемы обеспечения безопасности для прекращения подачи напряжения питания на выходной оптрон, а следовательно, и передачи данных на маяки. Более того, благодаря соответствующему построению схемы, устройство передачи данных осуществляет непрерывное тестирование своего функционирования, не прерывая при этом передачу данных на маяки. Таким образом, тестируется функционирование блоков приема входных сигналов, рабочей памяти ОЗУ микропроцессора, схем сравнения и определения ошибок передачи, а также схемы быстрого прерывания. В описанное выше изобретение могут вноситься изменения, не выходящие за пределы настоящего изобретения, определенного в прилагаемой формуле изобретения. В частности, для отбора передаваемых блоков данных, основанных на состоянии железнодорожного пути, может быть использовано иное устройство. 8 13301 1 2010.06.30 В этом случае на устройство передачи данных может непосредственно подаваться маркер, показывающий поле в соответствующем блоке памяти, содержащее блок данных,предназначенный для передачи. Несмотря на то что описанный пример относится к устройствам передачи, управляющим четырьмя маяками, при использовании различных электронных устройств (например,демультиплексора с большим числом выходов) можно управлять большим числом маяков. Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20. 9

МПК / Метки

Метки: передачи, данных, устройство, железнодорожные, маяки

Код ссылки

<a href="https://by.patents.su/9-13301-ustrojjstvo-dlya-peredachi-dannyh-na-zheleznodorozhnye-mayaki.html" rel="bookmark" title="База патентов Беларуси">Устройство для передачи данных на железнодорожные маяки</a>

Предыдущий патент: Способ обследования больной с маточными ациклическими кровотечениями для диагностики опухолевой патологии эндометрия

Следующий патент: Способ отопления лестничного помещения

Случайный патент: Терочное устройство к зерноуборочному комбайну