Запоминающее устройство

Текст

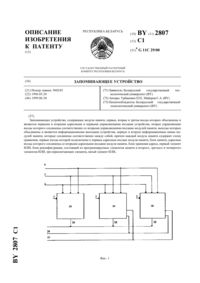

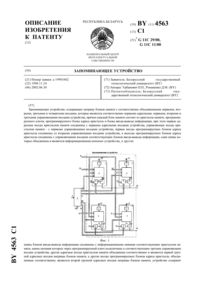

(12) НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ(71) Заявитель Закрытое акционерное общество БелХард Групп(73) Патентообладатель Закрытое акционерное общество БелХард Групп(57) 1. Запоминающее устройство, содержащее адресные блоки, аналоговые сумматоры, матрицу элементов памяти и блоки считывания, входы которых подключены через общую разрядную шину к выходам элементов памяти, одни входы которых присоединены к соответствующим адресным шинам строк, а другие входы подключены к соответствующим адресным шинам столбцов, причем каждая адресная шина присоединена к выходу соответствующего аналогового сумматора, а входы аналоговых сумматоров подключены к выходам адресных блоков, причем каждый адресный блок содержит первый и второй адресные дешифраторы, генератор и две группы ключевых элементов, первые входы которых в каждой группе соединены между собой, а вторые входы первой группы ключевых элементов присоединены к соответствующим выходам первого адресного дешифратора, а выходы второго адресного дешифратора подключены к соответствующим вторым входам ключевых элементов второй группы, а каждый элемент памяти содержит последовательно соединенные согласующий элемент и ключ, управляющий вход которого подключен к выходу триггера, отличающееся тем, что блок считывания содержит синхронный детектор, выход которого соединен со входом фильтра нижних частот, выход которого подключен ко входу порогового элемента, а сигнальный вход синхронного детектора является входом блока считывания, который подключен через общую разрядную шину к выходам элементов памяти, а опорный вход синхронного детектора каждого блока считывания присоединен к дополнительному выходу соответствующего адресного блока, причем каждый адресный блок содержит генератор гармонических колебаний, выходные клеммы которого подключены ко входу блока фильтрации, одна выходная клемма которого присоединена к первым входам ключевых элементов первой группы, а другая выходная клемма подключена к первым входам ключевых элементов второй группы, причем выходные клеммы блока фильтрации подключены ко входу фазовращателя, выход которого является дополнительным выходом адресного блока, который подключен к опорному входу синхронного детектора соответствующего блока считывания. 6542. Устройство по п. 1, отличающееся тем, что блок фильтрации содержит первый и второй последовательные колебательные контуры, причем каждый контур подключен между одной выходной клеммой генератора гармонических колебаний и одной выходной клеммой блока фильтрации, а резонансная частота каждого контура равна частоте генератора в данном адресном блоке, а значения частот генераторов в разных адресных блоках не равны между собой. 3. Устройство по п. 1, отличающееся тем, что величина фазового сдвига, вносимого фазовращателем на частоте генератора в каждом адресном блоке, выбрана равной суммарному фазовому сдвигу, вносимому последовательно соединенными ключевым элементом, аналоговым сумматором и элементом памяти на этой же частоте. 4. Устройство по п. 1 или 2, отличающееся тем, что согласующий элемент представляет собой дифференциальный усилитель, входное сопротивление которого по крайней мере на порядок меньше сопротивления любого последовательного колебательного контура вне его полосы пропускания, а значения частот генераторов гармонических колебаний в соседних адресных блоках отличаются между собой на величину,большую средней полосы пропускания двух последовательных колебательных контуров в этих адресных блоках.(56) 1. Гольденберг Л.М. и др. Цифровые устройства на интегральных схемах в технике связи. - М. Связь, 1979. С. 101. 2. Самохвалов К.Г. и др. Цифровые электронные вычислительные машины. Издание второе. - Киев Вища школа, 1983. - С. 218, рис. 4.37. 3. А.с. СССР 905857, 11 11/00 от 1980 г., опубликовано 15.02.82. Бюллетень 6 (прототип). 4. Баскаков С.И. Радиотехнические цепи и сигналы Учебник. - М. Высшая школа, 1983. - С. 288. 5. Белоцерковский Г.Б. Основы радиотехники и антенны. Часть 1. - М. Сов.радио, 1968. - С. 244-246. Предлагаемое устройство относится к области вычислительной техники, а точнее к полупроводниковым запоминающим устройствам и может быть использовано, например, в качестве полупроводниковой микросхемы постоянного запоминающего устройства в составе системного блока компьютера. Известно запоминающее устройство, содержащее двухкоординатную матрицу запоминающих элементов,блок адреса с дешифраторами адресов строки и столбца и адресными формирователями сигналов и блок считывания информации. При поступлении на дешифраторы кода адреса определенного запоминающего элемента возбуждаются соответствующие выходные шины дешифраторов и с помощью адресных шин по двум координатам выбирается данный запоминающий элемент, с которого по общей для всех элементов разрядной шине считывается его состояние 1. Указанное устройство обеспечивает обращение к матрице запоминающих элементов только по одному адресу. Одновременно обращаться и считывать информацию независимо с двух и более запоминающих элементов одной матрицы невозможно. Таким образом, общее время выборки по разным адресам определяется суммой времен выборки информации по каждому адресу отдельно. Известно запоминающее устройство с тремя независимыми каналами обращения при чтении цифровой информации 2. Устройство содержит три регистра адреса и три регистра слова. Благодаря наличию трех регистров возможно одновременное чтение слов по независимым адресам, за счет чего эффективное быстродействие запоминающего устройства в два или три раза выше фактического. Однако в данном устройстве одновременное считывание информации возможно только при обращении по независимым адресам к отдельным регистрам памяти. Фактически поле памяти разделено на отдельные информационные полярегистры, имеющие независимые адресные входы и выходы для чтения информации. Обращаться одновременно по нескольким каналам с любым адресом к общему полю памяти и независимо считывать информацию в устройстве невозможно. Наиболее близким по технической сущности является известное запоминающее устройство, содержащее адресные блоки, аналоговые сумматоры, матрицу элементов памяти и блоки считывания, входы которых подключены через общую разрядную шину к выходам элементов памяти, одни входы которых присоединены к соответствующим адресным шинам строк, а другие входы подключены к соответствующим адресным шинам столбцов, причем каждая адресная шина присоединена к выходу соответствующего аналогового сумматора, а входы аналоговых сумматоров подключены к выходам адресных блоков, причем каждый адресный блок содержит первый и второй адресные дешифраторы, генератор и две группы ключевых элементов, первые входы которых в каждой группе соединены между собой, а вторые входы первой группы ключевых элементов присоединены к соответствующим выходам первого адресного дешифратора, а выходы второго адресного дешифратора подключены к соответствующим вторым входам ключевых элементов второй группы, а каждый элемент памяти содержит последовательно соединенные согласующий элемент и 654 ключ, управляющий вход которого подключен к выходу триггера, а каждый блок считывания содержит последовательно соединенные полосовой фильтр и преобразователь напряжения 3. Известное устройство обеспечивает одновременное и независимое обращение по любым адресам с нескольких адресных блоков к общей матрице элементов памяти. Это достигается тем, что адресные блоки вырабатывают сигналы опроса элементов памяти по соответствующим шинам строк и столбцов в виде высокочастотных колебаний с различными значениями частот, а выделение сигналов считывания происходит за счет частотного разделения этих сигналов системой полосовых фильтров в блоках считывания. Каждому адресному блоку соответствует определенный блок считывания, полосовой фильтр которого пропускает сигналы с частотой генератора только данного адресного блока. Это позволяет одновременно обращаться к нескольким адресным блокам и считывать информацию независимо с нескольких элементов памяти общего поля памяти. Уменьшение общего времени выборки становится значительным при большом количестве одновременно опрашиваемых адресных блоков см. описание известного устройства по авт. свидетельству 905857. Однако известное устройство имеет два недостатка. Во первых, в каждом блоке считывания, содержащем последовательно соединенные полосовой фильтр и преобразователь напряжения происходит задержка информации,связанная с фильтрацией высокочастотных колебаний и преобразованием их в цифровые сигналы. Полосовой фильтр при выделении резонансной частоты вносит задержку, обусловленную временем установления выходного процесса на выходе частотно-избирательной системы, равную Т 4, 606 /, где Т - время установления выходного колебания до уровня 0, 9- эквивалентная добротность контура- резонансная частота контура 4. Для узкополосных фильтров, входящих в блок считывания при 100 задержка сигналов составляет примерно семьдесят периодов колебаний резонансной частоты. Реально при сигналах опроса на частотах 100-500 МГц эта задержка составляет 700-140 наносекунд соответственно. Такая задержка существенно увеличивает время опроса при одновременном обращении и независимом считывании информации с помощью системы узкополосных фильтров. Большое время установления при фильтрации сигналов опроса, а также дополнительная задержка при выпрямлении сигналов снижает в целом быстродействие запоминающего устройства, что является его недостатком. Другим недостатком известного устройства является возможность ошибки при одновременном считывании информации с элементов памяти, расположенных в одной строке общей матрицы. Действительно, при опросе элемента памяти 4 сигнал генератора 12 в виде однополярных импульсов с выхода 10 оказывается приложен к одной адресной шине строки 3 на фигуре описания авт. свидетельства 905857 верхняя и соответственно к одним выводам всех согласующих элементов 13, расположенных в этом горизонтальном ряду. Отрицательный потенциал с выхода 11 этого же генератора 12 оказывается приложенным через адресную шину столбца 3 к другим выводам согласующих элементов 13, расположенных в вертикальном ряду на фигуре крайние слева. Если одновременно опрашивается второй элемент памяти 4, расположенный в верхней строке, например справа от первого, то сигнал положительной полярности с выхода 10 генератора 12 также проходит и через его согласующий элемент 13, другой выход которого оказывается через другую адресную шину столбца 3 на фиг. вторая слева подключен к отрицательному потенциалу на выходе 11 генератора 12 другого адресного блока 1. Таким образом, при опросе двух и более элементов памяти 4 одной строки через их согласующие элементы 13 одновременно проходят сигналы со всех генераторов 12 адресных блоков 1, поскольку другие выводы этих элементов 13 через вторые выходы всех генераторов 12 оказываются присоединены к одному потенциалу. Это вызывает считывание ложной информации и соответственно снижает надежность работы всего устройства. Таким образом, в известном устройстве не достигается максимально возможное быстродействие из-за неизбежных задержек при фильтрации выходных сигналов и не обеспечивается надежность при считывании информации. Задача предлагаемого запоминающего устройства заключается в обеспечении более высокого быстродействия и надежности работы при считывании информации по сравнению с известным устройством при сохранении всех его функций. Технический результат при реализации предлагаемого устройства заключается в получении более высокого быстродействия за счет уменьшения времени обращения и повышения надежности при считывании информации. Указанный технический результат достигается тем, что в запоминающем устройстве, содержащем адресные блоки, аналоговые сумматоры, матрицу элементов памяти и блоки считывания, входы которых подключены через общую разрядную шину к выходам элементов памяти, одни входы которых присоединены к соответствующим адресным шинам строк, а другие входы подключены к соответствующим адресным шинам столбцов, причем каждая адресная шина присоединена к выходу соответствующего аналогового сумматора,а входы аналоговых сумматоров подключены к выходам адресных блоков, причем каждый адресный блок содержит первый и второй адресные дешифраторы, генератор и две группы ключевых элементов, первые входы которых в каждой группе соединены между собой, а вторые входы первой группы ключевых элементов присоединены к соответствующим выходам первого адресного дешифратора выходывторого адресного 3 654 дешифратора подключены к соответствующим вторым входам ключевых элементов второй группы, а каждый элемент памяти содержит последовательно соединенные согласующий элемент и ключ, управляющий вход которого подключен к выходу триггера, блок считывания содержит синхронный детектор, выход которого соединен со входом фильтра нижних частот, выход которого подключен ко входу порогового элемента,а сигнальный вход синхронного детектора является входом блока считывания, который подключен через общую разрядную шину к выходам элементов памяти, а опорный вход синхронного детектора каждого блока считывания присоединен к дополнительному выходу соответствующего адресного блока, причем каждый адресный блок содержит генератор гармонических колебаний, выходные клеммы которого подключены ко входу блока фильтрации, одна выходная клемма которого присоединена к первым входам ключевых элементов первой группы, а другая выходная клемма подключена к первым входам ключевых элементов второй группы, причем выходные клеммы блока фильтрации подключены ко входу фазовращателя, выход которого является дополнительным выходом адресного блока, который подключен к опорному входу синхронного детектора соответствующего блока считывания, а блок фильтрации содержит первый и второй последовательные колебательные контуры, причем каждый контур подключен между одной выходной клеммой генератора гармонических колебаний и одной выходной клеммой блока фильтрации, а резонансная частота каждого контура равна частоте генератора в данном адресном блоке, а значения частот генераторов в разных адресных блоках не равны между собой, причем величина фазового сдвига, вносимого фазовращателем на частоте генератора в каждом адресном блоке равна суммарному фазовому сдвигу, вносимому последовательно соединенными ключевым элементом, аналоговым сумматором и элементом памяти на этой частоте, а согласующий элемент представляет собой дифференциальный усилитель, входное сопротивление которого по крайней мере на порядок меньше сопротивления любого последовательного колебательного контура вне его полосы пропускания, а значения частот генераторов гармонических колебаний в соседних адресных блоках отличаются между собой на величину, большую средней полосы пропускания двух последовательных колебательных контуров в этих адресных блоках. На фиг. изображена схема предлагаемого запоминающего устройства. Обозначения на фиг.1 - адресный блок 2 - аналоговый сумматор 3 - матрица элементов памяти 4 блок считывания 5 - общая разрядная шина 6 - элемент памяти 7 - адресная шина строки 8 - адресная шина столбца 9 - первый адресный дешифратор 10 - второй адресный дешифратор 11 - генератор гармонических колебаний 12 - ключевой элемент 13 - согласующий элемент 14 - ключ 15 - триггер 16 - синхронный детектор 17 - фильтр нижних частот 18 - пороговый элемент 19 - дополнительный выход 20 - блок фильтрации 21 - одна выходная клемма блока фильтрации 22 - другая выходная клемма блока фильтрации 23 первый последовательный колебательный контур 24 - второй последовательный колебательный контур 25 фазовращатель. Запоминающее устройство содержит адресные блоки 1, аналоговые сумматоры 2, матрицу элементов памяти 3 и блоки считывания 4, входы которых подключены через общую разрядную шину 5 к выходам элементов памяти 6, одни входы которых присоединены к соответствующим адресным шинам строк 7, а другие входы подключены к соответствующим адресным шинам столбцов 8, причем каждая адресная шина 7 и 8 присоединена к выходу соответствующего аналогового сумматора 2, а входы аналоговых сумматоров 2 подключены к выходам адресных блоков 1, причем каждый адресный блок 1 содержит первый и второй адресные дешифраторы 9 и 10, генератор 11 и две группы ключевых элементов 12, первые входы которых в каждой группе соединены между собой, а вторые входы первой группы ключевых элементов 12 присоединены к соответствующим выходам первого адресного дешифратора 9, а выходы второго адресного дешифратора 10 подключены к соответствующим вторым входам ключевых элементов 12 второй группы, а каждый элемент памяти 6 содержит последовательно соединенные согласующий элемент 13 и ключ 14, управляющий вход которого подключен к выходу триггера 15, а блок считывания 4 содержит синхронный детектор 16, выход которого соединен со входом фильтра нижних частот 17, выход которого подключен ко входу порогового элемента 18, а сигнальный вход синхронного детектора 16 является входом блока считывания 4, который подключен через общую разрядную шину 5 к выходам элементов памяти 6, а опорный вход синхронного детектора 16 каждого блока считывания 4 присоединен к дополнительному выходу 19 соответствующего адресного блока 1, причем каждый адресный блок 1 содержит генератор гармонических колебаний 11, выходные клеммы которого подключены ко входу блока фильтрации 20, одна выходная клемма 21 которого присоединена к первым входам ключевых элементов 12 первой группы, а другая выходная клемма 22 подключена к первым входам ключевых элементов 12 второй группы, а блок фильтрации 20 содержит первый и второй последовательные колебательные контуры 23 и 24, причем каждый контур 23 и 24 подключен между одной и другой выходной клеммой генератора 11 и одной и другой выходной клеммой 21 и 22 блока фильтрации 20, а выходные клеммы 21 и 22 блока фильтрации 20 подключены ко входу фазовращателя 25, выход которого является дополнительным выходом 19 адресного блока 1, который подключен к опорному входу синхронного детектора 16 соответствующего блока считывания 4, а резонансная частота каждого контуры 23 и 24 равна частоте генератора 11 в данном адресном блоке 1, а значения частот генераторов 11 в разных адресных блоках 1 не равны между собой, причем величина фазового сдвига, вносимого фазовращателем 25 4 654 на частоте генератора 11 в каждом адресном блоке 1 равна суммарному фазовому сдвигу, вносимому последовательно соединенными ключевым элементом 12, аналоговым сумматором 2 и элементом памяти 6 на этой же частоте, а согласующий элемент 13 представляет собой дифференциальный усилитель, входное сопротивление которого по крайней мере на порядок меньше сопротивления любого последовательного колебательного контура 23 и 24 вне его полосы пропускания, а значения частот генераторов гармонических колебаний 11 в соседних адресных блоках 1 отличаются между собой на величину, большую средней полосы пропускания двух последовательных колебательных контуров 23 и 24 в этих адресных блоках 1. Работа предлагаемого запоминающего устройства заключается в следующем. Устройство имеет несколько независимых каналов обращения к общей матрице элементов памяти 3 и столько же независимых выходов для считывания информации. Количество каналов обращения равно числу адресных блоков 1. Входом каждого канала являются входы первого и второго адресных дешифраторов строк и столбцов 9 и 10, а независимыми выходами устройства являются выходы пороговых элементов 18 в каждом блоке считывания 4. Количество блоков считывания 4 равно числу адресных блоков 1, причем каждому каналу обращения с определенным адресным блоком 1 соответствует независимый выход в том блоке считывания 4, который подключен к его дополнительному выходу 19. Обращение к матрице элементов памяти 3 происходит при подаче цифровых кодов адреса строки и столбца нужного элемента памяти 6 на вход адресного блока 1, а считывание информации в виде логической 1 или 0 происходит на выходе соответствующего блока считывания 4. В устройстве обеспечивается одновременное обращение по любому каналу с любым адресом к общей матрице элементов памяти 3 и независимое считывание информации на соответствующем выходе блока считывания 4. Рассмотрим работу устройства более подробно. При включении электропитания все генераторы гармонических колебаний 11 в каждом адресном блоке 1 начинают вырабатывать высокочастотные сигналы, которые с выхода каждого генератора 11 через колебательные контуры 23 и 24 оказываются на клеммах 21 и 22 блока фильтрации 20, с которых сигнал поступает и на первые входы ключевых элементов 12 первой и второй группы. Одновременно эти сигналы через фазовращатель 25 с дополнительного выхода 19 каждого адресного блока 1 поступают на дополнительные входы синхронных детекторов 16 соответствующих блоков считывания 4. Код адреса опрашиваемого элемента памяти 6 поступает на входы адресного блока 1, при этом код адреса строки поступает на входы первого дешифратора 9,а код адреса столбца - на входы второго дешифратора 10. На выходах этих дешифраторов 9 и 10 появляются логические сигналы, которые поступают на вторые входы соответствующих ключевых элементов 12, на первые входы поступает сигнал с выхода генератора 11. Логические сигналы с выходов дешифраторов 9 и 10 являются разрешающими для ключевых элементов 12, на которые они поступают, и гармонический сигнал генератора 11 оказывается приложенным между входами аналоговых сумматоров 2 разных координат, подключенных к выходам открытых ключевых элементов 12. Каждый аналоговый сумматор 2 обеспечивает передачу высокочастотных сигналов с любого входа на общий выход, при этом обеспечивается развязка входных сигналов. Таким образом, при подаче кода адреса опрашиваемого элемента памяти 6, гармонический сигнал определенной частоты с выхода генератора 11 через последовательные контуры 23 и 24, открытые ключевые элементы 12, аналоговые сумматоры 2 и подключенные к ним адресные шины строки 7 и столбца 8 оказывается приложенным ко двум входам согласующего элемента 13 опрашиваемого элемента памяти 6. С выхода согласующего элемента 13, в качестве которого использован дифференциальный усилитель, сигнал поступает на вход ключа 14. Состоянием ключа 14 - открыт или закрыт - управляет триггер 15, который хранит 1 Бит информации в данной ячейке памяти. Если триггер 15 находится в единичном состоянии, то сигнал с триггера 15 поступает на ключ 14 и держит его в открытом состоянии. В этом случае гармонический сигнал с выхода согласующего элемента 13 через открытый ключ 14 поступает на общую разрядную шину 5, с выхода которой передается на входы блоков считывания 4. Определение гармонического сигнала считывания заданной частоты происходит за счет частотной избирательности синхронных детекторов 16 в блоках считывания 4, подключенных к общей шине 5. На опорный вход каждого синхронного детектора 16 непрерывно поступает гармонический сигнал с частотой генератора 11 соответствующего адресного блока 1. При появлении на сигнальном входе синхронного детектора 16 синфазного когерентного сигнала на его выходе выделяется постоянная и переменная составляющие 5. Постоянная составляющая оказывается равна 1/2 у, при 1,где- постоянная составляющая тока на выходе синхронного детектора 16 -го блока считывания 4- амплитуда высокочастотного сигнала опроса на входе синхронного детектора 16- фазовый сдвиг между напряжением сигналаи опорным сигналом на входах синхронного детектора 16- постоянный коэффициент, определяемый параметрами синхронного детектора 161 - число адресных блоков. Фильтр нижних частот 17, подключенный к синхронному детектору 16 не пропускает на выход переменные составляющие тока, поэтому выпрямленный ток формирует на выходе постоянное напряжение, которое поступает на вход порогового элемента 18. Пороговый элемент 18 сработывает и на его выходе формируется сигнал логической 1, соответствующий состоянию опрашиваемого элемента памяти 6. 654 Для обеспечения максимального значения постоянной составляющей тока на выходе синхронного детектора 16 необходима синфазность опорного и входного сигналов, т.е. у 0. В устройстве это достигается введением фазовращателя 25 в цепь опорного сигнала каждого генератора 11 и выбором величины фазового сдвига, равного суммарному фазовому сдвигу, вносимому в цепи опроса, последовательно соединенными ключевым элементом 12, аналоговым сумматором 2, элементом памяти 6, причем это должно обеспечиваться на частоте генератора 11 в каждом адресном блоке 1. При этом обеспечиваетсяу 1, выпрямленный ток максимален и напряжение на выходе фильтра 17 обеспечивает срабатывание порогового элемента 18. Если триггер 15 элемента памяти 6 находится в нулевом состоянии, то ключ 14 закрыт, гармонический сигнал опроса с его выхода в общую разрядную шину 5 не поступает, на выходе соответствующего блока считывания 4 сохраняется состояние логического 0, что соответствует состоянию опрашиваемого элемента памяти 6. Аналогичным образом происходит опрос и считывание информации с матрицы элементов памяти 3 другими адресными блоками 1.их входы поступают коды адресов элементов памяти 6, а через фиксированное время на выходах соответствующих блоков считывания 4 появляется хранимая информация в виде логических 1 или 0. Использование в устройстве в качестве сигналов опроса гармонических колебаний и их частотное разделение в блоках считывания 4 позволяет одновременно обращаться ко всем адресным блокам 1 по любым адресам и независимо считывать информацию с общей матрицы элементов памяти 3. При этом суммарное время выборки при всех одновременно опрашиваемых адресных блоков 1 равно времени обращения по одному адресу. Технический результат в предлагаемом устройстве достигается следующим образом. Каждый блок считывания 4 содержит синхронный детектор 16 опорный вход которого соединен с выходом генератора 11 соответствующего адресного блока 1, а сигнальный вход подключен к общей разрядной шине 5. При работе устройства каждый синхронный детектор 16 обеспечивает частотную избирательность сигналов опроса и их преобразование в постоянный сигнал с минимальной задержкой, т.к. время установления выходного процесса на его выходе принципиально меньше, чем на выходе узкополосного фильтра в известном устройстве. Фактически, время установления на выходе синхронного детектора 16 определяется быстродействием его активного элемента. Выпрямленный ток с выхода синхронного детектора 16 поступает на вход фильтра нижних частот 17, формируя на его выходе напряжение срабатывания для порогового элемента 18. Время формирования этого напряжения определяется постоянной времени этого фильтра 17 и соизмеримо с периодом входных колебаний. Таким образом, в предлагаемом устройстве время задержки сигнала опроса в блоке считывания 4, связанное с его фильтрацией и детектированием не превышает несколько периодов входных колебаний, что существенно меньше, чем в известном устройстве. Например, для частоты опроса элементов памяти 6, равной 500 МГц, время обращения в предлагаемом устройстве уменьшается более чем на 100 наносекунд по сравнению с известным устройством. Это обеспечивает более высокое быстродействие предлагаемого устройства. В известном устройстве по авт.свид.905857 при опросе двух и более элементов памяти одной строки через входные выводы их согласующих элементов могут одновременно проходить паразитные высокочастотные сигналы с выходной клеммы одного генератора к выходной клемме другого генератора разных адресных блоков, поскольку их выходные напряжения привязаны к потенциалу схемной земли, а при подключении к общей нагрузке между выходами генераторов не обеспечена развязка от взаимных сигналов. Это вызывает считывание ложной информации. В предлагаемом устройстве технический результат - повышение надежности - устраняет указанный недостаток. Для этого в устройстве каждый адресный блок 1 содержит блок фильтрации 20, состоящий из двух последовательных колебательных контуров 23 и 24, подключенных к выходным клеммам генераторов 11. Резонансная частота каждого контура 23 и 24 равна частоте генератора 11 в данном адресном блоке 1, а значения частот генераторов 11 не равны между собой и в соседних адресных блоках 1 отличаются между собой на величину, большую средней полосы пропускания контуров в этих соседних адресных блоках 1. Кроме того, в качестве согласующего элемента 13 использован дифференциальный усилитель, входное сопротивление которого более чем в десять раз меньше, чем сопротивление колебательного контура 23 или 24 вне его полосы пропускания. Указанное обеспечивает развязку для паразитных сигналов между входами разных генераторов 11 при их коммутации на общие адресные шины 7 и 8, поскольку сигнал с выходной клеммы одного генератора 11 проходит через относительно малое входное сопротивление согласующего элемента 13 и относительно большое сопротивление колебательного контура 23 и 24 к клемме другого генератора 11. Указанное обеспечивает такое деление паразитного сигнала, при котором на входах согласующего элемента 13 он практически отсутствует и на выход элемента 13 не поступает. Например, при опросе элемента памяти 6 сигнал с выхода генератора 11 без затуханий проходит через контуры 23 и 24, т.к. на резонансной частоте их сопротивление практически равно нулю, и далее через ключевые элементы 12 и аналоговые сумматоры 2 полностью оказывается приложенным ко входам согласующего элемента 13 нужного элемента памяти 6, с выхода которого сигнал считывания поступает на вход ключа 14 и т.д. Для гармонических сигналов опроса от других генераторов 11 эти контуры 23 и 24 вносят 6 654 существенные затухания, поскольку частоты всех других генераторов 11 лежат за пределами полосы пропускания этих контуров и паразитные сигналы не проходят через выводы выбранного согласующего элемента 13. Тем самым в предлагаемом устройстве обеспечивается надежность считывания информации при одновременном обращении по любым адресам. Национальный центр интеллектуальной собственности. 220072, г. Минск, проспект Ф. Скорины, 66.

МПК / Метки

МПК: G11C 11/00

Метки: запоминающее, устройство

Код ссылки

<a href="https://by.patents.su/7-u654-zapominayushhee-ustrojjstvo.html" rel="bookmark" title="База патентов Беларуси">Запоминающее устройство</a>

Предыдущий патент: Способ изготовления электрохимической ячейки и электрохимическая ячейка

Следующий патент: Коробка для сигарет

Случайный патент: Способ стимулирования половой охоты у самок крупного рогатого скота