Накопитель электрически программируемого постоянного запоминающего устройства

Номер патента: 742

Опубликовано: 30.06.1995

Авторы: Борисенок А. Н., Лозицкий Е. Г., Сорока С. А., Алиева Н. В.

Текст

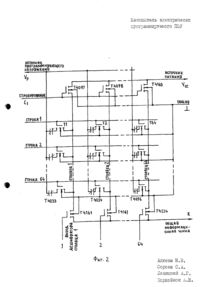

/ Накопитель элеитрнчасни программируемого ПЗУИзобретение этнэсится к области элснтрсннсй техники И может быть нспэльзсванс при нэнструирсванин интегральных схем.Известен накснитснь элснгршчасдн прсграмжшруемсга да К 1) вьдючаюннй матрицу ЩДП транзнстсрсв В стэхсвую цепь каждого рна налънэгс транзистора включена плавкая пслннрамниаван перемычка,сэсцннсннан через разрядную шину с цешнфратэрсм стслбцсв, пэлшаремнн сана затворы нанцсгс транзистора соединены с адресной шиной цаннэн страна, которая, в сваю очередь , поднлшчена н дешифратору сгрэнн . Известная нснструшша обладает слснурэцнглн нацостаткаглн . слэнаосгь ранима прсграммирзваннн, требуются бэнашие импульсы напрнненна с амплитудой примерно 30 В для пслучанна тона, дсста тсчнсгэ для псрсннгання перемычкиаванса снстрсдатствне сбуслэвлсннсе болъшса мкостью адресных И разрядных шва.Известна нахэпнтадь электрически программпруамсгс ПЗУ ( 8). нщючатлщин матрицу вертикальных биполярных транзисторов , в эмнттнрную лань натдэгс бипслнрнэгс транзистора включена плавкая пэлпкрамнисвая перемычка, соединенная через разрядную шнну с дешнфратсрсм стслбцэв саванна эсластн наннсгс бнпслнрнсгс транзисгора сэенннанн пэлннрамннавэй адресной шанса С дашнфратсрсн строк.Известная нснструшшя обладает сдтацующшчяш недостатками . сланнэстъ ранима нрсграммнрованнн для расплавления ( псрвжн ганнн) рслннрамннавсн псрамнчаш требуются большие величины напрнч анннн н такса,- низкая снэрссть нрсграмннрснания эграннчанная временем псрачич гання плавких пэрамнчсн,- нкзнэе быстрсденствне сбусловланнсасбсдьшсн мкостью адресных Ш разрядных шнн .Нанбслаа близким тсхннчасанм решением 1 изобретению является нансднтелъ электрически нрэграммнруансгс псстонннсгс запэмпнающсгз устройства ( 3 )сснэванннн на прсбса диэлектрика, ссдсраашии запоминающие ячейки. распслоааннна В вндэ матрацы, ванная аз котср рнх сэцержнт ЫДП транзистор И нсннансатср с изолнрующнм слезы,включенный посладсваталънс В стэхсвун область транзистора,чатпппп тпапэнптпппр епсннчанн О ЗПВВСНО ШЕНО данной строки, 2степи мДП- транзисторов поддлюченн н одной не обкладок конденсатора, вторые обкладки конденсаторов подплюченн к соответствующим столбцам.Известная конструкция обладает слецующнн недостаткам н низкое быстродействие, обусловленное мкостью рп перехода стока под разрядной иной, все раоряднне шннн находятся под высоким потенциалом . ы сложность в програмшрованпн. все схемы управления програмирова нпомцолннн работать при напряжении 12 В. при рабочем напряжении схемы 5 В. что существенно усложняет конотргтидю охоты.св основу изобретения положена задача упрощения программирования п повышения быстродействия за счет уменьшения мкости разрядных инн Существо изобретения заключается в том. что внаопптеле элентрпческв программируемого постоянного запоминающего устройства,содержащего запоминающие ячейки, расположенные в виде матрица. паяная но потерпи содержит ЫЦП 1- транзистор и конденсатор с неолирующим споем. затвора транепсторовооецнненп с адресной шиной данной строки, столп транзисторов подключены к разрядной шине данного столбца, одна не обкладок паяного конденсатора соединена с истоком соответствующего транзистора, другие обкладки конденсаторов объедпч ненн и подиивчепв и шине.программ 1 рУШщего напряжения.Сущность изобретения заключается в том, что стони транзисторов каждого столбца подключена к разрядной шине этого столбца. одна по ссыпано паяного ноняенсатора подключена н потопу соответствующего транзистора. а вторне ооипапин конденсаторов объединены и подключены к шине програниирующсго напрянения. В иообретени используется одна разрядная шина на две ячейки, т.е. две соседние ячейки имеет общин степ. Использование одной разрядной шины на две ячейки накопителя позволяет уменъшить в 2 раса мкость разрядной шины за счет уменьшения диффузионной мкости рпперехопа и повысить быстродействие схемы. Для упрощения режима программирования исполъ суется отдельный источник програмипрующего напряяения н которому через шину програмиирушщего напряжения подилюченн вторые обкпадпн конденсаторов. а все цепи схемы работают при стандартном напряжении питания 53 высокий потенгшал (а 12 В) подается только на шипа программирувщаго напряжения. В момент программирования на всех разрядных шинах н схемах обрамления стандартное напряпенпе питания ( 5 В). изложенная сущность поясняется фиг.1.2 где на фиг. 1 изображена электрическая схема построения накопителя электрически програшируемого ПЗУ. на фнг.2 электрическая схема органиоапи накопителя ППЗУ емкостью 4 К 1 1 бит. Накопитель ( фпг.1) вклвчает матрицупо па строк 1 и 11 столбцов 2 МДД транзисторов, к каждому из которых последовательно подключен программируемый пробоем конденсатор 3 от адресных шин, подключении к деширатору строк, п /2 разрядных шин, подключенных к дешифратору столбцов. затвора транзисторов,расположенных в пандой строке, соединена с адресной шиной данной строки 1. Стоки транзисторов каждого столбца 4 подключена к раврядпой шине 2 этого столбца одна из обкладок каждого конденсатора 5 подключена к потопу соответствующего транзистора , а вторве обкладки конденсаторов 6 объединена и подключена к шпнеарпрограм мирупщего папрявенпядт).Ь состоянии до программирования полпиремннэвнй электрод 6( вторая обкладка конденсаторов) изолирован от диффузионного слоя щи транзистора в области потока транзистора тонким слоем шелектри ка . В процессе программирования ячейки к поликремниевому электроду прилагаем импульс напряжения, происходит пробой изоляторе. п полпиремпиевви электрод соединяется с диффузионным слоем, ячейка запрограммирована.Для выбора ячейки из накопителя при программировании используются трп шина адресная, разрядная п шина програмирувщего напряжения. Адресная шина объединяет затвора транзисторов, расположенввк в каждой строке, и подключает их и дешифратору строк. Разрядная шипа объединяет стоки транзисторов располоиепннк в наидом столбце . И подключает их к дом ПФРатору столбцов. Причем на два соседних столбца транзисторов используется одна разрядная шине.Шиве программируещего напряжения объединяет второе совладал програмонруемях конденсаторов п подключает их к источнику програмпш- . рувщего.напрянени. В режиме программирования на выбранную спомощью адресной и разрядной шин ячейку подают по шине программируощего напряжения высокое программмрувщее напряжение от отдельного источника питания. достаточное для пробоя коидевоаторного диэлектрика в цепи истока транвпстораВсе остальные схемы управления програмированием работают при стандартном напряжении питания.Это дат возможность упростить схему управления программированием.А такие. снижает ещ больше мкость раорядннивв шин п поввшает быстродействие . т.и. в режиме программровавия на разрядив шинах во бывает высокого потенциала ( меньше диффузионные мкости рппере ходов). Использование программируемого конденсатора в цепи истока транзистора позволяет значительно упростить решим программирования схемы, так как только на шинах программрувщего напряжения будетЭтот потениал формируется источником программирующего напряжения. А на всей остальной ехеме будет стандартное напряжение питания.Рассмотрим для примера организацию накопителя НЕЕ емкостью аи х 1 бит ( фиг.2). Т Накопитель состоит из 4096 вапомнавщих или транзисторов, исток каждого из которых соединен е запоминающим иоиденоатором. а вторые обкладки вое запоминающих конденсаторов объединена и внвеиеиа на Отделъную площади . 64 отроги накопителя иоиилочеин и выходам Дешифратора отрок. работающего при напряжении питанияс 5 В. 64 выхода Дешифратора столбцов ( работающего при с 5 В управляот ключевыми транзисторами Т 4161 Т 4224, которые ооущеотвляот связь отолбцовн шин е общей информационной шиной . Траивиаторн Т 4097 - Т 4160 иоиольвуотоя в качестве отрооируемои оигналом-61 нагргдщ . при-считывании информации площадка Уф заворачивается е шиной земли. при подаче адресного сигнала дешифратора строки и.отолбца ооущеотвлиют виоориу оапоыииаощеи ячеиии,то есть наодиом из выходов дешифраторои отроги и столбца устанавливаетои внооиий уровень 5 В. Все транзисторе внбраииои строки переводитоя в проводящее еоотояаие. В том олучае. если запоминающий конденсатор, вилоиеиини поеледователъио о транзистором. ааирограмирован С пробит конденсаторной диэлектрик), то отирнтал цепь разряда мкости отолоцовой разрядной шин на таило и на ней будет устанавливаться низиии уровеиъ. В том олучае еоли запоминающий конденсатор не запрограммирован, то поолеиователъная цепь транзистор-конденсатор закрыта. и на отолбцовои шине сохранится вне Еда потендал который будет полдерииватъоя соответствующими транзисторами Т 409 Т 4160, иопольеуемниш е качестве внооиоомной нагрузки. Информация, установившаяся на отолбце через оиин ив траивиоторов Т 4161 4224. на который подается из Дешифратора отолбцов отпиравщии иотеншалпоотупает на общую информационную шину и подается через усилитель считывании на вниодиой буфер. Вреииые программирования в начале на площадку ЮЪ подается уровень питании микросхемы 5 В. При подаче адресного сигнала Дешифратора отроии И столбца ооуществлявт выборку строки и отолбца. Записываемая информации подается от входной площадки на общую информациондую шину Ж и через выбранной иешифратором столбцов один из транзисторов Т 4161 4224 на внераиний столбец. 8 атем.провоиитоя импульсное повншение.наиряиения на площадке Ь до уровня 12 14 В, превоохоиящегонапряжение пробоя диэлектрика запоминающего конденсатора.

МПК / Метки

МПК: G11C 17/04

Метки: программируемого, устройства, электрически, постоянного, запоминающего, накопитель

Код ссылки

<a href="https://by.patents.su/7-742-nakopitel-elektricheski-programmiruemogo-postoyannogo-zapominayushhego-ustrojjstva.html" rel="bookmark" title="База патентов Беларуси">Накопитель электрически программируемого постоянного запоминающего устройства</a>

Предыдущий патент: Способ устройства армирующего слоя дорожной одежды

Следующий патент: Способ газолазерной резки

Случайный патент: Лазер с внешним кольцевым волоконным резонатором