Вычислительное устройство по модулю три

Номер патента: 12201

Опубликовано: 30.08.2009

Авторы: ГОРОДЕЦКИЙ Данила Андреевич, Супрун Валерий Павлович

Текст

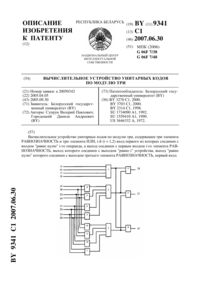

(51) МПК (2006) НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ПО МОДУЛЮ ТРИ(71) Заявитель Белорусский государственный университет(72) Авторы Супрун Валерий Павлович Городецкий Данила Андреевич(73) Патентообладатель Белорусский государственный университет(57) Вычислительное устройство по модулю три, характеризующееся тем, что содержит четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, -й, где 1, 2, вход первого элемента из которых соединен с входом младшего разряда -го операнда устройства, вход старшего разряда которого соединен с -м входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, и два элемента РАВНОЗНАЧНОСТЬ, выход первого из которых соединен с выходом младшего разряда устройства, выход старшего разряда которого соединен с выходом второго элемента РАВНОЗНАЧНОСТЬ, первый инверсный вход которого соединен с первым инверсным входом первого элемента РАВНОЗНАЧНОСТЬ и с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, третий и четвертый входы которого соединены с входом старшего разряда первого операнда устройства, а пятый и шестой входы соединены с входом старшего разряда второго операнда устройства, вход младшего разряда которого соединен с третьим и четвертым входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, пятый и шестой входы которого соединены с входом младшего разряда первого операнда устройства, а выход соединен с первым прямым входом -го элемента РАВНОЗНАЧНОСТЬ, причем второй прямой вход второго элемента РАВНОЗНАЧНОСТЬ соединен со вторым инверсным входом первого элемента 12201 1 2009.08.30 РАВНОЗНАЧНОСТЬ и с выходом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, -й вход которого соединен с -м входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с входом младшего разряда (2)-го операнда устройства, вход старшего разряда которого соединен с (2)-м входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с (2)-м входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, (4)-й вход которого соединен с входом старшего разряда (2)-го операнда устройства, вход младшего разряда которого соединен с (4)-м входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, выход которого соединен со вторым прямым входом первого элемента РАВНОЗНАЧНОСТЬ и со вторым инверсным входом второго элемента РАВНОЗНАЧНОСТЬ. Изобретение относится к области вычислительной техники и автоматики и может быть использовано для построения систем передачи и переработки дискретной информации. Известен сумматор по модулю три, содержащий четыре элемента РАВНОЗНАЧНОСТЬ, четыре входа и два выхода 1. Недостатком известного сумматора по модулю три являются низкие функциональные возможности. Наиболее близким по конструкции и функциональным возможностям техническим решением к предлагаемому является сумматор по модулю три, содержащий мажоритарный элемент с порогом два, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, четыре входа и два выхода 2. Сложность сумматора (по числу входов логических элементов) равна 10, а его быстродействие, определяемое глубиной схемы, составляет 2, где- усредненная задержка на один логический элемент. Недостатком сумматора по модулю три являются низкие функциональные возможности, поскольку сумматор не реализует операцию (АВ)(С) ( 3). Изобретение направлено на решение технической задачи расширения функциональных возможностей сумматора по модулю три за счет реализации арифметической операции (АВ)(С) ( 3). Вычислительное устройство по модулю три характеризуется тем, что содержит четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, -й (1, 2) вход первого элемента из которых соединен с входом младшего разряда -го операнда устройства, вход старшего разряда которого соединен с -м входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, и два элемента РАВНОЗНАЧНОСТЬ. Выход первого элемента РАВНОЗНАЧНОСТЬ соединен с выходом младшего разряда устройства, выход старшего разряда которого соединен с выходом второго элемента РАВНОЗНАЧНОСТЬ, первый инверсный вход которого соединен с первым инверсным входом первого элемента РАВНОЗНАЧНОСТЬ и с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два. Третий и четвертый входы первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два соединены с входом старшего разряда первого операнда устройства, а пятый и шестой входы соединены с входом старшего разряда второго операнда устройства, вход младшего разряда которого соединен с третьим и четвертым входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, пятый и шестой входы которого соединены с входом младшего разряда первого операнда устройства, а выход соединен с первым прямым входом -го элемента РАВНОЗНАЧНОСТЬ. Второй прямой вход второго элемента РАВНОЗНАЧНОСТЬ соединен со вторым инверсным входом первого элемента РАВНОЗНАЧНОСТЬ и с выходом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, -й вход которого соединен с -м входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с входом младшего разряда (2)-го операнда устройства. 2 12201 1 2009.08.30 Вход старшего разряда (2)-го операнда устройства соединен с (2)-м входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с (2)-м входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, (4)-й вход которого соединен с входом старшего разряда (2)-го операнда устройства. Вход младшего разряда (2)-го операнда устройства соединен с (4)-м входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, выход которого соединен со вторым прямым входом первого элемента РАВНОЗНАЧНОСТЬ и со вторым инверсным входом второго элемента РАВНОЗНАЧНОСТЬ. На чертеже (фигура) представлена схема вычислительного устройства по модулю три. Вычислительное устройство по модулю три содержит четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два 1, 2, 3 и 4, два элемента РАВНОЗНАЧНОСТЬ 5 и 6, восемь входов 7, 8, , 14 и два выхода 15 и 16. Операнды А, В, С изадаются двухразрядными двоичными кодами(1, 2),(, 2), С(с 1, с 2),(1, 2), где , , ,- младшие разряды 2, 2, 2, 2 - старшие разряды операндов А, В, С и , т.е. Аа 12 а 2,122, Сс 12 с 2 и 122. В соответствии с выбранным модулем Р 3 операнды могут принимать значения 0(00), 1 (01), 2 (10). Результат выполнения операции (АВ)(С) ( 3) задается двухразрядным двоичным кодом(1, 2), где 122. На входы 7, 9, 11 и 13 вычислительного устройства подаются значения младших разрядов , , 1,операндов, соответственно на входы 8, 10, 12 и 14 - значения старших разрядов 2, 2, 2, 2 операндов А, В, С исоответственно. На выходе 15 вычислительного устройства реализуется младший разряд 1, на выходе 16 - старший разряд 2 результата выполнения операции (АВ)(С) ( 3). Логическая схема вычислительного устройства по модулю три (фигура) синтезирована по следующим аналитическим представлениям функций 1 и 2 1, если(1 ,2 , 1 ,2 )(1 ,2 , 1 ,2 )(1 ,2 , 1 ,2 )(1 ,2 , 1 ,2 ) 10 в противном случае,1, если(1 ,2 , 1 ,2 )(1 ,2 , 1 ,2 )(1 ,2 , 1 ,2 )(1 ,2 , 1 ,2 ),20 в противном случае,где 1, если 2122122(1 ,2 , 1 ,2 )0 в противном случае, 1, если 12 212 22(1 ,2 , 1 ,2 )0 в противном случае,1, если 2122122(1 ,2 , 1 ,2 )0 в противном случае,1, если 12 212 22(1 ,2 , 1 ,2 )0 в противном случае,В таблице представлены логические функции 1 и 2, описывающие работу вычислительного устройства по модулю три. Основным достоинством вычислительного устройства по модулю три являются широкие функциональные возможности, поскольку устройство реализует операцию(АВ)(С) ( 3). Следует отметить, что быстродействие вычислительного устройства, определяемое глубиной схемы, совпадает с быстродействием устройства-прототипа. 12201 1 2009.08.30 ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ПО МОДУЛЮ ТРИ Входы Двоичный код Двоичный код Двоичный код первого операнда второго операнда третьего операн(2, 1) Выходы Двоичный код Двоичный код четвертого оперезультата ранда (2, 1) 12201 1 2009.08.30 Входы Выходы Двоичный код Двоичный код Двоичный код Двоичный код Двоичный код первого операнда второго операнда первого операнда второго операнда результата Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20. 5

МПК / Метки

МПК: G06F 7/38

Метки: модулю, три, устройство, вычислительное

Код ссылки

<a href="https://by.patents.su/5-12201-vychislitelnoe-ustrojjstvo-po-modulyu-tri.html" rel="bookmark" title="База патентов Беларуси">Вычислительное устройство по модулю три</a>

Предыдущий патент: Вычислительное устройство по модулю три

Следующий патент: Способ изготовления адгезивного протеза в области отсутствующего зуба

Случайный патент: Передача с гибкой связью