Устройство обработки нечеткой информации

Номер патента: U 127

Опубликовано: 30.06.2000

Авторы: Федоров Анатолий Юрьевич, Лисейчиков Николай Иванович, Кардаков Владимир Иванович

Текст

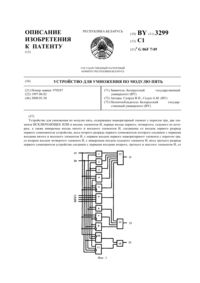

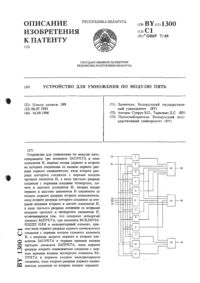

(12) ГОСУДАРСТВЕННЫЙ ПАТЕНТНЫЙ КОМИТЕТ РЕСПУБЛИКИ БЕЛАРУСЬ УСТРОЙСТВО ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ(71) Заявитель Военная академия Республики Беларусь(73) Патентообладатель Военная академия Республики Беларусь(57) Устройство обработки нечеткой информации, содержащее генератор тактовых импульсов, группу вычислительных блоков, первый, второй и третий элементы И, элемент НЕ, первый элемент ИЛИ, первый и второй регистры, первую группу элементов ИЛИ, первый, второй и третий элемент задержки, реверсивный счетчик, триггер, первый сдвиговый регистр, первый блок сравнения, группу регистров, причем выход генератора тактовых импульсов соединен с первым входом первого элемента И, второй вход которого соединен с выходом элемента НЕ, входом подключенного к выходу переполнения реверсивного счетчика, вход вычитания которого соединен с выходом первого элемента И, единичный вход триггера подключен к выходу первого элемента задержки, а прямой выход подключен к первому входу второго элемента И, к третьему входу первого элемента И, к первому входу третьего элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выходом подключенного к входу записи реверсивного счетчика, к первым входам всех вычислительных блоков, ко входу установки первого регистра в единичное состояние,группа выходов группы регистров подключена к входам соответствующих элементов блока элементов И,выходы которых являются первой группой входов первого блока элементов ИЛИ, второй группой входов которого являются группы выходов вычислительных блоков, вторые входы которых объединены и подключены к выходу первого элемента И, первая группа выходов первого сдвигового регистра подключена к соответствующим вторым входам блока элементов И, а вторая группа выходов первого сдвигового регистра подключена к соответствующим третьим входам вычислительных Фиг. 1 блоков, у которых четвертые входы объединены и подключены к входу первого регистра, к первому входу первого блока сравнения, второй вход которого соединен с выходом первого регистра, к группе выходов первого блока элементов ИЛИ, второй элемент задержки выходом подключен ко входу сдвига первого сдвигового регистра, а вход подключен к выходу генератора тактовых импульсов и объединен со вторым вхо 127 дом третьего элемента И и со вторым входом второго элемента И, третий вход которого подключен к выходу переполнения реверсивного счетчика, а выход соединен с входом третьего элемента задержки, выходом подключенного к управляющему входу первого блока сравнения, выход которого подключен ко входу записи первого регистра, второй регистр выходом подключен ко входам реверсивного счетчика, третий вход третьего элемента И соединен с выходом старшего разряда первого сдвигового регистра, вход первого сдвигового регистра, вход первого элемента задержки объединен со вторым входом первого элемента ИЛИ,отличающееся тем, что в устройство введены второй сдвиговой регистр, группа блоков хранения входной информации, группа элементов задержки, второй блок элементов ИЛИ, второй, третий, четвертый и пятый элементы ИЛИ, второй и третий блоки сравнения, третий и четвертый регистры, четвертый элемент задержки, причем группа выходов каждого блока хранения входной информации подключена к соответствующим выходам второго сдвигового регистра, последние входы каждой группы входов всех блоков хранения входной информации соединены с соответствующими входами группы элементов задержки, группы выходов которой подключены к группе входов пятого элемента ИЛИ, к первой группе входов блока регистров, вход записи последнего регистра блока регистров объединен со входами записи регистров с нечетными номерами блока регистров, с установочным входом младшего разряда первого сдвигового регистра, с входом первого элемента задержки и вторым входом первого элемента ИЛИ, все выходы с четными номерами второго сдвигового регистра подключены к группе входов второго элемента ИЛИ, выход которого соединен со входом четвертого элемента задержки, выход которого соединен со вторым входом третьего элемента ИЛИ и с управляющим входом третьего блока сравнения, группы выходов блоков хранения входной информации подключены к соответствующим группам входов второго блока элементов ИЛИ,группа выходов которого объединена с группой входов третьего регистра и с первой группой входов второго блока сравнения, вторая группа входов которого подключена к группе выходов третьего регистра, выход второго блока сравнения подключен к о входу записи третьего регистра, установочный вход в единичное состояние которого подключен к выходу третьего элемента ИЛИ, первый вход которого объединен с первыми входами блоков хранения входной информации, с выходом четвертого элемента ИЛИ, с первым входом пятого элемента ИЛИ, с установочным входом в единицу младшего разряда второго сдвигового регистра,вход сдвига которого подключен ко входу сдвига первого сдвигового регистра, второй вход четвертого элемента ИЛИ подключен к третьему входу третьего элемента И, а первый его вход является установочным,выход пятого элемента ИЛИ подключен к установочному входу в нулевое состояние четвертого регистра,вход записи которого подключен к выходу третьего блока сравнения, вторая группа входов которого подключена к группе выходов четвертого регистра, группа входов которого объединена с первой группой входов третьего регистра и с группой выходов третьего регистра, группа выходов четвертого регистра объединена с группами входов регистров с четными номерами блока регистров, группа входов регистров с нечетными номерами которого является информационными входами, группа выходов первого регистра является группой выходов устройства.(56) 1. А.с. СССР 942071, МПК 06 К 9/62, 1982. 2. А.с. СССР 1363275, МПК 06 К 9/62, 1987. 3. А.с. СССР 1357984, МПК 06 К 9/00, 1987 (прототип). 4. Д. Дюбуа, . Прад. Теория возможностей. Приложения к представлению знаний в информатике М. Радио и связь, 1990.С. 288. 5. Г. Дружинин, И. Сергеева, Н. Стрельникова. Повышение надежности и качества функционирования технологических систем за счет разработки и развития систем поддержки операторов Надежность и контроль качества. Ежемесячное приложение к журналу Стандарты и качество.6, 1990. - С. 43-47. Полезная модель относится к области автоматики и вычислительной техники и предназначено для использования в системах принятия решений при наличии нечеткой информации. Известно устройство для распознавания образов 1, содержащее группу делителей напряжений, группу функциональных преобразователей, пороговый блок, формирователи сигналов, интегратор, генератор функциональных напряжений, группу интеграторов. Известно устройство для распознавания информации 2, содержащее входной усилитель, блок адаптации, интегратор, дна компаратора, два элемента И, генератор импульса, блок задания временных интервалов. Недостатком данных устройств является невозможность их применения по назначению в случае, когда входная информация, на основе которой решается задача распознавания образов, является неопределенной(нечеткой). Наиболее близким по своей сущности к заявляемому устройству является устройство для распознавания ситуаций 3. Устройство-прототип содержит генератор тактовых импульсов (ГТИ), группу вычислительных 2 127 блоков (ВБ), первый, второй и третий элементы И, элемент НЕ, первый элемент ИЛИ, первый и второй регистры, первую группу элементов ИЛИ, первый, второй и третий элемент задержки (ЭЗ), реверсивный счетчик (РС), триггер, первый сдвиговый регистр (СР), первый блок сравнения (БС), группу регистров, причем выход ГТИ соединен с первым входом первого элемента И, второй вход которого соединен с выходом элемента НЕ, входом подключенного к выходу переполнения реверсивного счетчика (РС), вход вычитания которого соединен с выходом первого элемента И, единичный вход триггера подключен к выходу первого ЭЗ, а прямой выход подключен к первому входу второго элемента И, к третьему входу первого элемента И, к первому входу третьего элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выходом подключенного к входу записи РС, к первым входам всех ВБ, ко входу установки первого регистра в единичное состояние, группа выходов группы регистров подключена к входам соответствующих элементов блока элементов И, выходы которых являются первой группой входов первого блока элементов ИЛИ, второй группой входов которого являются группы выходов ВБ, вторые входы которых объединены и подключены к выходу первого элемента И, первая группа выходов первого сдвигового регистра подключена к соответствующим вторым входам блока элементов И, а вторая группа выходов первого сдвигового регистра подключена к соответствующим третьим входам ВБ, у которых четвертые входы объединены и подключены к входу первого регистра, к первому входу первого блока сравнения, второй вход которого соединен с выходом первого регистра, к группе выходов первого блока элементов ИЛИ, второй ЭЗ выходом подключен ко входу сдвига первого сдвигового регистра, а вход подключен к выходу генератора тактовых импульсов и объединен со вторым входом третьего элемента И и со вторым входом второго элемента И,третий вход которого подключен к выходу переполнения РС, а выход соединен с входом третьего ЭЗ, выходом подключенного к управляющему входу первого БС, выход которого подключен ко входу записи первого регистра, второй регистр выходом подключен ко входам РС, третий вход третьего элемента И соединен с выходом старшего разряда первого СР, вход первого СР, вход первого ЭЗ объединен со вторым входом первого элемента ИЛИ. Однако, данное устройство предназначено для обработки информации, когда ситуация представлена в виде семантической сети. При моделировании взвешенных расплывчатых запросов устройство, должно обрабатывать нечеткую информацию. В этом случае степень фильтрации 5 некоторого объекта с помощью полного фильтра с учетом относительной важности р, различных целей задается выражением 4(1)(1-р, ),1,где- степень фильтрации с помощью полного фильтра,р - весовые коэффициенты выражающие относительную важность -го элементарного фильтра, - степень фильтрации -м элементарным фильтром.- количество элементарных фильтров. Причем степень фильтрации-м элементарным фильтром рассматриваемого объекта определяется 4, стр. 119 как(,(, (2)где- степень фильтрации 1-м элементарным фильтром,Р и А- нечеткие множества с известными функциями распределения возможностейи , - полное множество рассуждений. Выражение (2) фактически позволяет определить возможность событияесть , при условииесть А. Причем множестваи А нечеткие с известными функциями распределения возможностейи ,множество рассуждений в -м случае (в случае рассмотрения -ой цели). Задача полезной модели - расширение области применения устройства. Техническим результатом полезной модели является возможность обработки нечеткой информации. Это позволяет моделировать расплывчатые высказывания. Обработка нечеткой информации ведет к необходимости усложнения устройств их обработки, но, вместе с тем, дает ряд преимуществ. Например, 4 можно моделировать неточную (лингвистическую) информацию за счет представления различных смысловых оттенков правила обработки информации могут работать даже тогда, когда реальная ситуация точно не соответствует предусмотренной, что часто бывает во многих практических случаях возможным становится классификация числовых данных, когда соответствующие классы описываются именами нечетких множеств для моделирования нечеткой информации требуется ограниченное число правил. Предлагаемое устройство может быть полезным при разработке систем поддержки операторов 5, систем поддержки принятия решений. Решение указанной задачи достигается тем, что в устройство, содержащее ГТИ, группу ВБ, первый, второй и третий элементы И, элемент НЕ, первый элемент ИЛИ, первый и второй регистры, первую группу элементов ИЛИ, первый второй и третий ЭЗ, РС, триггер, первый СР, первый блок сравнения, группу элементов И, группу регистров, причем выход ГТИ соединен с первым входом первого элемента И , вто 3 127 рой вход которого соединен с выходом элемента НЕ, входом подключенного к выходу переполнения РС,вход вычитания которого соединен с выходом первого элемента И, единичный вход триггера подключен к выходу первого ЭЗ, а прямой выход подключен к первому входу второго элемента И, к третьему входу первого элемента И, к первому входу третьего элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выходом подключенного к входу записи РС, к первым входам всех ВБ, к входу установки первого регистра в единичное состояние, группа выходов группы регистров подключения к входам соответствующих элементов блока элементов И, выходы которых являются первой группой входов первого блока элементов ИЛИ, второй группой которою являются группы выходов ВБ, вторые входы которых объединены и подключены к выходу первого элемента И, первая группа выходов первого СР подключена к соответствующим вторым входам блока элементов И, а вторая группа выходов первого СР подключена к соответствующим третьим входам ВБ, у которых четвертые входы объединены и подключены к входу первого регистра, к первому входу первого ВС, второй вход которого соединен с выходом первого регистра, к группе выходов первого блока элементов ИЛИ, второй элемент задержки выходом подключен к входу сдвига первого СР, а вход подключен к выходу ГТИ и объединен со вторым входом третьего элемента И и со вторым входом второго элемента И, третий вход которого подключен к выходу переполнения РС, а выход соединен с входом третьего ЭЗ, выходом подключенного к управляющему входу первого БС, выход которого подключен ко входу записи первого регистра, второй регистр выходами подключен ко входам РС,третий вход третьего элемента И соединен с выходом старшего разряда первого СР, вход первого элемента объединен со вторым входом элемента ИЛИ введены второй СР, группа боков хранения входной информации (БХВИ), группа ЭЗ, второй блок элементов ИЛИ, второй, третий, четвертый, пятый элементы ИЛИ, второй и третий БС, третий и четвертый регистры, четвертый ЭЗ, причем группа входов каждого БХВИ подключена к соответствующим выходам второго СР, последние входы каждой группы входов всех БХВИ соединены с соответствующими входами группы ЭЗ, группа выходов которой подключена к группе входов пятого элемента ИЛИ, к первой группе входов блока регистров, вход записи последнего регистра из блока регистров объединен со входами записи регистров с нечетными номерами регистров, с установочным входом младшего разряда первого СР, с входом первого ЭЗ и вторым входом первого элемента ИЛИ,все выходы с четными номерами второго СР подключены к группе входов второго элемента ИЛИ, выход которого соединен с выходом четвертого ЭЗ, выход которого соединен со вторым входом третьего элемента ИЛИ и с управляющим входом третьего БС, группы выходов БХВИ подключены к соответствующим группам входов второго блока элементов ИЛИ, группа выходов которого объединена с группой входов третьего регистра, выход второго БС подключен к входу разрешения записи третьего регистра, установочный вход в единичное состояние которого подключен к выходу третьего элемента ИЛИ, первый вход которого объединен с первыми входами БХВИ, с выходом четвертого элемента ИЛИ, с первым входом пятого элемента ИЛИ, с установочным входом в единицу младшего разряда второго СР, вход сдвига которого подключен к входу сдвига первого СР, второй вход четвертого элемента ИЛИ подключен к третьему входу третьего элемента И, а первый его вход является установочным, выход пятого элемента ИЛИ подключен к установочному входу в нулевое состояние четвертого регистра, вход записи которого подключен к выходу третьего БС, вторая группа входов которого подключена к группе четвертого регистра, первая группа входов третьего БС объединена с группой входов четвертого регистра, с группой выходов третьего регистра, группа выходов четвертого регистра объединена с группами входов регистров с четными номерами блока регистров. На фиг. 1 изображена функциональная схема устройство обработки нечетной информации на фиг. 2 схема вычислительного блока на фиг. 3 - схема блока хранения входной информации. Устройство обработки нечеткой информации (фиг. 1) содержит ГТИ 1, причем его выход соединен с первым входом первого элемента И 2, второй вход соединен с выходом элемента НЕ 3, входом подключенного к выходу переполнения РС 4, вход вычитания которого соединен с выходом первого элемента И 2,единичный вход триггера 8 подключен к выходу первого ЭЗ 6, а прямой выход подключен к первому входу второго элемента И 5, к третьему входу первого элемента И 2, к первому входу третьего элемента И 9,выход которого подключен к первому входу первого элемента ИЛИ 10, выходом подключенного к входу записи РС 4, к первым входам всех ВБ 7, группа входов блока регистров 11 подключена к входам соответствующих элементов блока элементов И 12, выходы которых являются первой группой входов первой группы элементов ИЛИ 13, второй группы входов которого является группы выходов ВБ 7, вторые входы которых объединены и подключены к выходу первого элемента И 2, соответствующие выходы первого СР 14 являются вторыми входами каждого элемента блока элементов И 12 и третьими входами каждого ВБ 7,группа входов каждого из которых объединена со входами первого регистра 15, со входами первого БС 16 и подключена к выходам элементов первого блок элементов ИЛИ 13, второй ЭЗ 17 выходом подключен к входу сдвига СР 14, а вход подключен к выходу ГТИ 1 и объединен со вторым входом второго элемента И 5, третий вход которого подключен к выходу переполнения РС 4, а выход соединен через третий ЭЗ 18 с управляющим входом первого БС 16, выход которого подключен ко входу записи первого регистра 15, вы 4 127 ходами подключенного ко вторым входам схемы 16 сравнения, а входом записи подключен к выходу первого элемента ИЛИ 10, выходы второго регистра 19 подключены к входам РС 4, третий вход третьего элемента И 9 соединен с выходом старшего разряда первого СР 14 и со вторым входом четвертого элемента ИЛИ 24, первый вход которого является установочным, а выходом подключенною к первому входу пятою элемента ИЛИ 20, к первому входу третьего элемента ИЛИ 25, к объединенным первым выходам БХВИ 32 и к выходу установки единицы в младшем разряде второго СР 29, группа входов каждого БХВИ 32 подключена к соответствующим выходам второго СР 29, последние входы каждой группы входов всех БХВИ 32 соединены с соответствующими входами группы ЭЗ 31, группа выходов которой подключена к группе входов пятого элемента ИЛИ 20, к первой группе входов блока регистров 11, которая образуется из входов записи четных регистров блока регистров 11, вход записи последнего регистра из блока регистров 11 объединен со входами записи нечетных регистров блока регистров 11, с установочным входом младшего разряда первого СР 14 с входом первого ЭЗ 6 и вторым входом первого элемента ИЛИ 10, все выходы с четными номерами второго СР 29 подключены к группе входов второго элемента ИЛИ 27, выход которого соединен через четвертый ЭЗ 23 со вторым входом третьего элемента ИЛИ 25 и с управляющим входом третьего БС 22, группы выходов БХВИ 32 подключены к соответствующим группам входов второго блока элементов ИЛИ 30, группа выходов которого объединена с группой входов третьего регистра 26 и с первой группой входов второго БС 28, вторая группа входов которого подключена к группе выходов третьего регистра 26, а выход второго БС 28 подключен к входу записи третьего регистра 26, установочный вход в единичное состояние которого подключен к выходу третьего элемента ИЛИ 25, вход сдвига второго СР 29 подключен к входу сдвига первого СР 14, выход пятого элемента ИЛИ 20 подключен к установочному входу в нулевое состояние четвертого регистра 21, вход записи которого подключен к выходу третьего БС 22,вторая группа входов которого подключена к группе выходов четвертого регистра 21, первая группа входов третьего БС 22 объединена с группой входов четвертого регистра 21, с группой выходов третьего регистра 26, группа выходов четвертого регистра 21 объединена с группами входов четных регистров блока регистров 11. Вычислительный блок 7 (фиг. 2) содержит СР 33, вход сдвига которого является вторым входом ВБ 7, а выход подключен к входу установки младшего разряда СР 33, БС 34, первая группа входов которого является четвертым входом ВБ 7, регистр 35, группа входов которого объединена с первой группой входов БС 34,выход которого подключен к входу записи регистра 35, установочный вход которого является первым входом ВБ 7, выход СР 33 объединен с входом управления БС 34, группа выходов регистра 35 объединена с группой входов элемента И 36, группа выходов которого является группой выходов ВБ 7, а второй вход элемента И 36 является третьим входом ВБ 7. Блок хранения входной информации (фиг. 3) содержит группу регистров 37137, входы которых являются информационными, группу элементов И 381-38, группы выходов которых являются группами выходов БХВИ 32, группы входов соответствующих элементов И 38 подключены к группам выходов соответствующих регистров 37, входы записи регистров 37 объединены и являются первым входом БХВИ 32, вторые входы элементов И 38 образуют группу входов БХВИ 32. Устройство работает следующим образом. На регистре 19 записана величина -1, где- количество регистров в группе регистров 11, число которых соответствует удвоенному количеству элементов(следовательно,- четно), на СР 33 ВБ 7 записана матрица, отражающая порядок сравнения элементови 1-р. Порядок сравнения должен быть таков, чтобы в каждом ВБ 7 сравнивалась только одна пара (1-р, ) с одинаковыми индексами. Например, для записи в первом ВБ 7 числа (1-р, ) нужно, чтобы в СР 33 этого ВБ 7 была записана матрица 1,1,0,0,0 для записи во втором ВБ 7 числа (1-р, ) нужно, чтобы в СР 33 этого ВБ 7 была записана матрица 0,0,1,1,0,0, и т. д. Количество выходов в первой группе выходов сдвигового регистра 14 будет соответствовать количеству регистров в блоке регистров 11, а количество выходов во второй группе выходов СР 14 будет соответствовать количеству ВБ 7, количество которых равно . Количество БХВИ 32 равно количеству элементов . Количество выходов СР 29 равно числу , где - количество значенийи.Количество регистров 1 в БХВИ 32 определяется числом . С приходом сигнала на установочный вход происходит запись информации, поступившей на входы групп регистров 37 в БХВИ 32, причем на первые регистры 37 БХВИ поступает информация А(1) на вторые регистры 37 БХВИ 32 поступает информация (1), на третьи регистры (2), на четвертые (2) и т. д., запись единицы в младший разряд СР 29, установка в единичное состояние регистра 26 и установка в нулевое состояние регистра 21. Единица появившись в младшем разряде СР 29 разрешает выдачу информации с первого регистра 37 и первого БХВИ 32 па группу элементов ИЛИ 30, пройдя через нее информация поступит на БС 28, где сравниться с содержимым регистра 26, и на регистр 26. В случае, если поступающая информация меньше содержимого регистра 26, то БС 28 выдает команду на запись информации поступившей на входы регистра 26. С приходом следующего тактового импульса на вход СР 29 произойдет сдвиг единицы на один разряд в сторону старших разрядов и эта единица поступает на вход первого БХВИ 32 и на элементы ИЛИ 27. Теперь будет разрешаться прохождение информации, записанной на втором регистре 37 первого БХВИ 5 12732. Информация, пройдя через группу элементов ИЛИ 30, поступит на ВС 28 и входы регистра 26,. В случае, если поступившая информация меньше содержимого регистра 26, то БС 28 выдаст команду на запись информации, поступившей на входы регистра 26, т.е. будет реализовано выражение (1), (1). Одновременно с этим сигнал со второго выхода СР 29, пройдя элемент ИЛИ 27, поступит на БС 22 и на элемент ИЛИ 25. Когда сигнал поступил на вход управления ВС 22, разрешается сравнение содержимого регистра 21 и регистра 26 БС 22. В случае, если информация, поступившая с выходов регистра 26, будет больше содержимого регистра 21, то БС 22 выдаст команду на запись в регистр 21 содержимого регистра 26 Сигнал, задержавшись на элементе ИЛИ 2, даст команду на вход установки регистра 26 в единичное состояние. Такой процесс работы будет повторяться до тех пор, пока единица с выходов СР 29 не будет подана на последний вход из группы входов первого БХВИ 32. С приходом этого сигнала в регистре 21 будет записан число 1, равное 1, (1),(1). и это число будет подано на входы регистров с четными номерами блока регистра 11. Одновременно с приходом единицы на последний вход группы входов первого БХВИ 32, сигнал поступает на первый вход группы входов блока ЭЗ 31. С первого выхода группы выходов ЭЗ 31 сигнал поступает на соответствующий вход группы входов элемента ИЛИ 20, и на первый вход первой группы входов блока регистров 11, где этим сигналом запишется число 1 на первый регистр с четным номером 112 группы регистров 11. Сигнал с выхода элемента ИЛИ 20 поступит на вход установки регистра 21 в нулевое состояние. Далее процесс работы устройства повторяется. Теперь информация будет считываться с последующих БХВИ 32. Вычисленные значения , будут записываться на соответствующие регистры с четными номерами блока регистров 11. Процесс будет повторяться до тех пор, пока в старшем разряде СР 29 не появится единица. С ее появлением произойдет запись последнего значения , в последний регистр с четным номером блока регистров 11, установка в единичное состояние регистра 26 и в нулевое состояние регистра 21, запись чисел 1-, причем в первый регистр блока регистров 11 будет записано число 1-р 1, в третий регистр - 1-р 2 и т. д. на регистры с нечетными номерами блока регистров 11, запись единицы в младший разряд СР 14. Этот же сигнал, пройдя через элемент ИЛИ 10 установит в единичное состояние регистр 15 и в нулевое состояние регистр 33 ВБ 7,разрешит перезапись содержимого регистра 19 на РС 4, а пройдя через ЭЗ 6 установит в единичное состояние триггер 8, высокий потенциал с выхода которого элементы И 2, 5, 9. На выходе переполнения РС появится низкий потенциал, который запретит прохождение тактовых импульсов с ГТИ 1 через элемент И 5,пройдя через элемент НЕ 3, разрешит прохождение через элемент И 2. Вычислительные блоки 7 работают следующим образом. Тактовый импульс, пройдя через элемент И 36 поступит на сдвиговый вход СР 33 всех ВБ 7. Произойдет сдвиг информации, находящейся в этих регистрах. Единичный сигнал (там, где он появится) разрешит сравнение содержимого соответствующего регистра блока 11 регистров с содержимым регистра 35 тех ВБ 7, где на выходе СР 33 появился единичный сигнал. В случае, если поступающая информация больше содержимого регистра 35, то БС 34 вырабатывает сигнал, под действием которого происходит запись в регистр 35 поступившей информации. После этого под действием того же тактового импульса, задержанного во времени элементом 17 задержки, произойдет сдвиг единицы на СР 14 на один разряд в сторону старших разрядов. На вход БС 34 всех ВБ 7 будет подано содержимое следующего регистра блока 11 регистров. Далее процесс работы устройства повторяется. Таким образом происходит параллельный сдвиг содержимого всех СР 33 ВБ 7 и отыскание максимальных значений из пар (1-, ,). Максимум каждой пары хранится в своем ВБ 7. Например, ах (1 1, 1) хранится в первом ВБ 7, ах (1-2, 2 ) - во втором ВБ 7 и т. д После того, как всерегистров блока 11 регистров будут просмотрены, содержимое РС 4 и станет равным нулю, а на его выходе переполнения появится высокий потенциал, который откроет элемент И 5 и разрешит прохождение тактовых импульсов через него, и пройдя через элемент НЕ 3, запретит прохождение тактовых импульсов с ГТИ 1 на вторые входы ВБ 7. Тактовые импульсы теперь будут проходить через элемент И 5 и синхронизировать работу блока сравнения, на вход которого поочередно будет подаваться содержимое регистров 35 ВБ 7, среди которых будет выбираться минимальное значение и записываться в регистре 15. После того как будет опрошен последний ВБ 7, на выходе старшего разряда СР 14 появится высокий потенциал, который откроет элемент И 9 и запишет новую входную информацию на регистры 37 БХВИ 32(фиг. 3), пройдя через четвертый элемент ИЛИ 24. Следующий тактовый импульс с ГТИ 1 пройдет через элемент И 9, элемент ИЛИ 10 и установит регистр 15 в единичное состояние, регистры 35 всех ВБ 7 - в нулевое состояние, перепишет содержимое регистра 19 на РС 4, запишет ноль в старший разряд СР 14. Процесс работы устройства повторится для новой входной информации. Государственный патентный комитет Республики Беларусь. 220072, г. Минск, проспект Ф. Скорины, 66.

МПК / Метки

МПК: G06K 9/00

Метки: обработки, информации, нечеткой, устройство

Код ссылки

<a href="https://by.patents.su/7-u127-ustrojjstvo-obrabotki-nechetkojj-informacii.html" rel="bookmark" title="База патентов Беларуси">Устройство обработки нечеткой информации</a>

Предыдущий патент: Устройство дистанционного обмена

Следующий патент: Штепсельный соединитель

Случайный патент: Способ непрерывно-циклического литья заготовок