Способ и устройство для улучшения динамических характеристик цифровой системы фазовой синхронизации

Текст

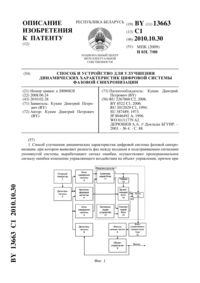

(51) МПК (2009) НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ СПОСОБ И УСТРОЙСТВО ДЛЯ УЛУЧШЕНИЯ ДИНАМИЧЕСКИХ ХАРАКТЕРИСТИК ЦИФРОВОЙ СИСТЕМЫ ФАЗОВОЙ СИНХРОНИЗАЦИИ(71) Заявитель Кукин Дмитрий Петрович(72) Автор Кукин Дмитрий Петрович(73) Патентообладатель Кукин Дмитрий Петрович(57) 1. Способ улучшения динамических характеристик цифровой системы фазовой синхронизации, при котором выявляют разность фаз между входным и подстраиваемым сигналами упомянутой системы, вырабатывают сигнал ошибки, осуществляют пропорциональное сигналу ошибки изменение управляющего воздействия на объект управления, причем при 13663 1 2010.10.30 выявлении значительного фазового рассогласования между упомянутыми сигналами переводят систему в режим автоматической подстройки частоты, а при незначительном рассогласовании - в режим фазовой автоподстройки частоты, отличающийся тем, что в режиме автоматической подстройки частоты заменяют управляющее воздействие на объект управления управляющим воздействием максимально допустимой величины путем применения нелинейного корректирующего устройства с обеспечением возможности подстройки частоты объекта управления к частоте входного сигнала с максимально возможной скоростью, при равенстве разности частот между входным и подстраиваемым сигналами установленному порогу, соответствующему инерционности объекта управления, систему переводят в режим фазовой автоподстройки частоты, при этом производят вычисление величины управляющего воздействия путем перемножения величины фазового рассогласования между упомянутыми сравниваемыми сигналами на дополнительный динамический коэффициент усиления кольца фазовой синхронизации УУ, который определяют из выражения УУ 0,80,1315,где- длительность последнего интервала времени, на котором система находилась в режиме автоматической подстройки частоты. 2. Устройство для улучшения динамических характеристик цифровой системы фазовой синхронизации способом по п. 1, содержащее опорный генератор, два делителя частоты, частотно-фазовый детектор, микроконтроллер со сравнивающим блоком, запоминающим устройством, таймером, вычисляющим блоком, умножающим блоком и ключом,два блока измерения частоты, фильтр нижних частот, объект управления и блок управляемых генераторов тока, причем выход опорного генератора соединен со входом первого делителя частоты, являющегося источником входной последовательности импульсов, выход которого соединен с первым входом частотно-фазового детектора и со входом первого блока измерения частоты, выход блока управляемых генераторов тока через фильтр нижних частот соединен с управляющим входом объекта управления, выход которого соединен со входом второго делителя частоты, выход которого соединен со вторым входом частотно-фазового детектора и со входом второго блока измерения частоты, выход первого блока измерения частоты соединен с первым входом сравнивающего блока, второй вход которого соединен с выходом второго блока измерения частоты, выход частотнофазового детектора соединен с первым входом вычисляющего блока, со вторым входом которого соединен выход таймера, вход которого соединен с первым выходом сравнивающего блока и с управляющим входом ключа, второй выход сравнивающего блока соединен с первым входом умножающего блока, со вторым входом которого соединен выход запоминающего устройства, выходы вычисляющего и умножающего блоков соответственно соединены с первым и вторым входами ключа, выход которого соединен с входом блока управляемых генераторов тока. Настоящее изобретение относится к системам фазовой синхронизации (СФС). Более конкретно к способу и устройству для улучшения динамических характеристик цифровых СФС (ЦСФС). Известны СФС представляющие собой схему, которая эффективно отслеживает фазы входного и опорного сигналов. Если разность фаз между входным и подстраиваемым колебаниями системы постоянна, то СФС засинхронизирована. Если происходит изменение фазы (частоты) входного или подстраиваемого сигналов, то фазовый детектор в СФС будет вырабатывать сигнал ошибки, пропорциональный величине и полярности изменения фазы. Этот сигнал ошибки вызовет изменение фазы (частоты) опорного сигнала таким образом, что состояние синхронизации вновь восстанавливается. 2 13663 1 2010.10.30 СФС с элементами дискретизации, в том числе ЦСФС, широко применяются в технике связи и управления, радиоавтоматике и других системах авторегулирования. Такое положение вещей обусловлено повышенной надежностью, а также относительной простотой изготовления и настройки подобных систем. ЦСФС находят широкое применение в устройствах, осуществляющих демодуляцию частотно-модулированного радиосигнала,демодуляцию фазоманипулированного сигнала, синтез частот, синхронизацию данных,преобразованиесигналов, регулирование скорости двигателя. Широко известна обобщенная структурная схема СФС, включающая фазовый дискриминатор, делитель частоты с фиксированным коэффициентом деления, объект управления и фильтр нижних частот, образующие кольцо фазовой автоподстройки частоты 1. ЦСФС созданные по этой схеме характеризуются простотой схемотехнической реализации и обеспечивают высокие качественные параметры выходного сигнала. Основным недостатком существующих на данный момент ЦСФС является низкое быстродействие, что обусловлено отрицательными явлениями, характеризующими режим захвата и в значительной степени ухудшающими динамические характеристики устройства. Наиболее близким по физической сущности и технической реализации к предлагаемому способу и устройству улучшения динамических характеристик ЦСФС является синтезатор частот, описанный в патенте 2. Способ улучшения динамических характеристик цифровой системы фазовой синхронизации, описанный в упомянутом патенте, включает выявление разности фаз между входным и подстраиваемым колебаниями системы, выработку сигнала ошибки, в случае значительного фазового рассогласования предусмотрено увеличение коэффициента усиления системы и уменьшение демпфирования. В начальный момент времени процесса перестройки частоты (на промежутке времени 0 и 1, при этом 0 - стартовый момент времени, а в момент времени 1 достигается равенство сравниваемых частот) реализуется режим широкой полосы с увеличенным коэффициентом усиления кольца фазовой автоподстройки частоты. В момент времени 2 имеет место факт состояния синхронизма по фазе. В течение промежутка времени 1 и 2 кольцо фазовой автоподстройки находится в режиме узкой полосы для замедления (демпфирования) скорости переходного процесса при приближении к установившемуся состоянию. В прототипе переходной процесс улучшается и сокращается его длительность за счет изменения в определенные моменты времени структуры фильтра нижних частот и параметров блока управляемых генераторов тока. Существенным недостатком описанной выше системы-прототипа является то, что в ней не учитывается инерционность объекта управления, вследствие чего при замене управляемого генератора на более инерционный объект система теряет устойчивость. Кроме того, на начальном этапе подстройки существует возможность значительно ускорить перестройку частоты объекта управления путем введения нелинейного корректирующего устройства. Задачей, решаемой настоящим изобретением, является преодоление вышеупомянутых недостатков и обеспечение достижения дополнительных преимуществ за счет создания ЦСФС и соответствующего ей способа, который улучшает характеристики захвата синхронизма простым с точки зрения вычислений и одновременно с этим надежным способом. Иными словами, задачей, которую решает предлагаемое изобретение, является разработка универсального способа и устройства для улучшения динамических характеристик ЦСФС путем введения в нее нелинейного корректирующего устройства, а также динамического коэффициента усиления. Поставленная задача решается способом для улучшения динамических характеристик цифровой системы фазовой синхронизации, включающим выявление разности фаз между входным и подстраиваемым колебаниями системы, выработку сигнала ошибки, пропор 3 13663 1 2010.10.30 циональное сигналу ошибки изменение управляющего воздействия на объект управления,в случае выявления значительного фазового рассогласования между сравниваемыми колебаниями система переходит в режим автоматической подстройки частоты, в случае небольшого рассогласования в системе имеет место режим фазовой автоподстройки частоты, отличающимся тем, что в режиме автоматической подстройки частоты осуществляется замена управляющего воздействия путем применения нелинейного корректирующего устройства, в режиме фазовой автоподстройки частоты производится динамическое вычисление коэффициента усиленияпо полученной опытным путем формуле 0,80,1315, где- длительность последнего интервала времени, на котором система находилась в режиме автоматической подстройки частоты. Устройство для улучшения динамических характеристик цифровой системы фазовой синхронизации содержащее опорный генератор, два делителя частоты, частотно-фазовый детектор, микроконтроллер, фильтр нижних частот, объект управления, блок управляемых генераторов тока, выход опорного генератора соединен со входом первого делителя частоты, являющегося источником входной последовательности импульсов, выход первого делителя частоты соединен с первым входом частотно-фазового детектора, выход блока управляемых генераторов тока через фильтр нижних частот соединен с управляющим входом объекта управления, выход объекта управления подключен ко входу второго делителя частоты, выход которого в свою очередь подключен ко второму входу частотнофазового детектора, отличающееся тем, что введены два блока измерения частоты, а в состав микроконтроллера входят сравнивающий блок, запоминающее устройство, таймер,вычисляющий блок, умножающий блок, ключ, выход первого делителя частоты соединен со входом первого блока измерения частоты, выход первого блока измерения частоты подключен к первому входу сравнивающего блока, выход частотно-фазового детектора соединен с первым входом вычисляющего блока, ко второму входу которого подключен выход таймера, вход последнего в свою очередь подключен к первому выходу сравнивающего блока, кроме того, к первому выходу сравнивающего блока подключен управляющий вход ключа, второй выход сравнивающего блока подключен к первому входу умножающего блока, ко второму входу которого подключен выход запоминающего устройства, выходы вычисляющего блока и умножающего блока соединены с первым и вторым входами ключа, выход ключа подключен ко входу блока управляемых генераторов тока, выход второго делителя частоты подключен ко входу второго блока измерения частоты. В начальный момент времени процесса перестройки частоты (на промежутке времени 0 и 1) реализуется режим широкой полосы с заменой управляющего сигнала на максимально допустимый. При этом кольцо автоподстройки теряет астатизм по фазе, оставаясь только астатической по частоте. Таким образом, до момента времени 1 система фазовой автоподстройки работает в режиме частотной автоподстройки. С момента времени 1 переходного процесса система приобретает свойства астатизма по фазе и стремится устранить рассогласование по фазе, имеющееся на момент достижения синхронизма по частоте. В течение промежутка времени, начиная с момента 1, кольцо фазовой автоподстройки находится в режиме узкой полосы для демпфирования скорости переходного процесса при приближении к установившемуся состоянию. В этом режиме коэффициент усиления системы определяется динамически. В результате система автоподстройки очень быстро производит дерегулирование для последних нескольких сотен герц выходной частоты объекта управления. Признаки и преимущества настоящего изобретения поясняются более детально в последующем подробном описании со ссылками на чертежи, на которых представлено фиг. 1 - структурная схема предлагаемого устройства фиг. 2 - графики переходных процессов, представляющие собой результаты математического моделирования с использованием программы моделирования , иллю 4 13663 1 2010.10.30 стрирующие сравнение традиционного способа синхронизации с вариантом осуществления настоящего изобретения. Детальное описание изобретения. Структурная схема предлагаемого устройства приведена на фиг. 1. ЦСФС содержит опорный генератор 1, делитель 2 частоты, блок 3 измерения частоты, частотно-фазовый детектор 4, блок 5 измерения частоты, делитель 6 частоты, микроконтроллер 7, фильтр 8 нижних частот, объект 9 управления, блок 10 управляемых генераторов тока. В состав микроконтроллера 7 входят сравнивающий блок 11, запоминающее устройство 12, таймер 13,вычисляющий блок 14, умножающий блок 15, ключ 16. Выход опорного генератора 1 соединен со входом делителя 2 частоты, являющегося источником входной последовательности импульсов, к которой осуществляется подстройка сигнала объекта 9 управления. Выход делителя 2 частоты соединен с первым входом частотно-фазового детектора 4 и со входом блока 3 измерения частоты. Выход блока 3 измерения частоты подключен к первому входу сравнивающего блока 11. Выход частотно-фазового детектора 4 соединен с первым входом вычисляющего блока 14, ко второму входу которого подключен выход таймера 13, вход последнего в свою очередь подключен к первому выходу сравнивающего блока 11. Кроме того, к первому выходу сравнивающего блока 11 подключен управляющий вход ключа 16. Второй выход сравнивающего блока 11 подключен к первому входу умножающего блока 15, ко второму входу которого подключен выход запоминающего устройства 12. Выходы вычисляющего блока 14 и умножающего блока 15 соединены с первым и вторым входами ключа 16. Выход ключа 16 подключен ко входу блока 10 управляемых генераторов тока,выход которого через фильтр 8 нижних частот соединен с управляющим входом объекта 9 управления. Выход объекта 9 управления подключен ко входу делителя 6 частоты, выход которого в свою очередь подключен ко входу блока 5 измерения частоты, а также ко второму входу частотно-фазового детектора 4. Схема работает следующим образом. В качестве источника входного сигнала взят опорный генератор 1, однако вместо него может быть применен любой другой источник периодических колебаний. При отклонении выходной частоты объекта 9 управления от частоты входного сигнала на выходе частотно-фазового детектора 4 появляется кодовая последовательность, соответствующая величине выявленного фазового рассогласования между входным и подстраиваемым сигналами системы. Частотно-фазовый детектор 4 выполнен на триггерах с применением оцифровки выявленной разности фаз и работает по принципу запоминания и хранения информации. Оцифровка разности фаз в частотно-фазовом детекторе 4 осуществляется путем заполнения промежутка между фронтами входных импульсов блока колебаниями высокой частоты с последующим их подсчетом и формированием двоичного кода учитывающего знак выявленной разности фаз. В то же время на выходах блоков 3 и 5 измерения частоты формируются кодовые последовательности, соответствующие длительности периодов входного и подстраиваемого колебаний соответственно. Метод оцифровки временных промежутков в данном случае аналогичен кодированию разности фаз в частотнофазовом детекторе 4. Сформированные блоками 3 и 5 кодовые последовательности поступают на сравнивающий блок 11. Блок 11 выявляет разность между входными последовательностями, после чего устанавливает, превосходит ли полученная величина заранее заданное значение , величина которого выбирается с учетом инерционности объекта 9 управления и системы в целом (для безинерционного объекта это значение может соответствовать величине так называемой пятипроцентной трубки, или например 10 Гц). Чем выше инерционность системы, тем большее значение параметраследует выбирать. В том случае, когда разность между входными последовательностями сравнивающего блока 11 превосходит , устанавливается необходимость значительной перестройки частоты объекта 9 управления, т.е. переход системы в режим автоматической подстройки частоты, который характеризуется заменой управляющего сигнала ЦСФС на максималь 5 13663 1 2010.10.30 ное значение управляющего воздействия с целью наискорейшей подстройки частоты объекта 9 управления к частоте входного сигнала. В этом случае на выходе 1 сравнивающего блока 11 устанавливается сигнал с уровнем логической 1, который запускает таймер 13 и переключает ключ 16 таким образом, чтобы на его выход проходил сигнал со входа К 2. В тот же момент на выходе 2 сравнивающего блока 11 устанавливается логический сигнал- илив зависимости от установленного направления необходимой перестройки частоты объекта 9 управления (т.е. от того, какое из пришедших на входы блока 11 значений больше). Запоминающее устройство 12 хранит значение максимально допустимого управляющего воздействия на объект 9 управления, установленное из его технических характеристик. Это значение совместно с сигналом на выходе 2 блока 11 поступает на умножающий блок 15, в результате чего на его выходе формируется максимально допустимый по величине управляющий сигнал, по необходимости направленный в сторону уменьшения, либо увеличения частоты выходных колебаний, которое поступает на вход К 2 ключа 16. При наличии на управляющем входе 1 ключа 16 уровня логической 1 на его выход проходит сигнал со входа К 2 после чего последний в преобразованном виде подается на блок 10 управляемых генераторов тока, который в свою очередь, согласно полученной информации, формирует в данном случае управляющий сигнал максимально допустимой амплитуды, поступающий через фильтр 8 нижних частот на управляющий вход объекта 9 управления. Блок 6 управляемых генераторов тока заряда/разряда представляет собой устройство, состоящее из двух последовательно соединенных генераторов тока заряда и разряда, генерирующих в соответствии с управляющим сигналом токи заряда и разряда (см. 3). Таким образом, на управляющий вход объекта 9 поступает сигнал максимально допустимой амплитуды, направленный в сторону изменения частоты входного сигнала таким образом, чтобы приближать частоту выходных колебаний к частоте входного сигнала с максимально возможной скоростью. Это продолжается до тех пор, пока разность частот между входным и подстраиваемым колебаниями не становится равной величине . Когда разность частот между входным и подстраиваемым колебанием перестает превосходить значение , система переходит в режим фазовой автоподстройки частоты, в котором управление объектом 9 осуществляется сигналом, сформированным частотно-фазовым детектором 4 с учетом динамического коэффициента усиления. В этом случае на выходе 1 сравнивающего блока 11 устанавливается сигнал с уровнем логической 0, который останавливает таймер 13 и переключает ключ 16 таким образом, чтобы на его выход проходил сигнал со входа К 1. Частотно-фазовый детектор 4 формирует кодовую последовательность, содержащую информацию о выявленном фазовом рассогласовании в соответствии с нелинейной внутренней характеристикой данного блока, наиболее применяемые из которых рассмотрены в различных источниках, например 1. Выходная кодовая последовательность частотно-фазового детектора 4 поступает на вход вычисляющего блока 14, который производит подсчет величины управляющего воздействия путем перемножения входного значения на дополнительный динамический коэффициент усиления кольца фазовой синхронизации , определяемый по следующему выражению(1)0,80,1315,где- длительность последнего интервала времени, на котором система находилась в режиме автоматической подстройки частоты. Значениеподсчитывается таймером 13,запуск и остановка которого осуществляется сигналом с выхода 1 сравнивающего блока 11,счет осуществляется за период времени, в течение которого на упомянутом выходе установлено значение логической 1. В том случае, если 0 величинеприсваивается значение 1. Формула (1) получена опытным путем. Вычисленное таким образом управляющее воздействие поступает на вход К 1 ключа 16 и во время нахождения системы в режиме фазовой автоподстройки частоты подается на блок 10 управляемых генераторов тока, в результате чего воздействует на объект 9 управления. 6 13663 1 2010.10.30 Цифровое моделирование предложенной структурной схемы ЦСФС показало, что применение нелинейного корректирующего устройства с динамическим коэффициентом усиления значительно (в среднем в 3-10 раз) сокращает длительность переходного процесса в сравнении с прототипом. При этом указанная особенность проявляется тем сильнее, чем значительнее рассогласование входного и подстраиваемого сигналов. На фиг. 2 пример переходного процесса в ЦСФС с нелинейным корректирующим устройством обозначен 1, а пример переходного процесса в ЦСФС построенной в соответствии с прототипом обозначен 2. Новизна предлагаемого изобретения заключается в следующем в цепи управления предлагается использовать нелинейное корректирующее устройство, при значительном рассогласовании частот заменяющее управляющий сигнал на максимально допустимый, что позволяет производить перестройку частоты с максимальной скоростью совместно с нелинейным корректирующим устройством предлагается использовать динамический коэффициент усиления, вычисляемый по изобретенной формуле (1), который позволяет в значительной степени унифицировать систему в целом, сделать ее значительно более широкополосной и универсальной в плане выбора объекта регулирования. Источники информации 1. Шахгильдян В.В., Ляховкин А.А. Системы фазовой автоподстройки частоты. - М. Связь, 1972. 2. Патент 2267860. Синтезатор частот с переменными усилением и полосой пропускания кольца фазовой автоподстройки, МПК 03 7/107, 01.09.2003. 3. Патент 5055803. - - . //. . -28,11 , 1980. - . 1849-1858. Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20. 7

МПК / Метки

МПК: H03L 7/00

Метки: характеристик, синхронизации, динамических, системы, цифровой, фазовой, улучшения, способ, устройство

Код ссылки

<a href="https://by.patents.su/7-13663-sposob-i-ustrojjstvo-dlya-uluchsheniya-dinamicheskih-harakteristik-cifrovojj-sistemy-fazovojj-sinhronizacii.html" rel="bookmark" title="База патентов Беларуси">Способ и устройство для улучшения динамических характеристик цифровой системы фазовой синхронизации</a>

Предыдущий патент: Способ построения и обновления фонового кадра для обнаружения движущихся объектов в системе видеонаблюдения

Следующий патент: Способ плазменного напыления покрытия

Случайный патент: Запорное устройство для крышек наливных люков цистерн