Сумматор-накопитель

Номер патента: 7066

Опубликовано: 30.06.2005

Авторы: Герасименя Николай Иванович, Осипов Анатолий Николаевич, Бондарик Василий Михайлович, Достанко Анатолий Павлович

Текст

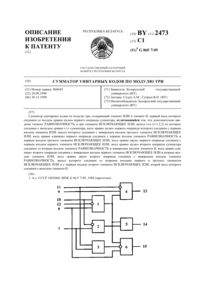

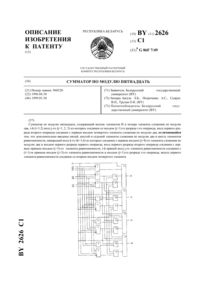

(51) С 061 71494150 НАЦИОНАЛЬНЫЙ ЦЕНтР ИНТЕЛЛЕКТУАЛЬНОИ СОБСТВЕННОСТИ(71) Заявитель Учреждение образования Белорусский государственный университет информатики и радиоэлектроники (ВУ)(72) Авторы Осипов Анатолий Николаевич Достанко Анатолий Павлович Бондарик Василий Михайлович(73) Патентообладатель Учреждение обра зования Белорусский государственный университет информатики и радиоэлектроники (ВУ)ПЕРВЫЙ арифметический бЛОК, ПЕРВЫЙ ВХОД КОТОРОГО СОЕДИНЕН СО ВХОДОМ устройства, а ПЕРВЫЙ ВЫХОД - С ПЕРВЫМ ВХОДОМ ПЕРВОГО регистра, ВЫХОД КОТОРОГО СОЕДИНЕН С ПЕРВЫМ ВХОДОМ ВТОРОГО регистра, ВЫХОД КОТОРОГО СОЕДИНЕН СО ВТОРЫМ ВХОДОМ ПЕРВОГО арифметиЧЕСКОГО блока, ВТОРЫЕ ВХОДЫ ПЕРВОГО И ВТОРОГО РЕГИСТРОВ СОЕДИНЕНЬ 1 С ПЕРВЫМ ВЫХОДОМ тактового генератора, ВТОРОЙ ВЫХОД КОТОРОГО СОЕДИНЕН С ТРЕТЬИМИ входами ПЕРВОГО И ВТОРОГО РЕГИСТРОВ, ОТЛИЧЯЮЩИЙСЯ ТЕМ, ЧТО ДОПОЛНИТЕЛЬНО СОДЕРЖИТ ТРЕТИЙ, ЧЕТВЕРТЫЙ, ПЯТЫЙ, Регистр 5Шестой регистры И второй арифметический блок, выход которого соединен с выходом устройства, а первый вход - с выходом пятого регистра, первый вход которого соединен с выходом первого регистра, второй вход второго арифметического блока соединен с вь 1 ходом Шестого регистра, первый вход которого соединен с выходом третьего регистра и первым входом Четвертого регистра, первый выход тактового генератора соединен со вторыми входами третьего и четвертого регистров, второй выход - с третьими входами третьего и четвертого регистров, а третий выход - со вторыми входами пятого и Шестого регистров, выход четвертого регистра соединен с третьим входом первого арифметического блока, второй выход которого соединен с первым входом третьего регистра.Изобретение относится к области вычислительной техники и может быть использовано в системах передачи дискретных сообщений для цифровой фильтрации, в системах поиска, синхронизации и т.д.Известны накапливающие сумматоры, предназначенные для суммирования-накопления входных чисел. Эти устройство содержат триггер со счетным входом, элементы И и ИЛИ, сумматор по модулю два и элементы задержки 2-8. Недостатком таких устройств является их сложность.Наиболее близким техническим решением к предлагаемому является устройство 1,включающее арифметический блок, тактовый генератор, первый и второй регистры. С частотой тактовых импульсов компоненты сигнального вектора 5(1) поступают на вход арифметического блока. Частота поступления компонентов определяется временем обработки данных в арифметическом блоке. Перед началом суммирования-накопления сигнал с тактового генератора обнуляет содержимое регистров. Арифметический блок производит поочередно суммирование значений сигнала с входа и предыдущих значений суммирования, накопленных в регистрегде Хд - значение сигнала на входе устройства, У - значение сигнала на выходе арифметического блока, Ум - значение суммирования, полученное в предыдущем такте. Результаты суммирования поступают на выход устройства через Ы тактов. В следующие Ы тактов происходит суммирование второй последовательности отсчетов сигнального вектора. Недостатком такого устройства является низкое быстродействие, определяемое бь 1 стродействием операции сложения на арифметическом блоке.Задачей настоящего изобретения является увеличение быстродействия устройства.Задача достигается тем, что в сумматор-накопитель, содержащий первый и второй регистры, тактовый генератор и первый арифметический блок, первый вход которого соединен со входом устройства, а первый выход - с первым входом первого регистра, выход которого соединен с первым входом второго регистра, выход которого соединен со вторым входом первого арифметического блока, вторые входы первого и второго регистра соединены с первым выходом тактового генератора, второй выход которого соединен с третьими входами первого и второго регистров, дополнительно включены третий, четвертый, пятый, Шестой регистры и второй арифметический блок, выход которого соединен с выходом устройства, а первый вход - с выходом пятого регистра, первый вход которого соединен с выходом первого регистра, второй вход второго арифметического блока соединен с выходом Шестого регистра, первый вход которого соединен с выходом третьего регистра и первым входом четвертого регистра, первый выход тактового генератора соединен со вторыми входами третьего и четвертого регистров, второй выход - с третьими входами третьего и четвертого регистров, а третий выход - со вторыми входами пятого и Шестого регистров, выход четвертого регистра соединен с третьим входом первого арифметического блока, второй выход которого соединен с первым входом третьего регистра.Сущность Изобретения заключается в том, что для накопления результатов используется арифметический блок, выполняющий преобразование операции сложения трех чисел в двоичной позиционной системе счисления в операцию сложения двух чисел. При этом время преобразования не зависит от длины обрабатываемых чисел, что позволяет увеличить частоту поступления отсчетов сигнального вектора в устройство.На фиг. 1 приведена структурная схема сумматора-накопителя, на фиг. 2 - временные диаграммы работы сумматора-накопителя.Сумматор-накопитель содержит (фиг. 1) первый арифметический блок 1, первый вход которого соединен со входом устройства, а первый выход - с первым входом первого регистра 2, выход которого соединен с первым входом второго регистра 3, выход второго регистра соединен со вторым входом первого арифметического блока 1, вторые входы первого 2, второго 3, третьего 4 и четвертого 5 регистров соединены с первым выходом тактового генератора 6, второй выход которого соединен с третьими входами первого 2,второго 3, третьего 4 и четвертого 5 регистров, пятый 7, Шестой 8 регистры и второй арифметический блок 9, выход которого соединен с выходом устройства, а первый вход с выходом пятого регистра 7, первый вход которого соединен с выходом первого регистра 2,второй вход второго арифметического блока 9 соединен с выходом Шестого регистра 8,первый вход которого соединен с выходом третьего регистра 4 и первым входом четвертого регистра 5, третий выход тактового генератора 6 соединен со вторыми входами пятого 7 и Шестого 8 регистров, выход четвертого регистра 5 соединен с третьим входом первого арифметического блока 1, второй выход которого соединен с первым входом третьего регистра 4.Рассмотрим работу устройства. Арифметический блок 1 реализует преобразование операции сложения трех чисел, представленных в двоичной позиционной системе счисления, в операцию сложения двух чисел. Данное преобразование описывается следующими уравнениямиКак следует из (2), значения 1-го разряда числа Х 1 зависят и определяются только из значений 1-х разрядов чисел Х 1, Х 2, Х 3, а значения 1-го разряда числа Х 2 определяются и зависят только от значений (1-1)-х разрядов чисел Х 1, Х 2, Х 3 и не зависят от значений предыдущих разрядов. Следовательно, время преобразования не зависит от длины обрабать 1 ваемых чисел. Реализация арифметического блока 1 известна. На фиг. 2 приведен один из возможных вариантов реализации арифметического блока 1. В этом случае операнды Х 1 д,Хд, Х 3 д поступают на соответствующие входы арифметического блока. На элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 14 и 15 осуществляется вычисление числа Х 1 в соответствии с(2), а на элементах И 10, 11, 12 и ИЛИ 13 блоков А 1 - число Х 2. Таким образом арифметический блок 1 выполняет преобразование операции сложения трех чисел в операцию сложения двух чисел. Время преобразования о операции сложения трех чисел в два числа равно времени вычисления одного разряда результата в сумматоре с последовательным переносом 3.На вход устройства (фиг. 1) последовательно поступают отсчеты Х 1, Х 2 Хы, которые необходимо просуммировать. В начале работы сигнал с третьего выхода тактового генератора 6 обнуляет содержимое регистров 2, 3, 4, 5. Одновременно первый операнд Х 1 поступает на вход устройства. Данный отсчет и нулевое содержимое регистров 3 и 5 преобразуются в арифметическом блоке 1 в два числа в соответствии с (2). По переднему фронту сигнала с первого выхода тактового генератора 6 вычисленные числа заносятсясоответственно в регистры 2 И 4, а по заднему фронту данные числа из регистров 2 И 4 переписываются в регистры 3 и 5. Регистры 3 и 5 предназначены для хранения результатов сложения, полученных в предыдущих тактах. В следующем такте работы аналогичным образом поступившее на вход устройства число Х 2 складывается в блоке 1 с содержимым регистров 3 и 5. Результат сложения представляется двумя числами, сумма которых есть искомый результат. Таким образом на выходе блока 1 в 1-м такте работы устройства появляется два числа Хш и Хт 1Окончательное сложение результатов, полученных на выходе блока 1 после обработки М чисел, выполняется в арифметическом блоке 9. Для этого на вторые входы регистров 7 и 8 поступает сигнал с тактового генератора 6, который разрешает перезапись данных из регистров 2 и 4 соответственно в регистры 7 и 8. Блок 9 может быть реализован по известной схеме как сумматор с последовательным переносом. Результат накопления чисел Х 1, Х 2, Хм поступает на выход устройства. Следует отметить, что во время обработки данных в блоке 9 арифметический блок 1 готов накапливать очередные входные данные.Для известного устройства 2 частота поступления отсчетов определяется выражениемгде 1 - количество разрядов одного отсчета, о - время вычисления одного разряда при суммировании входных данных.Если время суммирования (гп) в арифметическом блоке 9 меньше времени накопления(ц) Ы чисел в блоке 1 (фиг. 2, а), то накопление следующих Ы чисел в блоке 1 можно начинать сразу после начала суммирования в арифметическом блоке 9 до окончания Цикла работы сумматора-накопителя. В этом случае частота поступления данных в устройство равнаПри ц П (1 М) обработку новых отсчетов в арифметическом блоке 1 нельзя начинать одновременно с началом суммирования в блоке 9 (фиг. 2, б). При синхронном поступлении отсчетов сигнального вектора (без пауз) необходимо, чтобы ц гп. ТогдаУвеличение частоты поступления данных для первого (5) и второго (6) случаев в сравнении с известным устройством составляет соответственно

МПК / Метки

Метки: сумматор-накопитель

Код ссылки

<a href="https://by.patents.su/5-7066-summator-nakopitel.html" rel="bookmark" title="База патентов Беларуси">Сумматор-накопитель</a>

Предыдущий патент: Деформатор кручения витых структур

Следующий патент: Способ лечения профессиональной экземы

Случайный патент: Транспортирующий патрон пневмопочты