Одноразрядный десятичный сумматор

Номер патента: 2627

Опубликовано: 30.03.1999

Авторы: Супрун Валерий Павлович, Авгуль Леонид Болеславович, Петроченко Андрей Сергеевич, Курносенко Сергей Васильевич

Текст

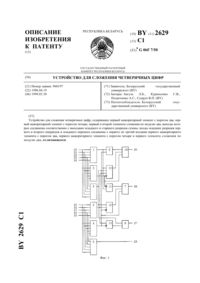

ГОСУДАРСТВЕННЫЙ ПАТЕНТНЫЙ КОМИТЕТ РЕСПУБЛИКИ БЕЛАРУСЬ(71) Заявитель Белорусский государственный университет(73) Патентообладатель Белорусский государственный университет(57) Одноразрядный десятичный сумматор, содержащий пять элементов сложения по модулю два и четыре элемента И, отличающийся тем, что дополнительно введены шестой и седьмой элементы сложения по модулю два, пятый, шестой, седьмой и восьмой элементы И, два элемента ЗАПРЕТ, мажоритарный элемент с порогом два, мажоритарный элемент с порогом четыре, мажоритарный элемент с порогом шесть и два элемента ИЛИ-НЕ, -й вход го из которых (1,2 1,2) соединен с -м входом -го элемента сложения по модулю два, -м входом -го элемента И и входом -го разряда -го операнда, вход третьего разряда -го операнда соединен с (2-1)-м и 2-м входами мажоритарного элемента с порогом два, (2-1)-м и 2-м входами мажоритарного элемента с порогом четыре 2627 1 и (2-1)-м и 2-м входами мажоритарного элемента с порогом шесть, вход четвертого разряда -го операнда соединен с (4)-м входом мажоритарного элемента с порогом два, (4)-м входом мажоритарного элемента с порогом четыре, (4)-м входом мажоритарного элемента с порогом шесть и -м входом третьего элемента сложения по модулю два, вход переноса из младшего десятичного разряда соединен с седьмым входом мажоритарного элемента с порогом два, седьмым входом мажоритарного элемента с порогом четыре, седьмым входом мажоритарного элемента с порогом шесть и третьим входом третьего элемента сложения по модулю два, выход первого элемента ИЛИ-НЕ соединен с первым входом третьего элемента И, первым входом четвертого элемента И, первым входом четвертого элемента сложения по модулю два и первым входом пятого элемента сложения по модулю два, выход второго элемента ИЛИ-НЕ соединен с первым прямым входом первого элемента ЗАПРЕТ и вторым входом четвертого элемента И, выход первого элемента сложения по модулю два соединен со вторым прямым входом первого элемента ЗАПРЕТ и первым прямым входом второго элемента ЗАПРЕТ, выход второго элемента сложения по модулю два соединен с первым входом пятого элемента И, вторым входом третьего элемента И, вторым прямым входом второго элемента ЗАПРЕТ и первым входом шестого элемента сложения по модулю два, выход первого элемента И соединен с первым входом шестого элемента И и вторым входом шестого элемента сложения по модулю два, выход второго элемента И соединен с первым входом седьмого элемента И, первым входом восьмого элемента И и первым входом седьмого элемента сложения по модулю два, выход мажоритарного элемента с порогом два соединен со вторым входом шестого элемента И, вторым входом седьмого элемента И, входом запрета первого элемента ЗАПРЕТ, входом запрета второго элемента ЗАПРЕТ и вторым входом пятого элемента сложения по модулю два, выход мажоритарного элемента с порогом четыре соединен с третьим входом третьего элемента И, третьим входом четвертого элемента И и третьим входом пятого элемента сложения по модулю два, выход мажоритарного элемента с порогом шесть соединен со вторым входом пятого элемента И, вторым входом восьмого элемента И и четвертым входом пятого элемента сложения по модулю два, выход пятого элемента И соединен со вторым входом седьмого элемента сложения по модулю два, пятым входом пятого элемента сложения по модулю два и вторым входом четвертого элемента сложения по модулю два, инверсный выход которого соединен с выходом переноса сумматора, а третий вход соединен с выходом первого элемента ЗАПРЕТ, третьим входом седьмого элемента сложения по модулю два и шестым входом пятого элемента сложения по модулю два, четвертый вход соединен с выходом седьмого элемента И, четвертым входом седьмого элемента сложения по модулю два и седьмым входом пятого элемента сложения по модулю два, выход третьего элемента И соединен с третьим входом шестого элемента сложения по модулю два и пятым входом седьмого элемента сложения по модулю два,выход которого соединен с выходом первого разряда суммы сумматора, а шестой вход соединен с выходом шестого элемента И и четвертым входом шестого элемента сложения по модулю два, пятый вход которого соединен с выходом четвертого элемента И, шестой вход - с выходом восьмого элемента И, седьмой вход - с выходом второго элемента ЗАПРЕТ, а выход - с выходом второго разряда суммы сумматора, выход третьего разряда суммы которого соединен с инверсным выходом пятого элемента сложения по модулю два, выход четвертого разряда суммы соединен с выходом третьего элемента сложения по модулю два. Изобретение относится к вычислительной технике и микроэлектронике и предназначено для построения арифметическо - логических устройств высокопроизводительных ЭВМ и спецпроцессоров, выполняющих обработку двоично-десятичных чисел. Известен двоично-десятичный сумматор, содержащий в каждом разряде 2 тетрадных двоичных сумматора, узел коррекции, элемент И, 5 элементов ИЛИ, 2 элемента сложения по модулю два 1. Недостатком сумматора является низкое быстродействие. Наиболее близким по функциональным возможностям и конструкции техническим решением к предлагаемому является одноразрядный десятичный сумматор, содержащий четырехразрядный двоичный сумматор, четыре элемента И, элемент ИЛИ, элемент НЕ и пять элементов сложения по модулю два 2. Недостатком известного одноразрядного десятичного сумматора является низкое быстродействие. Изобретение направлено на решение задачи повышения быстродействия одноразрядного десятичного сумматора. Поставленная задача решается тем, что в одноразрядный десятичный сумматор, содержащий пять элементов сложения по модулю два и четыре элемента И, согласно изобретению дополнительно введены шестой и седьмой элементы сложения по модулю два, пятый, шестой, седьмой и восьмой элементы И, два элемента ЗАПРЕТ, мажоритарный элемент с порогом два, мажоритарный элемент с порогом четыре,мажоритарный элемент с порогом шесть и два элемента ИЛИ-НЕ, -й вход -го из которых (1,2 ,2) соединен с -м входом -го элемента сложения по модулю два, -м входом -го лемента И и входом -го разряда-го операнда, вход третьего разряда -го операнда соединен с (2-1)-м и 2-м входами мажоритарного эле 2 2627 1 мента с порогом два, (2-1)-м и 2-м входами мажоритарного элемента с порогом четыре и (2-1)-м и 2-м входами мажоритарного элемента с порогом шесть, вход четвертого разряда -го операнда соединен с (4)-м входом мажоритарного элемента с порогом два, (4)-м входом мажоритарного элемента с порогом четыре,(4)-м входом мажоритарного элемента с порогом шесть и -м входом третьего элемента сложения по модулю два, вход переноса из младшего десятичного разряда соединен с седьмым входом мажоритарного элемента с порогом два, седьмым входом мажоритарного элемента с порогом четыре, седьмым входом мажоритарного элемента с порогом шесть и третьим входом третьего элемента сложения по модулю два, выход первого элемента ИЛИ-НЕ соединен с первым входом третьего элемента И, первым входом четвертого элемента И, первым входом четвертого элемента сложения по модулю два и первым входом пятого элемента сложения по модулю два, выход второго элемента ИЛИ-НЕ соединен с первым прямым входом первого элемента ЗАПРЕТ и вторым входом четвертого элемента И, выход первого элемента сложения по модулю два соединен со вторым прямым входом первого элемента ЗАПРЕТ и первым прямым входом второго элемента ЗАПРЕТ, выход второго элемента сложения по модулю два соединен с первым входом пятого элемента И,вторым входом третьего элемента И, вторым прямым входом второго элемента ЗАПРЕТ и первым входом шестого элемента сложения по модулю два, выход первого элемента И соединен с первым входом шестого элемента И и вторым входом шестого элемента сложения по модулю два, выход второго элемента И соединен с первым входом седьмого элемента И, первым входом восьмого элемента И и первым входом седьмого элемента сложения по модулю два, выход мажоритарного элемента с порогом два соединен со вторым входом шестого элемента И, вторым входом седьмого элемента И, входом запрета первого элемента ЗАПРЕТ,входом запрета второго элемента ЗАПРЕТ и вторым входом пятого элемента сложения по модулю два, выход мажоритарного элемента с порогом четыре соединен с третьим входом третьего элемента И, третьим входом четвертого элемента И и третьим входом пятого элемента сложения по модулю два, выход мажоритарного элемента с порогом шесть соединен со вторым входом пятого элемента И, вторым входом восьмого элемента И и четвертым входом пятого элемента сложения по модулю два, выход пятого элемента И соединен со вторым входом седьмого элемента сложения по модулю два, пятым входом пятого элемента сложения по модулю два и вторым входом четвертого элемента сложения по модулю два, инверсный выход которого соединен с выходом переноса сумматора, а третий вход соединен с выходом первого элемента ЗАПРЕТ, третьим входом седьмого элемента сложения по модулю два и шестым входом пятого элемента сложения по модулю два, четвертый вход соединен с выходом седьмого элемента И, четвертым входом седьмого элемента сложения по модулю два и седьмым входом пятого элемента сложения по модулю два,выход третьего элемента И соединен с третьим входом шестого элемента сложения по модулю два и пятым входом седьмого элемента сложения по модулю два, выход которого соединен с выходом первого разряда суммы сумматора, а шестой вход соединен с выходом шестого элемента И и четвертым входом шестого элемента сложения по модулю два, пятый вход которого соединен с выходом четвертого элемента И, шестой вход - с выходом восьмого элемента И, седьмой вход - с выходом второго элемента ЗАПРЕТ, а выход - с выходом второго разряда суммы сумматора, выход третьего разряда суммы которого соединен с инверсным выходом пятого элемента сложения по модулю два, выход четвертого разряда суммы соединен с выходом третьего элемента сложения по модулю два. На чертеже (фиг. 1) представлена функциональная схема одноразрядного десятичного сумматора. Сумматор содержит два элемента ИЛИ-НЕ 1 и 2, семь элементов сложения по модулю два 3-9, восемь элементов И 10-17, мажоритарный элемент с порогом два 18, мажоритарный элемент с порогом четыре 19,мажоритарный элемент с порогом шесть 20, два элемента ЗАПРЕТ 21 и 22, входы разрядов 23-26 первого десятичного операнда, входы разрядов 27-30 второго десятичного операнда, вход переноса 31 из младшего десятичного разряда, выход переноса 32 в старший десятичный разряд, выходы разрядов суммы 33-36. Одноразрядный десятичный сумматор работает следующим образом. На входы 23, 24. 25 и 26 поступают соответственно первый х 1, второй х 2, третий х 3 и четвертый х 4 разряды первого операнда Х 8 х 1422 х 3 х 4 на- входы 27, 28, 29 и 30- соответственно первый 1,второй 2, третий з и четвертый у 4 разряды второго операнда 81422 узу 4 на вход 31 - перенос с из соседнего младшего десятичного разряда. На выходе 32 формируется переносв соседний старший десятичный разряд, на выходах 33, 34, 35 и 36- соответственно значения первого 1, второго 2, третьего 3 и четвертого 4 разрядов суммы 8142234. Таким образом, сумматор выполняет сложение двух десятичных цифр с учетом переноса из соседнего младшего десятичного разряда. Работа одноразрядного десятичного сумматора описывается приводимой ниже таблицей (фиг. 2). Достоинством одноразрядного десятичного сумматора является высокое быстродействие, которое определяется глубиной схемы и равно 3, где- задержка на вентиль. Государственный патентный комитет Республики Беларусь. 220072, г. Минск, проспект Ф. Скорины, 66.

МПК / Метки

МПК: G06F 7/50

Метки: десятичный, одноразрядный, сумматор

Код ссылки

<a href="https://by.patents.su/4-2627-odnorazryadnyjj-desyatichnyjj-summator.html" rel="bookmark" title="База патентов Беларуси">Одноразрядный десятичный сумматор</a>

Предыдущий патент: Устройство для формирования остатка по модулю 2n-1

Следующий патент: Способ получения композиции на основе сложного полиэфира

Случайный патент: Устройство для прокатки, в частности, клеть для ассиметричной прокатки