Многовходовый одноразрядный сумматор

Номер патента: 5353

Опубликовано: 30.09.2003

Авторы: Авгуль Леонид Болеславович, Петроченко Андрей Сергеевич, Супрун Валерий Павлович

Текст

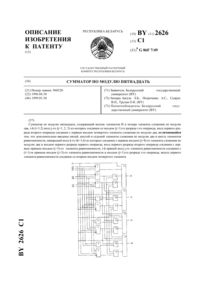

(12) НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ(71) Заявитель Белорусский государственный университет(72) Авторы Авгуль Леонид Болеславович Петроченко Андрей Сергеевич Супрун Валерий Павлович(73) Патентообладатель Белорусский государственный университет(57) Многовходовый одноразрядный сумматор, содержащийэлементов сложения по модулю два, в которомопределено по формуле 2,где 21 - разрядность входного двоичного слова 1, 2, 3,выход -го элемента сложения по модулю два (1,2) соединен с -м выходом сумматора,-й информационный вход (1, 2 ) которого соединен с -м входом первого элемента сложения по модулю два, отличающийся тем, что содержит (1)-й элемент сложения по модулю два, элемент ИЛИ имажоритарных элементов, -й из которых (1, 2 ) имеет порог,равный 21, при этом выход (р 1)-го элемента сложения по модулю два соединен (р 1)-м 5353 1 выходом сумматора, -й информационный вход которого соединен с -м входом элемента ИЛИ и -м входом -го мажоритарного элемента, управляющий вход сумматора соединен с (1)-м входом элемента ИЛИ, (1)-м входом -г мажоритарного элемента и первым входом (1)го элемента сложения по модулю два, второй вход которого соединен с выходом элемента ИЛИ, (2)-й вход (1, 2 /) (1)-го элемента сложения по модулю два соединен с выходом (2-1)-го мажоритарного элемента.(56)2047216 1, 1995.2305 1, 1998.2021630 1, 1994.1068932 , 1984.1827671 1, 1993.02207323 , 1990.0353041 2, 1990.01304532 , 1989. Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано для построения быстродействующих арифметическо-логических устройств ЭВМ и специализированных процессоров. Известен многовходовый одноразрядный сумматор, содержащий преобразователи двоичных кодов в унитарные и блок суммирования унитарных кодов 1. Недостатком устройства является низкое быстродействие, а также формирование на выходах унитарного кода, затрудняющее применение сумматора при построении арифметических устройств. Наиболее близким по функциональным возможностям и конструкции техническим решением к предлагаемому является многовходовый одноразрядный сумматор, содержащийэлементов сложения по модулю два (2,- разрядность входного двоичного слова) имажоритарных элементов (/2), -й из которых (1, 2 ) имеет порог, равный 2 2. На выходах сумматора формируется позиционный двоичный код числа единиц, содержащихся во входном двоичном слове. Недостатком известного многовходового одноразрядного сумматора является ограниченные функциональные возможности, поскольку он не обеспечивает формирование дополнительного кода результата. Изобретение направлено на решение задачи расширения функциональных возможностей многовходового одноразрядного сумматора за счет формирования прямого и дополнительного кодов числа единиц, содержащихся во входном двоичном слове. Названный технический результат достигается путем введения в состав сумматора дополнительно элемента ИЛИ, элемента сложения по модулю два, мажоритарных элементов с нечетными порогами, а также изменением связей между элементами сумматора. Многовходовый одноразрядный сумматор содержитэлементов сложения по модулю два, в которомопределено по формуле 2, где 21 - разрядность входного двоичного слова,1, 2, 3, Выход -го элемента сложения по модулю два (1, 2 ) соединен с -м выходом сумматора. В сумматоре -й информационный вход (1, 2 ) соединен с -м входом первого элемента сложения по модулю два. В отличие от прототипа сумматор содержит (1)-й элемент сложения по модулю два, элемент ИЛИ имажоритарных элементов, -й из которых (1, 2 ) имеет порог, равный 2. Выход (1)-го элемента сложения по модулю два соединен с (1)м выходом сумматора, -й информационный вход которого соединен с -м входом элемента ИЛИ и -м входом -го мажоритарного элемента. Управляющий вход сумматора соеди 2 5353 1 нен с (1)-м входом элемента ИЛИ, (1)-м входом -го мажоритарного элемента и первым входом (1)-го элемента сложения по модулю два, второй вход которого соединен с выходом элемента ИЛИ. Выход (2-1)-го мажоритарного элемента соединен с(2)-м входом (1)-го элемента сложения по модулю два (1, 2 /). На фиг. 1 представлена схема многовходового одноразрядного сумматора при 11. При 11 (21,5) сумматор содержит 14 (2/3) элементов сложения по модулю два 1-4, элемент ИЛИ 5,5 мажоритарных элементов 6-10,11 информационных входов 11-21, управляющий вход 22,14 выхода. При этом мажоритарные элементы 6, 7, 8, 9 и 10 имеют пороги соответственно три, пять, семь, девять и одиннадцать. Предлагаемый многовходовый одноразрядный сумматор работает в двух режимах режиме формирования прямого кода и режиме формирования дополнительного кода числа единиц, содержащихся во входном двоичном слове(1, 2 ). Выбранный режим определяется значением сигнала, подаваемого на управляющий вход сумматора. В режиме формирования прямого кода числа единиц на управляющий вход сумматора подается сигнал 1, а на информационные входы - двоичные переменные 1-. На выходах сумматора формируется (1)-разрядный позиционный двоичный код (, -10) числа (0) единиц во входном слове Х 1222-1-1210. В режиме формирования дополнительного кода числа единиц на управляющий вход сумматора подается сигнал 0, а на информационные входы - двоичные переменные 1-. На выходах сумматора формируется дополнительный (1)-разрядный позиционный двоичный код (, -1 0) числаединиц во входном словеСдоп.22-1-121 с 0,где 0, если 0 доп.1 2, если 1. Многовходовый одноразрядный сумматор при 11 (фиг. 1) работает следующим образом. На управляющий вход 22 подается сигнал , определяющий режим работы. На информационные входы 11-21 подаются двоичные переменные 1-11 (в произвольном порядке). На выходах 23-26 формируются соответственно сигналы 0-3 (при 1) или 0-с 3(при 0). Работа многовходового одноразрядного сумматора при 11 поясняется приводимой ниже таблицей (фиг. 2). Многовходовый одноразрядный сумматор при 11 построен в соответствии со следующими соотношениями 01211 9 312 ( ,)12 ( ,), где 0-3 - функции, реализуемые соответственно на выходах 23-26 сумматора Х(х 1, 2 11) - вектор входных двоичных переменных 12(, )1 х 211 - функция, реализуемая двенадцативходовым элементом ИЛИ 5 12 (, ) , 3, 5, 7, 9, 11 - функция, реализуемая двенадцативходовым мажоритарным элементом с порогом(элементы 6-10). 3 5353 1 Отметим, что функция, реализуемая -входовым мажоритарным элементом с порогом(1) определяется следующим образом 1, если 12( )0, если 12,где(1, 2) 10, 1,1, 2 . При 1 элемент ИЛИ 5 реализует функцию константа 1, поскольку 12(, )1 двенадцативходовые мажоритарные элементы с нечетными порогами 6-10 реализуют функции одиннадцативходовых мажоритарных элементов с четными порогами, меньшими на единицу 12 (1, )111 , (3, 5, 7, 9, 11. Следовательно, при вычислении прямого кода числа единиц (1) соотношения (1),описывающие работу сумматора, примут вид 01211 При 0 элемент ИЛИ 5 реализует функцию 12(0, )111 х 211 двенадцативходовые мажоритарные элементы с нечетными порогами 6-10 реализуют функции одиннадцативходовых мажоритарных элементов с нечетными порогами (такими же порогами) 12 (0, )11 , (3, 5, 7, 9, 11. Следовательно, при вычислении дополнительного кода числа единиц (0) соотношения (1), описывающие работу сумматора, примут вид с 01211 Без потери общности формула изобретения составлена для нечетных значений . Структура сумматора для четных значенийполучается из устройства при числе входов,равном 1, путем удаления избыточных конструктивных узлов. Достоинствами многовходового одноразрядного сумматора являются широкие функциональные возможности и высокое быстродействие. Источники информации 1. А.с. СССР 1068932, 1984. 2. Патент РФ 2047216, 1995. 5353 1 Таблица работы многовходового одноразрядного сумматора при 11 Сигнал на управляющем входе Вес входного слова Сигналы на выходах сумматора 1211 Входы 11-21 3(3)/26 2(2)/25 1(1)/24 0(0)/23 0 0 0 0 0 1 0 0 0 1 2 0 0 1 0 3 0 0 1 1 4 0 1 0 0 5 0 1 0 1 6 0 1 1 0 7 0 1 1 1 8 1 0 0 0 9 1 0 0 1 10 1 0 1 0 11 1 0 1 1 0 0 0 0 0 1 1 1 1 1 2 1 1 1 0 3 1 1 0 1 4 1 1 0 0 5 1 0 1 1 6 1 0 1 0 7 1 0 0 1 8 1 0 0 0 9 0 1 1 1 10 0 1 1 0 11 0 1 0 1 Фиг. 2 Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20. 5

МПК / Метки

МПК: G06F 7/50, G06F 7/49, G06F 7/00

Метки: многовходовый, одноразрядный, сумматор

Код ссылки

<a href="https://by.patents.su/5-5353-mnogovhodovyjj-odnorazryadnyjj-summator.html" rel="bookmark" title="База патентов Беларуси">Многовходовый одноразрядный сумматор</a>

Предыдущий патент: Способ сокращения сроков сервис-периода у коров

Следующий патент: Способ переработки кубовых остатков стадии ректификации производства капролактама

Случайный патент: Электрод заземлитель