Многовходовый одноразрядный сумматор по модулю три

Номер патента: 5352

Опубликовано: 30.09.2003

Текст

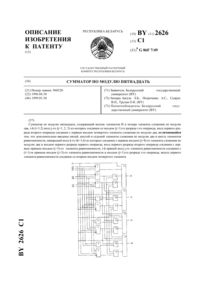

(12) НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ МНОГОВХОДОВЫЙ ОДНОРАЗРЯДНЫЙ СУММАТОР ПО МОДУЛЮ ТРИ(71) Заявитель Белорусский государственный университет(72) Авторы Авгуль Леонид Болеславович Супрун Валерий Павлович(73) Патентообладатель Белорусский государственный университет(57) Многовходовый одноразрядный сумматор по модулю три, содержащий три элемента сложения по модулю два и /2 мажоритарных элементов ( - разрядность входного слова,6,1, 2, 3,), -й (1, 2 /2) из которых имеет порог, равный 2, а г -й (1, 2 ) вход соединен-м входом первого элемента сложения по модулю два и -м входом сумматора, первый и второй выходы которого соединены с выходами второго и третьего элементов сложения по модулю два соответственно, отличающийся тем, что содержит две группы элементов ЗАПРЕТ по /3 элементов в каждой, причем прямой вход -г (1, 2 ) элемента ЗАПРЕТ первой группы соединен с выходом (3-2)-г мажоритарного элемента, а его вход запрета соединен с выходом (3-)-го мажоритарного элемента, первый прямой вход -г элемента ЗАПРЕТ первой группы соединен с выходом (3-2)-г мажоритарного элемента, второй прямой 5352 1 вход соединен с выходом первого элемента сложения по модулю два, а вход запрета соединен с выходом 3-г мажоритарного элемента, прямой вход -г элемента ЗАПРЕТ второй группы соединен с выходом (3-)-г мажоритарного элемента, а его вход запрета соединен с выходом 3-г мажоритарного элемента, первый прямой вход -г элемента ЗАПРЕТ второй группы соединен с выходом (3-2)-г мажоритарного элемента, второй прямой вход соединен с выходом первого элемента сложения по модулю два, а вход запрета соединен с выходом (3-)-г мажоритарного элемента, выход -г (1, 2 2) элемента ЗАПРЕТ -ой (1, 2) группы соединен с -м входом (1)-го элемента сложения по модулю два, (21)-й вход третьего элемента сложения по модулю два соединен с выходом первого элемента сложения по модулю два.(56)2047216 1, 1995.2305 1, 1998.2021630 1, 1994.1827671 1, 1993.02207323 , 1990.0353041 2, 1990.01304532 , 1989.62084336 , 1987. Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано для построения систем аппаратурного контроля и вычислительных устройств, реализующих алгоритмы модулярной арифметики. Известно устройство для формирования остатка по модулю три, содержащее два блока вычисления симметрических булевых функций, четыре элемента ИЛИ и сумматор по модулю три 1. Устройство формирует двухразрядный код результата свертки по модулю три входного -разрядного позиционного кода. Недостатком устройства является низкое быстродействие, определяемое большой глубиной схемы. Наиболее близким по конструкции и функциональным возможностям техническим решением к предлагаемому является многовходовый одноразрядный сумматор, содержащийэлементов сложения по модулю два (2,- разрядность входного слова) имажоритарных элементов (/2), -й из которых (1, 2 ) имеет порог, равный 2 2. Сумматор формирует позиционный двоичный код числа единиц, содержащихся во входном двоичном слове. Недостатком известного многовходового одноразрядного сумматора является невозможность вычисления суммы по модулю три числа единиц, содержащихся во входном двоичном слове. Изобретение направлено на решение задачи расширения функциональных возможностей многовходового одноразрядного сумматора за счет вычисления суммы по модулю три числа единиц, содержащихся во входном двоичном слове. Названный технический результат достигается путем введения в состав сумматора дополнительно двух групп элементов ЗАПРЕТ, а также изменением связей между элементами сумматора. Многовходовый одноразрядный сумматор по модулю три содержит три элемента сложения по модулю два и /2 мажоритарных элементов ( - разрядность входного слова,6,1, 2, 3,). При этом -й (1, 2 /2) мажоритарный элемент имеет порог,равный 2, а его -й (1, 2 ) вход соединен с -м входом первого элемента сложения 2 5352 1 по модулю два и -м входом сумматора. Первый и второй выходы сумматора соединены с выходами второго и третьего элементов сложения по модулю два соответственно. В отличие от прототипа сумматор содержит две группы элементов ЗАПРЕТ по /3 элементов в каждой. Прямой вход -го (1, 2 ) элемента ЗАПРЕТ первой группы соединен с выходом(3-2)-го мажоритарного элемента, а его вход запрета соединен с выходом (3-1)-го мажоритарного элемента. Первый прямой вход -го элемента ЗАПРЕТ первой группы соединен с выходом (3-2)-го мажоритарного элемента, второй прямой вход соединен с выходом первого элемента сложения по модулю два, а вход запрета соединен с выходом 3 -го мажоритарного элемента. Прямой вход -го элемента ЗАПРЕТ второй группы соединен с выходом (3-1)-го мажоритарного элемента, а его вход запрета соединен с выходом 3-го мажоритарного элемента. Первый прямой вход -го элемента ЗАПРЕТ второй группы соединен с выходом (3-2)-го мажоритарного элемента, второй прямой вход соединен с выходом первого элемента сложения по модулю два, а вход запрета соединен с выходом (3-1)-го мажоритарного элемента. Выход -го (1, 2 2) элемента ЗАПРЕТ -й (1, 2) группы соединен с -м входом (1)-го элемента сложения по модулю два, (21)-й вход третьего элемента сложения по модулю два соединен с выходом первого элемента сложения по модулю два. На чертеже (фиг. 1) представлена схема предлагаемого многовходового одноразрядного сумматора по модулю при 12 (2). Сумматор содержит три элемента сложения по модулю два 1, 2 и 3, /26 мажоритарных элементов 4-9 с порогами два, четыре, шесть, восемь, десять и двенадцать соответственно, 48 элементов ЗАПРЕТ 10-17 (24 элемента первой группы 11, 13, 15 и 17 24 элемента второй группы 10, 12, 14 и 16),12 входов 18-29, два выхода 30 и 31. Многовходовый одноразрядный сумматор по модулю три работает следующим образом. На входы 18-29 подаются двоичные переменные 112 (в произвольном порядке), на выходах 30 и 31 реализуются соответственно булевы функции 1 и 2 результата, значения которых составляют позиционный двоичный код суммы по модулю три 212 числа единиц , содержащихся во входном слове(1, 2 12)3(1 х 212)3212. Схема сумматора (фиг. 1) построена в соответствии со следующими соотношениями 12426810812 224 М 4 М 68 12, гдех 2 х 12- функция, реализуемая мажоритарным элементом с порогом , которая определяется следующим образом 2, 4, 6, 8, 10, 12) 1, если 1212( 1 ,2 , , 12 )0, если 1212. Работа многовходового одноразрядного сумматора по модулю три поясняется приводимой ниже таблицей (фиг. 2). Без потери общности формула изобретения составлена для значений , кратных шести(6,1, 2, 3,). Структура сумматора для других значенийполучается из устройства при числе входов, равном 6/6, путем удаления избыточных логических элементов и межсоединений в схеме. Достоинствами многовходового одноразрядного сумматора по модулю три является простая конструкция, высокое быстродействие и широкая область применения. 3 Таблица работы многовходового одноразрядного сумматора по модулю три 3212 1/30 2/31 0 0 0 1 1 0 0 0 0 1 1 0 0 0 0 1 1 0 0 0 0 1 1 0 0 0 Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20. 4

МПК / Метки

Метки: модулю, одноразрядный, многовходовый, три, сумматор

Код ссылки

<a href="https://by.patents.su/4-5352-mnogovhodovyjj-odnorazryadnyjj-summator-po-modulyu-tri.html" rel="bookmark" title="База патентов Беларуси">Многовходовый одноразрядный сумматор по модулю три</a>

Предыдущий патент: Устройство для умножения N чисел по модулю три

Следующий патент: Устройство для умножения по модулю семь

Случайный патент: Манипулятор