Устройство для сложения чисел в последовательном коде

Номер патента: 5079

Опубликовано: 30.03.2003

Авторы: Изотов Сергей Николаевич, Супрун Валерий Павлович, Петроченко Андрей Сергеевич, Авгуль Леонид Болеславович

Текст

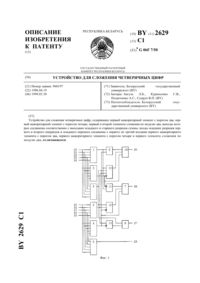

(12) НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ЧИСЕЛ В ПОСЛЕДОВАТЕЛЬНОМ КОДЕ(71) Заявитель Белорусский государственный университет(72) Авторы Авгуль Леонид Болеславович Изотов Сергей Николаевич Петроченко Андрей Сергеевич Супрун Валерий Павлович(73) Патентообладатель Белорусский государственный университет(57) Устройство для сложения чисел в последовательном коде, содержащее три одноразрядных двоичных сумматора и два синхронных двухступенчатых -триггера, входы синхронизации которых соединены со входом синхронизации устройства, а входы обнуления соединены со входом начальной установки устройства, -й информационный вход которого, где 1,2,3, соединен с -м входом первого одноразрядного двоичного сумматора, выход переноса которого соединен с первым входом второго одноразрядного двоичного сумматора, а выход суммы соединен с первым входом третьего одноразрядного двоичного сумматора, выход суммы которого соединен с выходом устройства, отличающееся тем,что содержит одноразрядные двоичные сумматоры с четвертого по седьмой и третий синхронный двухступенчатый -триггер, вход синхронизации которого соединен со входом синхронизации устройства, а вход обнуления соединен со входом начальной установки устройства, (3)-й информационный вход которого соединен с -м входом четвертого 5079 1 одноразрядного двоичного сумматора, седьмой и восьмой информационные входы устройства соединены соответственно с первым и вторым входами пятого одноразрядного двоичного сумматора, третий вход которого соединен с выходом первого синхронного двухступенчатого -триггера, информационный вход которого соединен с выходом суммы шестого одноразрядного двоичного сумматора, первый вход которого соединен с выходом второго синхронного двухступенчатого -триггера, информационный вход которого соединен с выходом суммы седьмого одноразрядного двоичного сумматора, выход переноса которого соединен с информационным входом третьего синхронного двухступенчатого -триггера, выход которого соединен с первым входом седьмого одноразрядного двоичного сумматора, второй вход которого соединен с выходом переноса шестого одноразрядного двоичного сумматора, второй вход которого соединен с выходом переноса третьего одноразрядного двоичного сумматора, а третий вход соединен с выходом суммы второго одноразрядного двоичного сумматора, выход переноса которого соединен с третьим входом седьмого одноразрядного двоичного сумматора, а второй вход соединен с выходом переноса пятого одноразрядного двоичного сумматора, выход суммы которого соединен со вторым входом третьего одноразрядного двоичного сумматора, третий вход которого соединен с выходом суммы четвертого одноразрядного двоичного сумматора,выход переноса которого соединен с третьим входом второго одноразрядного двоичного сумматора.(56)1783516 1, 1992.2043651 1, 1995.2059286 1, 1996.2006915 1, 1994.5548546 , 1996.04128922 , 1992.03108023 , 1991.3216196 1, 1983. Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано для построения быстродействующих арифметических устройств ЭВМ и специализированных процессоров. Известно устройство для сложениячисел в последовательном коде, содержащее дерево одноразрядных двоичных сумматоров и буферный регистр 1. Недостатком устройства является высокая конструктивная сложность. Наиболее близким по конструкции и функциональным возможностям техническим решением к предлагаемому является устройство для сложения четырех чисел в последовательном коде, содержащее три одноразрядных двоичных сумматора и два триггера 2. Недостатком известного устройства являются ограниченные функциональные возможности, так как оно не выполняет сложение более четырех двоичных чисел, представленных в последовательном коде. Изобретение направлено на решение задачи расширения функциональных возможностей устройства для сложения чисел в последовательном коде. Названный технический результат достигается путем введения в состав устройства дополнительно четырех одноразрядных двоичных сумматоров и одного триггера, а также изменением связей между элементами устройства. Устройство для сложения чисел в последовательном коде содержит три одноразрядных двоичных сумматора и два синхронных двухступенчатых -триггера, входы синхронизации которых соединены с входом синхронизации устройства, а входы обнуления соединены с входом начальной установки устройства. В устройстве -й (1,2,3) инфор 2 5079 1 мационный вход соединен с -м входом первого одноразрядного двоичного сумматора,выход переноса которого соединен с первым входом второго одноразрядного двоичного сумматора. Выход суммы первого одноразрядного двоичного сумматора соединен с первым входом третьего одноразрядного двоичного сумматора, выход суммы которого соединен с выходом устройства. В отличие от прототипа устройство содержит одноразрядные двоичные сумматоры с четвертого по седьмой и третий синхронный двухступенчатый -триггер, вход синхронизации которого соединен с входом синхронизации устройства, а вход обнуления соединен с входом начальной установки устройства. В устройстве (3)-й информационный вход соединен с -м входом четвертого одноразрядного двоичного сумматора. Седьмой и восьмой информационные входы устройства соединены соответственно с первым и вторым входами пятого одноразрядного двоичного сумматора, третий вход которого соединен с выходом первого -триггера. Информационный вход первого -триггера соединен с выходом суммы шестого одноразрядного двоичного сумматора, первый вход которого соединен с выходом второго -триггера. Информационный вход второго -триггера соединен с выходом суммы седьмого одноразрядного двоичного сумматора, выход переноса которого соединен с информационным входом третьего -триггера. Выход третьего триггера соединен с первым входом седьмого одноразрядного двоичного сумматора, второй вход которого соединен с выходом переноса шестого одноразрядного двоичного сумматора. Второй вход шестого одноразрядного двоичного сумматора соединен с выходом переноса третьего одноразрядного двоичного сумматора, а третий вход соединен с выходом суммы второго одноразрядного двоичного сумматора. Выход переноса второго одноразрядного двоичного сумматора соединен с третьим входом седьмого одноразрядного двоичного сумматора, второй вход второго одноразрядного двоичного сумматора соединен с выходом переноса пятого одноразрядного двоичного сумматора. Выход суммы пятого одноразрядного двоичного сумматора соединен со вторым входом третьего одноразрядного двоичного сумматора, третий вход которого соединен с выходом суммы четвертого одноразрядного двоичного сумматора. Выход переноса четвертого одноразрядного двоичного сумматора соединен с третьим входом второго одноразрядного двоичного сумматора. На чертеже (фиг. 1) представлена схема устройства для сложения чисел в последовательном коде. Устройство содержит семь одноразрядных двоичных сумматоров (ОДС) 1-7, три синхронных двухступенчатых -триггера 8, 9 и 10, восемь информационных входов 11-18,вход синхронизации 19, вход начальной установки 20 и выход 21. Устройство выполняет сложение восьми -разрядных двоичных чисел 021422-1 х-1,1,8 , представленных в последовательном коде где ,00,1 ,0,2 . Устройство для сложения чисел в последовательном коде работает следующим образом. На вход начальной установки 20 подается импульс, обнуляющий триггеры 8, 9 и 10. На информационные входы 11-18 подаются последовательно во времени одноименные(имеющие одинаковые веса) разряды 0, , , -1 суммируемых чисел Х (0 - младший разряд), сопровождаемые серией изтактовых импульсов, поступающих на вход синхронизации 19 устройства. После этого поступление данных на информационные входы 1118 блокируется, а на вход синхронизации 19 подаются дополнительно три тактовых импульса (разрядность суммывосьми -разрядных чисел равна 3 бита). На выходе 21 устройства последовательно во времени формируются разряды 0, , ,2 суммы , начиная с младшего 0. 3 5079 1 После (3)-го тактового импульса устройство готово к выполнению сложения очередных восьми чисел без предварительного обнуления триггеров 8, 9 и 10. Принцип работы устройства основан на суммировании одноименных (с одинаковыми весами) разрядов восьми чисел с тремя переносами, сформированными на предыдущем такте сложения и хранящимися в триггерах 8, 9 и 10. Семь ОДС 1-7, соединенных, как показано на фиг. 1, образуют одиннадцативходовый сумматор, который в каждом такте выполняет сложение девяти двоичных цифр с весом 20(восемь одноименных разрядов суммируемых чисел и состояние триггера 8), одной двоичной цифры с весом 21 (состояние триггера 9) и одной двоичной цифры с весом 22 (состояние триггера 10). Здесь и далее веса указаны относительно весов очередных разрядов суммируемых чисел. При этом на выходе 21 устройства формируется очередная цифра результата с весом 0 2 , на выходе суммы ОДС 6 - первый перенос с весом 21, на выходе суммы ОДС 7 - второй перенос с весом 22, на выходе переноса ОДС 7 - третий перенос с весом 23. В момент окончания текущего тактового импульса эти переносы заносятся соответственно в триггеры 8, 9 и 10 и на следующем такте суммируются с очередными разрядами восьми чисел,веса которых в два раза больше по сравнению с весами предыдущих разрядов. Математическое описание работы устройства имеет вид 1 (1)62 73 (1)7 , где ,0,2 ,1,8 - значение -го разряда -го числа (очевидно, что 1,2,0) 1, 2, 3 - состояния соответственно триггеров 8, 9 и 10 на -м такте (очевидно, что 1(0)2(0)3(0)0, поскольку триггеры перед началом работы обнулены,и 1(3)2(3)3(3)0)4 значение -го разряда результата, соответствующее сигналу суммы ОДС 4 на -м такте 6 - сигнал суммы ОДС 6 на -м такте 7 - сигнал суммы ОДС 7 на -м такте 7 - сигнал переноса ОДС 7 на -м такте. Работа предлагаемого устройства иллюстрируется временными диаграммами (фиг. 2),которые соответствуют сложению восьми четырехразрядных двоичных чисел 11111,21100, 31011, 41000, Х 51010, Х 60101, Х 71101, 81110,0,3 ,1,8 - значение -го разряда -го числа, который подается на -й информационный вход устройства 1, 1 - соответственно сигналы суммы и переноса ОДС 1 2, 2 - соответственно сигналы суммы и переноса ОДС 2 3, 3 - соответственно сигналы суммы и переноса ОДС 3 4, 4 - соответственно сигналы суммы (этот сигнал является выходным сигналомустройства) и переноса ОДС 4 5, р 5 - соответственно сигналы суммы и переноса ОДС 5 6, р 6 - соответственно сигналы суммы и переноса ОДС 6 7, 7 - соответственно сигналы суммы и переноса ОДС 7 1, 2, 3 - соответственно состояния -триггеров 8, 9 и 10. Достоинствами устройства для сложения чисел в последовательном коде являются широкие функциональные возможности, простая конструкция и отсутствие латентности при формировании результата. 4 Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20.

МПК / Метки

МПК: G06F 7/50

Метки: сложения, чисел, устройство, последовательном, коде

Код ссылки

<a href="https://by.patents.su/5-5079-ustrojjstvo-dlya-slozheniya-chisel-v-posledovatelnom-kode.html" rel="bookmark" title="База патентов Беларуси">Устройство для сложения чисел в последовательном коде</a>

Предыдущий патент: Нагреватель

Следующий патент: Магазин к пистолету для приварки шпилек

Случайный патент: Дренажно-распределительное устройство