Двухканальный цифровой осциллограф

Номер патента: 1063

Опубликовано: 14.03.1996

Авторы: Лисенков Борис Николаевич, Синькевич Валентин Михайлович, Немировский Владимир Моисеевич

Текст

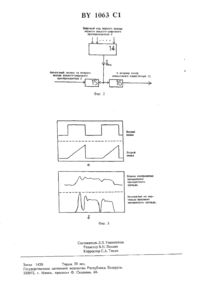

ГОСУДАРСТВЕЕШОЕ ПАТЕНТНОЕ ВЕДОМСТВО РЕСПУБЛИКИ БЕЛАРУСЬ1. Двухканальный цифровой осциллограф,содержащий первый входной блок, вход которого соединен с Цгиной первого исследуемого сигнала, а выход - с входом первого аналогоцифрового преобразователя, первый выход которого подключен к входу первого блока памяти, выход которого соединен с первым входом дисплеии первым входом блока масштабирования, второй входной блок, вход которого подключен к шине второго исследусмою сигнала, второй впалого-цифровой преобразователь, выход которого соединен со входом второго блока памяти, выходкоторого подключен ко второму входу блока масштабирования, блок синхронизации и развертки, вход которого соединен с шиной сигнала синхронизации, первый выход - с тактовыми входами первого аналога-цифровогопреобравователя и первою блока памяти,аналоге -цифрового преобразователя и второго блока памяти, а третий выход - с тактовым входом дисплея, отличающийся тем, что в не то введены аналоговый коммутатор, цифровойкоммутатор, ключ управления в блок вычитания,.1 первьп и второй входы которого соеди ФКЕНЫ С ПЕРВЫМ И ВТОРЫМ ВЫХОДВМИ первогоаналого-цифрового преобразователя соответственно, а выход - с вторым входом аналогового коммутатора, первьпй вход которою подключенк. выходу второго входного блока, а выход - к входу второго аналого-цифрового преобразователя, при этом первый вход ключауправпения соединен с источником питания,второй вход - с общей шиной, а выход - с управляющими входами аналогового-и цифрового коммутаторов, первый вход которого подключен к выходу второго блока памяти,второй вход - к выходу блока масштабирования, а выход подсоединен ко второму входу дисплея.Цель изобретения - позволение точности и расширение функциональных возможностей двухканальною цифровою осциллографа при наблюдении однократного сигнала.На фиг. 1 представлена блок-схема предлагаемого двухканального цифрового осциллографа, которая содержит первый блок 1 входной, второй блок 2 входной, первый аналою-цифровой преобразователь З, второй аналото-цифровой преобразователь 4, первый блок 5 памяти, второй блок 6 памяти, блок 7 синхронизации и развертки, блок 8 масштабирования, дисплей 9, блок 10 вычитания, аналоговый коммутатор 11, цифровой коммутатор 12 кодов и ключ 13 управления.На фиг. 2 изображена блок-схема блока 10 вычитания, которая состоит из цифро-аналоювою преобразователя 14, сумматора 15 аналоговых сигналов и усилителя 16.Вход первою блока 1 входного соедгшен с шиной первою исследуемою сигнала, а выход с входом первою аналоге-цифровою преобразователя 3. Первый выход первого аналоюцифрового преобразователя 1 подключен к первому входу первого блока 5 памяти и блока 10 вычитания. Второй выход первого аналогоцифровою преобразователя 3 соединен с вторым входом блока 10 вычитания. Выход первою блока 5 памяти подключен к первому входу дисплея 9 и первому входу блока 8масштабирования. Вход второю блока 2 вход ного соединен с шиной второю исследуемого сигнала, а выход - с первым входом аналогового коммутатора 11. Выход блока 10 вычитания подключен к второму входу аналогового коммутатора 11. Выход аналоювою коммутатора 11 соединен с входом второго аналоюцифрового преобразователя 4 выход которою подключен к входу второго блока 6 памяти. Выход второю блока 6 памяти соединен с вторым входом блока 8 масштабирования и первым входом цифровою коммутатора 12 кодов. Выход блока 8 масштабирования подключен к второму входу цифровою коммутатора 12 кода, выход которою соединен с вторым входом дисплея 9. Вход блока 7 синхронизации и развертки подключен к шине сигнала синхрони 10зации, а первый выход - к тактовым входам первою аналого-цифровою преобразователя 3 и первою блока 5 памяти. Второй выход блока 7 синхронизации и развертки соединен с так товыми входами второю аналоге-цифровою преобразователя 4 и второю блока 6 памяти. Третий выход блока 7 синхронизации и развертки подключен к тактовому входу дисплея 9. Первый вход ключа 13 управления соединен с источником питания, второй вход - общей шиной, а выход с управляющими входами аналоювого коммутатора 11 и цифровою коммутатора 12 кодов.Цифровой осциллограф работает в двухканальном и одноканалъном режиме (фиг. 1). В двухканальном режиме первый и второй исследуемые сигналы поступают на соответствующие блоки 1 и 2 входные, отображаются дисплеем 9 и верхней и нижней части экрана индикатора. При этом разрешающая способность (динамический диапазон) каждою канала соответствует разрешающей способности области экрана индикатора, предназначенной для данною канала. уПереключение режимов работы с двухканального на одноканальный осуществляется ключом 13 управления. В двухканальном режиме сигнал, поступающий с выхода ключа 13 на управляющие входы коммутаторов 11 и 12, подключается выход блока 2 входного ко входу преобразователя 4, а выход блока 6 памяти - ко второму входу дисплея 9. В одноканальном режиме аналоювый коммутатор 11 отключает блок 2 входной и соединяет вход преобразователя 4 с выходом блока 10 вычитания, а цифровой коммутатор 12 кодов соединяет выход блока 8 масштабирования со вторым входом дисплея 9.В одноканальвом режиме работы цифровою осциллографа входной сигнал поступает на первый блок 1 входной и после преобразования преобразователем З запоминается первым блоком памяти. Одновременно цифро-аналоювый преобразователь 14 (фиг. 2), который входит в состав блока 10 вычитания, преобразует цифровые коды с выхода аналою-цифровою преобразователя 3 в аналоговый сигнал (ток) соответствующего уровня, который поступает на сумматор 15. На другой вход сумматора 15 поступает напряжение со второю выхода преобразователя 3. Поскольку второй выход пре 5 ВУ 1063 С 1 вобразователя 3 является выходом устройства выборки-хранения (в составе преобразователя 3),то на этом выходе в течение времени, которое превышает время задержки между сигналами на первом и втором выходах блока 7, сохраняется постоянное напряжение, соответствующее мгновенному значению ситнала на входе блока 1. Сумматор 15 (фиг. 2) производит алгебраическое суммирование (вычитание) поступающих на него сигналов, после чего результат суммирования усиливается усилителем 16. Коэффициент усиления усилителя 16 равен К 2, где п - количество разрядов аналого-цифрового преобразователя 4 при работе в одноканальном режиме. Количество разрядов п преобразователя 4, используемых при работе в одноканальном режиме,может быть меньше количества разрядов Ы этого же преобразователя при работе в двухканальном режиме (ЦЕМ). В одноканальном режиме преобразователь 4 второго канала обрабатывает разность между мгновенным значением исследуемого сигнала и уровнем,соответствующим цифровому коду этого значения, полученному в первом канале. Эта разность усиливается усилителем 16 до такой степени, чтобы ее максимально возможная величина на входе усилителя 16 (равная младшему разряду преобразователя 3) соответствовала входному диапазону преобразователя 4. При этом выходные коды сравнительно малоразрядных преобразователей 3 и 4 представляют собой соответственно старшие и младшие разряды многоразряднот цифрового кода, который соответствует обрабатываемому МГНОВСННОМУ ЗНЗЧВНИЮ ИССЛВДУВМОГО сигнала. Блок 8 масштабирования служит дли задания оператором масштаба изображения фрагмента исследуемого сигнала в нижней половине экрана матричного индикатора и позволяет оператору выбрать часть разрядов поступающего на его вход многоразрядного цифрового кода и передать эти разряды через коммутатор 12 на второй вход дисплея 9. Количество двоичных разрядов цифрового кода, выбираемых блоком 8 из многоразрядного входного кода,соответствует разрешающей способности той части экрана матричного индикатора (входящего в состав дисплея 9), которая используетсядля отображения сигнала, исследуемого вторым каналом осциллографа в двухканальном режиме работы. Увеличение или уменьшение масштаба изображения фрагмента исследуемого сигнала в одноканальном режиме работы осциллографа в нижней части экрана дисплея достигается с помощью блока 8 масштабироВННИЯ ПУТЕМ сдвига РНЗрЯДПВ МНОГОрЗЭрЯДНОГО входного кода в сторону младших или старших разрядов соответственно. Импульсный сигнал,который тактирует информацию, поступающую на первый и второй входы дисплея 9,подается с третьего вьтхода блока 7 синхрониЗЗЦИИ И развертки на ТЭКТОВЫЙ ВХОД ДИСПЛЕЯ 9 синхронно с импульсными сигналами, тактирующими работу блоков 5 и 6 памяти.В одноканальном режиме работы адаптацию к амплитуде однократного сигнала осуществляют путем предварительной установки аттенюатора первого блока 1 входного в такое положение, чтобы предполагаемый вертикальный размер изображения исследуемого сигнала в этом канале составлял, например, 1-2 больших деления шкалы экрана (1/ 3 1/ 8 размера экрана по вертикали). В этом случае непредВИДВННОВ УВЛИЧБНИС амплитуды ИССЛВДУВМОГО однократного сигнала в 3-8 раз не приведет к потере информации о его амплитуде. При необходимости с помощью блока 8 масштабироВЭНИЯ ИЗОбРЗЖЕНИС ЗВПОМНСЪПЧОГО ОДНОКРВТНОПЭ сигнала может быть увеличено по вертикали до размеров экрана.Если произойдет непредвиденное уменьшеъше амплитуды исследуемого однократного сигнала и полное изображение запомненного сигнала(в верхней части экрана) составит менее одного деления по вертикали, с помощью блока 8 масштабирования устанавливают максимально увеличенный размер изображения.Таким образом, в одноканальном режиме предлагаемый цифровой осциллограф обеспечивает дискретизацию исследуемого сигнала с разрешающей способностью, значительно повышающей разрешающую способность экранаиндикатора. ЭТО ПОЗВОЛЯЕТ СУЩЕСТВЕННО РЕСширить функциональные возможности двухка нального цифрового осциллографа при наблюдении однократного сигнала и повыситьШфровоцч код первого выхода ПЕРВОГО ащлого-цъцарового преобразователя зК- Бювет внеш аналогового имитатора 11Рвшяъштьай по вертикали фрапчгъгг запоях-юного шва-ад.Заказ 1420 Тираж 20 экз. Государственное патентное ведомство Республики Беларусь.

МПК / Метки

МПК: G01R 13/20

Метки: цифровой, осциллограф, двухканальный

Код ссылки

<a href="https://by.patents.su/4-1063-dvuhkanalnyjj-cifrovojj-oscillograf.html" rel="bookmark" title="База патентов Беларуси">Двухканальный цифровой осциллограф</a>

Предыдущий патент: Радиозащитное средство

Следующий патент: Способ коррекции функционального состояния тонкой кишки

Случайный патент: Кокильная машина