Запоминающее устройство

Номер патента: 17482

Опубликовано: 30.08.2013

Авторы: Виткова Марина Федоровна, Булова Юлия Олеговна, Пацей Наталья Владимировна, Шиман Дмитрий Васильевич, Урбанович Павел Павлович, Романенко Дмитрий Михайлович

Текст

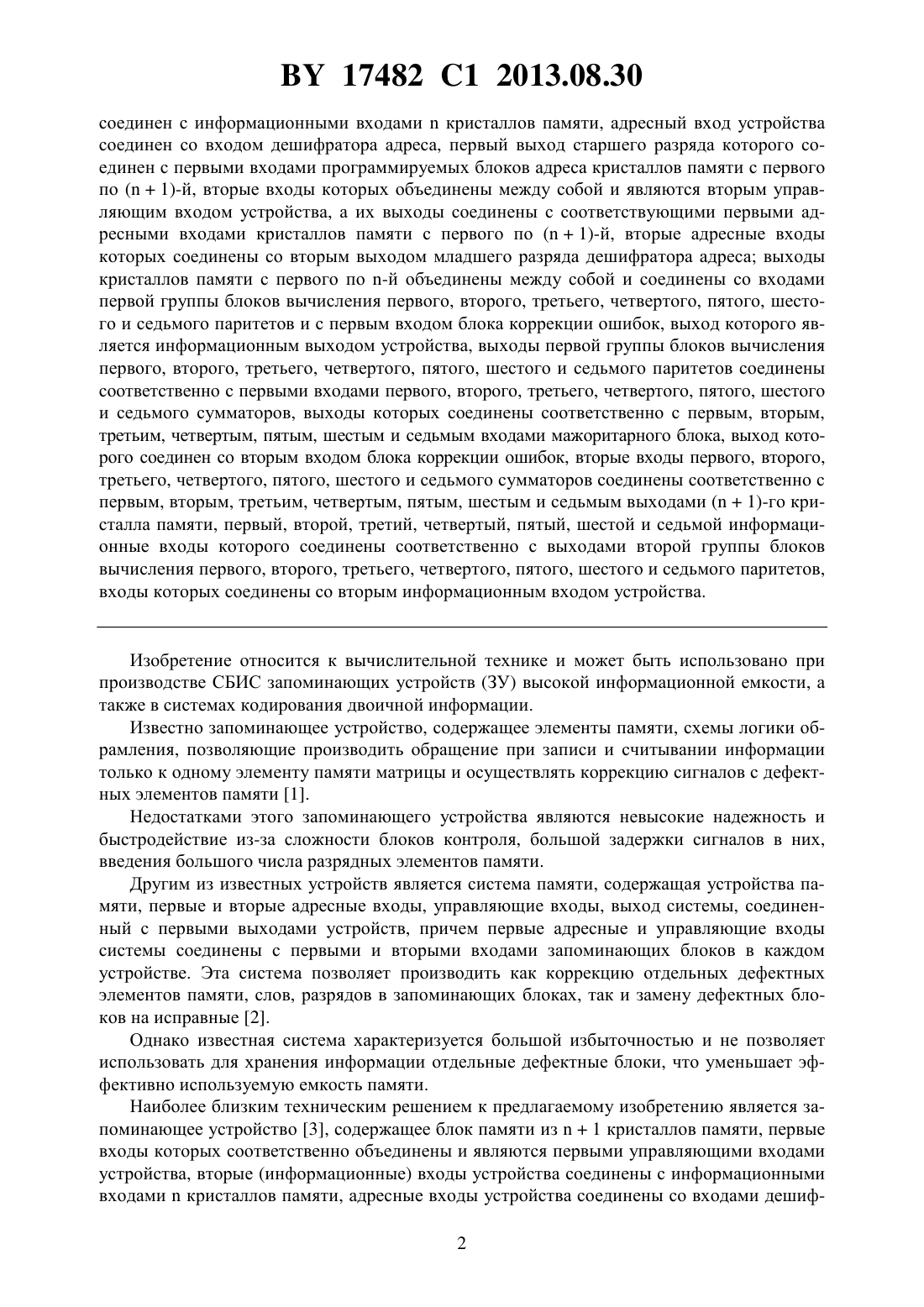

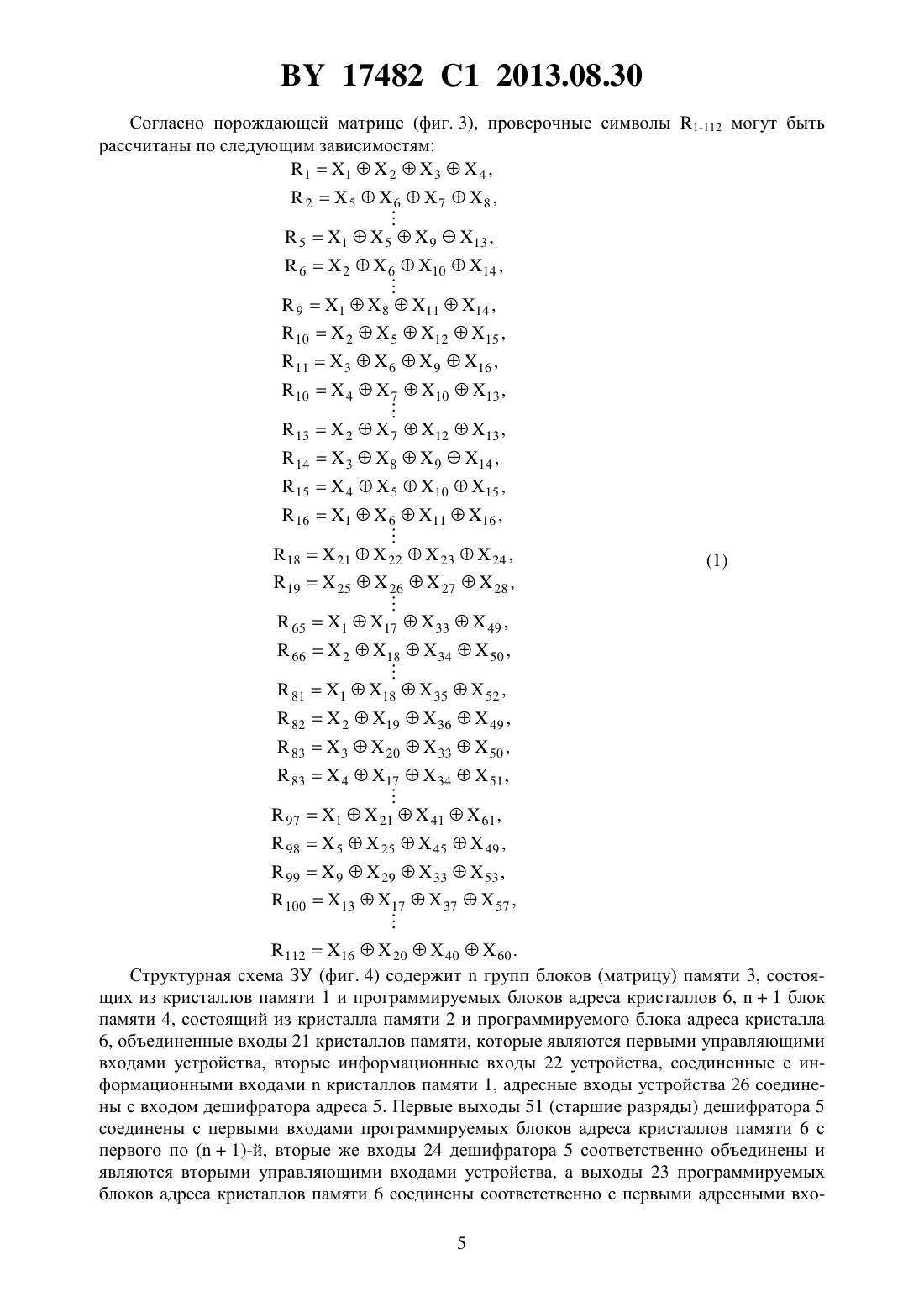

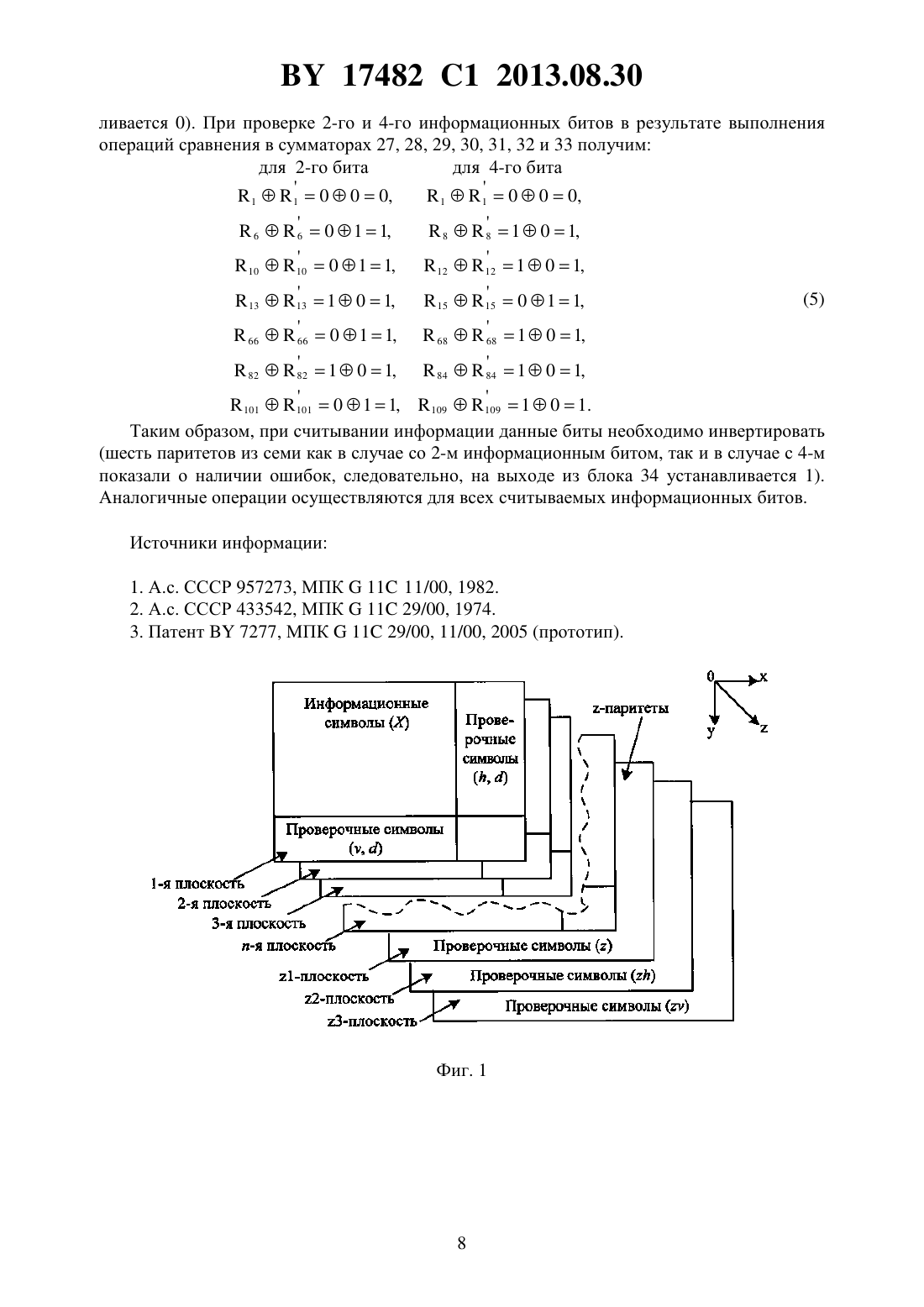

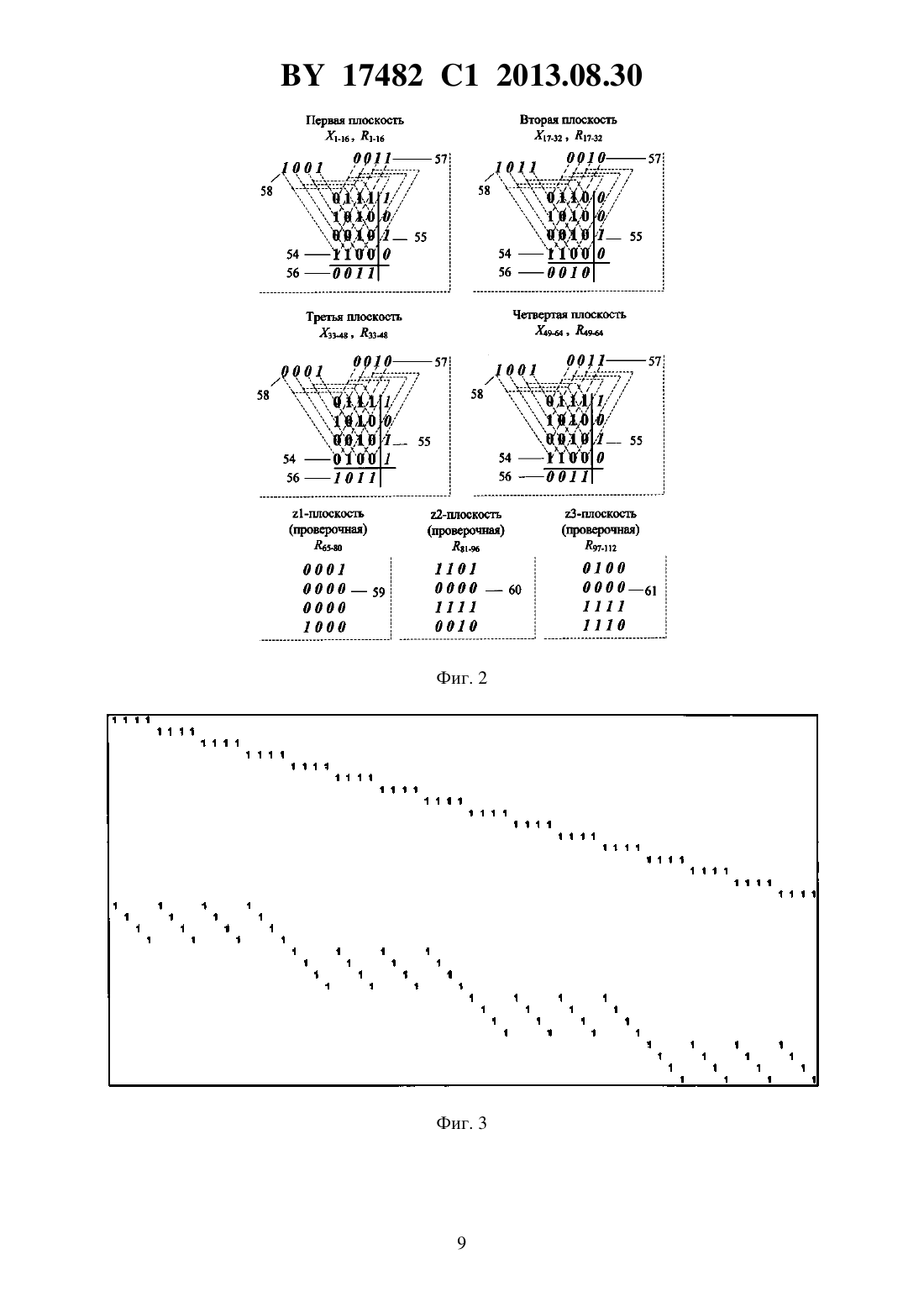

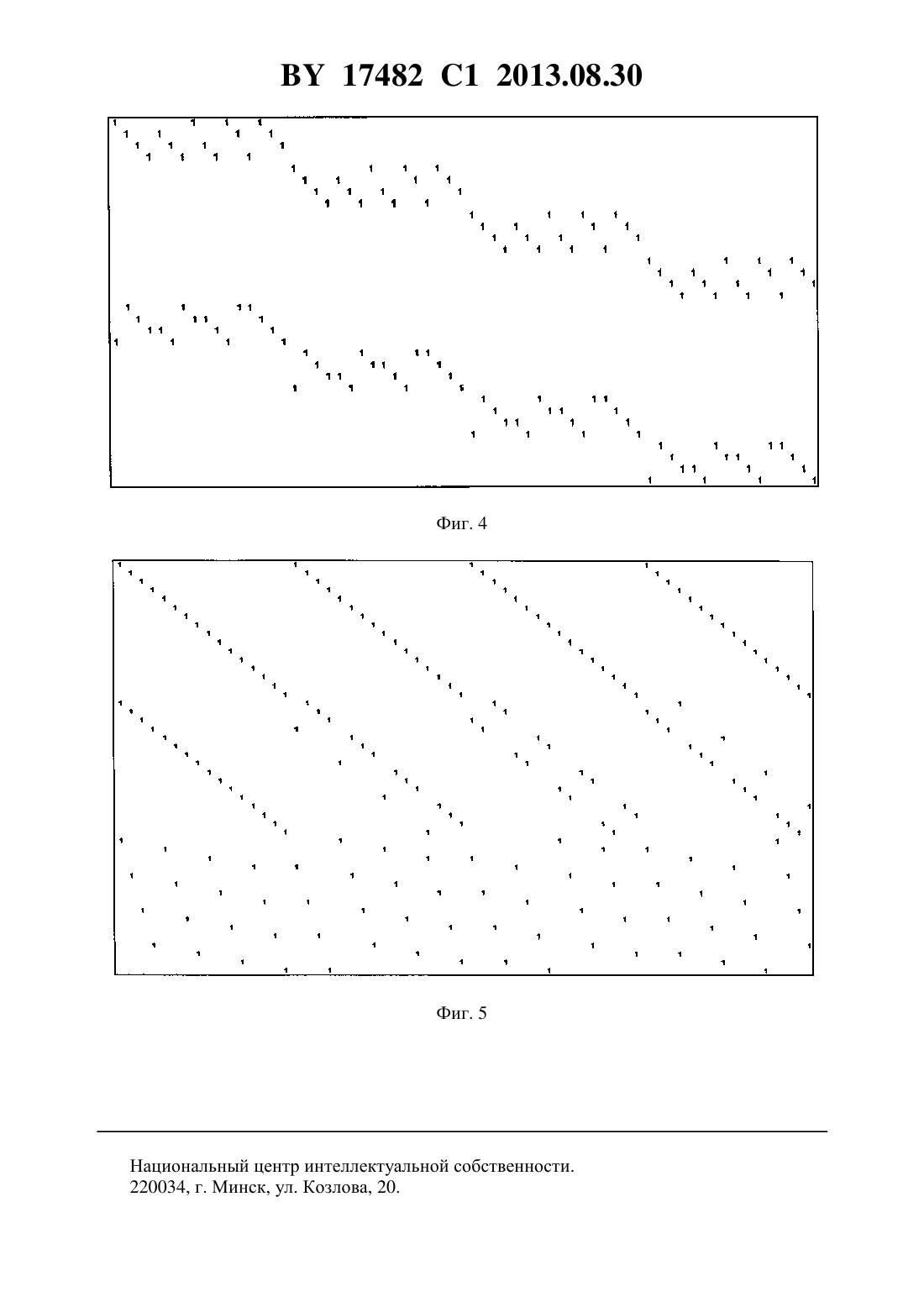

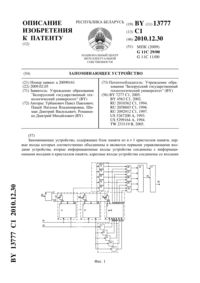

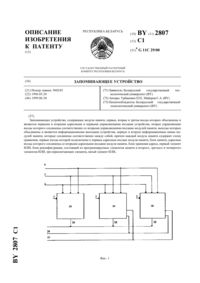

(51) МПК НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ(71) Заявитель Учреждение образования Белорусский государственный технологический университет(72) Авторы Урбанович Павел Павлович Романенко Дмитрий Михайлович Пацей Наталья Владимировна Шиман Дмитрий Васильевич Виткова Марина Федоровна Булова Юлия Олеговна(73) Патентообладатель Учреждение образования Белорусский государственный технологический университет(57) Запоминающее устройство, характеризующееся тем, что содержит 1 блоков памяти из 1 кристаллов памяти, первые входы которых объединены между собой и являются первым управляющим входом устройства, второй информационный вход которого 17482 1 2013.08.30 соединен с информационными входамикристаллов памяти, адресный вход устройства соединен со входом дешифратора адреса, первый выход старшего разряда которого соединен с первыми входами программируемых блоков адреса кристаллов памяти с первого по (1)-й, вторые входы которых объединены между собой и являются вторым управляющим входом устройства, а их выходы соединены с соответствующими первыми адресными входами кристаллов памяти с первого по (1)-й, вторые адресные входы которых соединены со вторым выходом младшего разряда дешифратора адреса выходы кристаллов памяти с первого по -й объединены между собой и соединены со входами первой группы блоков вычисления первого, второго, третьего, четвертого, пятого, шестого и седьмого паритетов и с первым входом блока коррекции ошибок, выход которого является информационным выходом устройства, выходы первой группы блоков вычисления первого, второго, третьего, четвертого, пятого, шестого и седьмого паритетов соединены соответственно с первыми входами первого, второго, третьего, четвертого, пятого, шестого и седьмого сумматоров, выходы которых соединены соответственно с первым, вторым,третьим, четвертым, пятым, шестым и седьмым входами мажоритарного блока, выход которого соединен со вторым входом блока коррекции ошибок, вторые входы первого, второго,третьего, четвертого, пятого, шестого и седьмого сумматоров соединены соответственно с первым, вторым, третьим, четвертым, пятым, шестым и седьмым выходами (1)-го кристалла памяти, первый, второй, третий, четвертый, пятый, шестой и седьмой информационные входы которого соединены соответственно с выходами второй группы блоков вычисления первого, второго, третьего, четвертого, пятого, шестого и седьмого паритетов,входы которых соединены со вторым информационным входом устройства. Изобретение относится к вычислительной технике и может быть использовано при производстве СБИС запоминающих устройств (ЗУ) высокой информационной емкости, а также в системах кодирования двоичной информации. Известно запоминающее устройство, содержащее элементы памяти, схемы логики обрамления, позволяющие производить обращение при записи и считывании информации только к одному элементу памяти матрицы и осуществлять коррекцию сигналов с дефектных элементов памяти 1. Недостатками этого запоминающего устройства являются невысокие надежность и быстродействие из-за сложности блоков контроля, большой задержки сигналов в них,введения большого числа разрядных элементов памяти. Другим из известных устройств является система памяти, содержащая устройства памяти, первые и вторые адресные входы, управляющие входы, выход системы, соединенный с первыми выходами устройств, причем первые адресные и управляющие входы системы соединены с первыми и вторыми входами запоминающих блоков в каждом устройстве. Эта система позволяет производить как коррекцию отдельных дефектных элементов памяти, слов, разрядов в запоминающих блоках, так и замену дефектных блоков на исправные 2. Однако известная система характеризуется большой избыточностью и не позволяет использовать для хранения информации отдельные дефектные блоки, что уменьшает эффективно используемую емкость памяти. Наиболее близким техническим решением к предлагаемому изобретению является запоминающее устройство 3, содержащее блок памяти из 1 кристаллов памяти, первые входы которых соответственно объединены и являются первыми управляющими входами устройства, вторые (информационные) входы устройства соединены с информационными входамикристаллов памяти, адресные входы устройства соединены со входами дешиф 2 17482 1 2013.08.30 ратора адреса, первые выходы (старшие разряды) которого соединены с первыми входами программируемых блоков адреса кристаллов памяти с первого по (1)-й, вторые входы которых соответственно объединены и являются вторыми управляющими входами устройства, выходы программируемых блоков адреса кристаллов памяти соединены соответственно с первыми адресными входами кристаллов памяти, вторые адресные входы которых соединены со вторыми выходами (младшими разрядами) дешифратора адреса,выходы кристаллов памяти с первого по -й соединены со входами первых блоков вычисления первого, второго и третьего паритетов и с первыми входами блока коррекции ошибок, выход которого является информационным выходом устройства, выходы первых блоков вычисления первого, второго и третьего паритетов соединены соответственно с первыми входами первых, вторых и третьих сумматоров, выходы которых соответственно соединены с первыми, вторыми и третьими входами мажоритарного блока, выходы которого соединены со вторыми входами блока коррекции ошибок, вторые входы которых соединены соответственно с первой, второй и третьей группами выходов (1)-го кристалла памяти, первая, вторая и третья группы информационных входов которого соединены соответственно с выходами вторых блоков вычисления первого, второго и третьего паритетов, входы которых соединены со вторыми (информационными) входами устройства. В этом устройстве кристаллы памяти, имеющие дефектные элементы памяти по фиксированным адресам, объединяются между собой таким образом, что появляется возможность использовать частично годные кристаллы, что повышает эффективную емкость ЗУ,а использование горизонтальных и вертикальных проверок записываемых и считываемых символов на основе итеративного кода позволяет повысить надежность ЗУ. Однако при относительно большой длине информационного слова, записываемого вкристаллов памяти (64 и более), цикл записи (а соответственно и цикл считывания информации) заметно возрастает. Это снижает эффективность использования итеративного кода на основе формирования горизонтальных и вертикальных паритетов. Задачей изобретения является повышение надежности запоминающего устройства. Запоминающее устройство, характеризующееся тем, что содержит 1 блоков памяти из 1 кристаллов памяти, первые входы которых объединены между собой и являются первым управляющим входом устройства, второй информационный вход которого соединен с информационными входамикристаллов памяти, адресный вход устройства соединен со входом дешифратора адреса, первый выход старшего разряда которого соединен с первыми входами программируемых блоков адреса кристаллов памяти с первого по (1)-й, вторые входы которых объединены между собой и являются вторым управляющим входом устройства, а их выходы соединены с соответствующими первыми адресными входами кристаллов памяти с первого по (1)-й, вторые адресные входы которых соединены со вторым выходом младшего разряда дешифратора адреса выходы кристаллов памяти с первого по -й объединены между собой и соединены со входами первой группы блоков вычисления первого, второго, третьего, четвертого, пятого, шестого и седьмого паритетов и с первым входом блока коррекции ошибок, выход которого является информационным выходом устройства, выходы первой группы блоков вычисления первого, второго, третьего, четвертого, пятого, шестого и седьмого паритетов соединены соответственно с первыми входами первого, второго, третьего, четвертого, пятого, шестого и седьмого сумматоров, выходы которых соединены соответственно с первым, вторым,третьим, четвертым, пятым, шестым и седьмым входами мажоритарного блока, выход которого соединен со вторым входом блока коррекции ошибок, вторые входы первого, второго,третьего, четвертого, пятого, шестого и седьмого сумматоров соединены соответственно с первым, вторым, третьим, четвертым, пятым, шестым и седьмым выходами (1)-го кристалла памяти, первый, второй, третий, четвертый, пятый, шестой и седьмой информаци 3 17482 1 2013.08.30 онные входы которого соединены соответственно с выходами второй группы блоков вычисления первого, второго, третьего, четвертого, пятого, шестого и седьмого паритетов,входы которых соединены со вторым информационным входом устройства. Изобретение поясняется фиг. 1-6. Фиг. 1 - схема трехмерного итеративного кода с семью линейно-независимыми паритетами (ТИК 7). Фиг. 2 - принцип формирования избыточных символов для трехмерного итеративного кода с семью линейно-независимыми паритетами (64), где 54 - информационные символы (1-64), 55 - горизонтальные паритеты(1-4, 17-20, 33-36, 49-52) (в формуле изобретения - первые паритеты), 56 - вертикальные паритеты(5-8, 21-24, 37-40, 5356) (в формуле изобретения - вторые паритеты), 57 - первые объединенные диагональные паритеты (1) (9-12, 25-28, 41-44, 57-60) (в формуле изобретения - четвертые паритеты), 58- вторые объединенные диагональные паритеты (2) (13-16, 29-32, 45-48, 61-64) (в формуле изобретения - пятые паритеты), 59 - первые паритеты между плоскостями(6580) (в формуле изобретения - третьи паритеты), 60 - вторые паритеты между плоскостями(со сдвигом по горизонтали)(81-96) (в формуле изобретения - шестые паритеты), 61 третьи паритеты между плоскостями (со сдвигом по вертикали)(97-112) (в формуле изобретения - седьмые паритеты). Фиг. 3 - фрагмент порождающей матрицы трехмерного итеративного кода с семью линейно-независимыми паритетами, отображающий принцип формирования горизонтальных и вертикальных паритетов (на фиг. 3 не отображены нули и единичная матрица). Фиг. 4 - фрагмент порождающей матрицы трехмерного итеративного кода с семью линейно-независимыми паритетами, отображающий принцип формирования первых и вторых объединенных диагональных паритетов (на фиг. 4 не отображены нули и единичная матрица). Фиг. 5 - фрагмент порождающей матрицы трехмерного итеративного кода с семью линейно-независимыми паритетами, отображающий принцип формирования первых, вторых и третьих паритетов между плоскостями кода (на фиг.5 не отображены нули и единичная матрица). Фиг. 6 - запоминающее устройство. Сущность метода заключается в том, что система памяти состоит из 1 кристаллов, из которых имеют внутренние схемы дешифрации адреса, а (1)-й кристалл является устройством для хранения паритетов строк и столбцов (, ), первых и вторых объединенных диагональных паритетов (1 и 2), первых, вторых и третьих паритетов между плоскостями (, , ). Из этого следует, что вычисление проверочных символов осуществляется в семи направлениях (, , 1, 2, , , ), т.е. в качестве корректирующего кода используется усовершенствованный трехмерный линейный итеративный код, основанный на свертках по модулю 2, в который добавлены первые и вторые объединенные диагональные проверки, а также вторые и третьи паритеты между плоскостями кода (трехмерный итеративный код с семью линейно-независимыми паритетами). Схематическое представление данного кода, а также принцип формирования проверочных символов при 64 бит представлена на фиг. 1 и 2 соответственно. Минимальное кодовое расстояниетрехмерного линейного итеративного кода с семью линейно-независимыми проверками будет равно 8, следовательно, код позволяет корректировать все ошибки, кратностью не превышающие три. Необходимо также отметить, что с ростом длины информационной последовательности увеличивается скорость кода. Так, при длине 64 скорость 0,36, при 512 скорость кода будет уже равна 0,53, а при 4096 скорость кода достигает 0,7. 4 17482 1 2013.08.30 Согласно порождающей матрице (фиг. 3), проверочные символы 1-112 могут быть рассчитаны по следующим зависимостям 11234 , 25678 ,515913 , 6261014 ,9181114 , 10251215 , 1136916 , 10471013 ,13271213 , 1438914 , 15451015 , 16161116 ,1821222324 , 1925262728 ,651173349 ,662183450 ,811183552 , 822193649 , 833203350 , 834173451 ,971214161 , 985254549 , 999293353 , 10013173757 ,11216204060 . Структурная схема ЗУ (фиг. 4) содержитгрупп блоков (матрицу) памяти 3, состоящих из кристаллов памяти 1 и программируемых блоков адреса кристаллов 6,1 блок памяти 4, состоящий из кристалла памяти 2 и программируемого блока адреса кристалла 6, объединенные входы 21 кристаллов памяти, которые являются первыми управляющими входами устройства, вторые информационные входы 22 устройства, соединенные с информационными входамикристаллов памяти 1, адресные входы устройства 26 соединены с входом дешифратора адреса 5. Первые выходы 51 (старшие разряды) дешифратора 5 соединены с первыми входами программируемых блоков адреса кристаллов памяти 6 с первого по (1)-й, вторые же входы 24 дешифратора 5 соответственно объединены и являются вторыми управляющими входами устройства, а выходы 23 программируемых блоков адреса кристаллов памяти 6 соединены соответственно с первыми адресными вхо 5 17482 1 2013.08.30 дами кристаллов памяти, вторые адресные входы которых соединены со вторыми выходами 52 (младшими разрядами) дешифратора адреса 5. Устройство также содержит первые блоки вычисления горизонтальных 14, вертикальных 15, первых и вторых объединенных диагональных паритетов 16 и 17, первых, вторых и третьих паритетов между плоскостями кода 18, 19 и 20, входы которых соединены с выходами 25 кристаллов памяти с первого по -й выходы первых блоков вычисления горизонтальных 14 и вертикальных 15, первых и вторых диагональных 16 и 17 паритетов, первых, вторых и третьих паритетов между плоскостями кода 18, 19 и 20 соединены соответственно с первыми входами первых, вторых, третьих, четвертых, пятых, шестых и седьмых сумматоров 27, 28, 29, 30, 31, 32 и 33,вторые входы которых соединены соответственно с первыми группами выходов 36, 37, 38,39, 40, 41 и 42 (1)-го кристалла памяти 2, группы информационных входов 43, 44, 45,46, 47, 48, 49 и 50 которого соединены соответственно с выходами вторых блоков вычисления горизонтальных 7, вертикальных 8, первых и вторых объединенных диагональных паритетов 9 и 10, первых, вторых и третьих паритетов между плоскостями кода 11, 12 и 13, входы которых соединены со вторыми информационными входами устройства 22. Кроме того, устройство содержит мажоритарный блок 34, выходы которого соединены со вторыми входами блока коррекции ошибок 35, а входы - с выходами первых 27, вторых 28,третьих 29, четвертых 30, пятых 31, шестых 32 и седьмых 33 сумматоров соответственно. Выход 53 блока коррекции ошибок 35 является информационным выходом устройства. На управляющие входы 21 и 24 подаются стандартные сигналы (разрешение записи/чтения) для соответствующего типа памяти. На адресный вход 26 устройства подаются подадреса опрашиваемого ЭП (соответственно младшие и старшие разряды). В соответствии с кодом адреса на шинах 23 формируется новый (внутренний) адрес, соответствующий адресу годного поднакопителя (часть накопителя) кристаллов 1 и 2 и элементу памяти внутри поднакопителя. Таким образом, программируемый блок 5 позволяет использовать частично годные накопители, что повышает эффективную емкость запоминающего устройства. Устройство работает следующим образом. Режим записи. На шине 21 устанавливается сигнал, разрешающий запись информации в кристаллы памяти 1 и 2. На адресный вход 26 устройства подаются подадреса требуемых элементов памяти. Информационные биты по шине 22 передаются на запись в кристаллы памяти 1, а также во вторые блоки формирования горизонтальных 7, вертикальных 8, первых объединенных диагональных 9, вторых объединенных диагональных 10 паритетов, первых, вторых и третьих паритетов между плоскостями 11, 12 и 13, где осуществляется формирование соответствующих паритетов, которые далее записываются в (1)-й кристалл памяти 2. Режим считывания. На шине 21 устанавливается сигнал, разрешающий считывание информации в кристаллы памяти 1 и 2. На адресный вход 26 устройства подаются подадреса требуемых элементов памяти. Информационные биты, считанные из кристаллов памяти 1, по шине 25 передаются на первый вход блока коррекции ошибок 35, а также в первые блоки формирования горизонтальных 14, вертикальных 15, первых объединенных диагональных 16, вторых объединенных диагональных 17 паритетов, первых, вторых и третьих паритетов между плоскостями 18, 19 и 20, из которых новые паритеты передаются на первые входы соответствующих первых 27, вторых 28, третьих 29, четвертых 30, пятых 31, шестых 32 и седьмых 33 сумматоров. На вторые входы сумматоров 27, 28, 29, 30, 31, 32 и 33 передают считанные по шинам 36, 37, 38, 39, 40, 41 и 42 старые проверочные символы. Результаты суммирования на сумматорах 27, 28, 29, 30, 31, 32 и 33 передаются в мажоритарный блок 34 и далее на вторые входы блока коррекции ошибок 35, где при необходимости осуществляется инверсия соответствующего бита, и далее по шине 53 на выход из устройства. 6 17482 1 2013.08.30 Рассмотрим пример исправления ошибок трехмерным итеративным кодом с семью линейно-независимыми проверками. Пусть закодированы 64 бит (64) информации 0111 1010 0010 1100 0111 1010 0010 1100 0111 1010 0010 1100 0111 1010 0010 1100(информационные биты записываются в кристаллы памяти с 1-го по -й). То есть согласно порождающей матрице (фиг. 3) в блоках 7, 8, 9, 10, 11, 12 и 13 формируются проверочные символы, которые далее записываются в 1 кристалл памяти 141010, 580011, 9120011, 13161001,(2) 65800001000000001000, 81961101000011110010, 971120100000011111110. Пусть при хранении во втором и четвертом битах информационной последовательностивозникла ошибка (инверсия бита). Тогда 0010 1010 0010 1100 0111 1010 0010 1100 0111 1010 0010 1100 0111 1010 0010 1100. Новые проверочные символы, сформированные в блоках 14, 15, 16, 17, 18, 19 и 20, будут равны 1010,1 4 Для декодирования информации реализован мажоритарный принцип (принцип большинства). Например, при проверке 8-го информационного бита в сумматорах 27, 28, 29, 30, 31, 32 и 33 будут сравниватьсяи,и,и,и,и,и,и 2 110 . Иными словами, будут выполнены следующие операции суммирования по модулю 2(1 свидетельствует о том, что ошибка произошла в данном бите, 0 - ошибки нет)000,1 По результатам суммирования согласно мажоритарному принципу в блоке 34 делается вывод, что ошибки в данном информационном бите нет (на выходе из блока 34 устанав 7 17482 1 2013.08.30 ливается 0). При проверке 2-го и 4-го информационных битов в результате выполнения операций сравнения в сумматорах 27, 28, 29, 30, 31, 32 и 33 получим для 2-го бита для 4-го бита 000,000,1 101101011,109109101. Таким образом, при считывании информации данные биты необходимо инвертировать(шесть паритетов из семи как в случае со 2-м информационным битом, так и в случае с 4-м показали о наличии ошибок, следовательно, на выходе из блока 34 устанавливается 1). Аналогичные операции осуществляются для всех считываемых информационных битов. Источники информации Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20.

МПК / Метки

МПК: H03M 13/09, G11C 11/00

Метки: устройство, запоминающее

Код ссылки

<a href="https://by.patents.su/10-17482-zapominayushhee-ustrojjstvo.html" rel="bookmark" title="База патентов Беларуси">Запоминающее устройство</a>

Предыдущий патент: Пьезоэлектрический керамический материал

Следующий патент: Устройство для вычисления полиноминальных симметрических булевых функций девяти переменных

Случайный патент: Сейсмограф