Устройство для сложения шести n-разрядных двоичных чисел в последовательно-параллельном коде

Номер патента: 6530

Опубликовано: 30.09.2004

Авторы: Петроченко Андрей Сергеевич, Супрун Валерий Павлович, Булаш Юрий Леонидович, Авгуль Леонид Болеславович

Текст

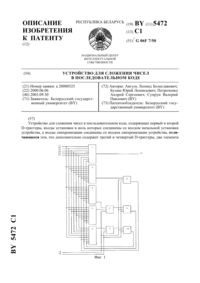

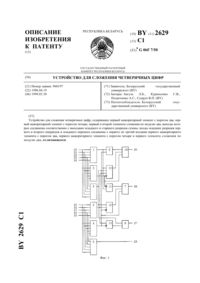

(12) НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ШЕСТИ -РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ В ПОСЛЕДОВАТЕЛЬНО-ПАРАЛЛЕЛЬНОМ КОДЕ(71) Заявитель Белорусский государственный университет(72) Авторы Авгуль Леонид Болеславович Булаш Юрий Леонидович Петроченко Андрей Сергеевич Супрун Валерий Павлович(73) Патентообладатель Белорусский государственный университет(57) Устройство для сложения шести -разрядных двоичных чисел в последовательнопараллельном коде, содержащее три -триггера, входы установки в ноль которых соединены с входом начальной установки устройства, а входы синхронизации соединены с входом синхронизации устройства, отличающееся тем, что содержит четыре элемента сложения по модулю два, три элемента ЗАПРЕТ, семь элементов И, два элемента ИЛИ,два мажоритарных элемента с порогом два, два мажоритарных элемента с порогом четыре 6530 1 и два мажоритарных элемента с порогом шесть, -й (1,6 ) вход первого из которых соединен с -м входом первого мажоритарного элемента с порогом два, -м входом первого мажоритарного элемента с порогом четыре, -м входом первого элемента сложения по модулю два, -м входом первого элемента И и -м входом первой группы информационных входов устройства, -й вход второй группы информационных входов которого соединен с-м входом второго мажоритарного элемента с порогом два, -м входом второго мажоритарного элемента с порогом четыре, -м входом второго мажоритарного элемента с порогом шесть и -м входом второго элемента сложения по модулю два, выход которого соединен с первым выходом устройства, второй выход устройства соединен с выходом третьего элемента сложения по модулю два, первый вход которого соединен с выходом второго мажоритарного элемента с порогом четыре, прямым входом первого элемента ЗАПРЕТ, первым входом второго элемента И и первым входом третьего элемента И, второй вход третьего элемента сложения по модулю два соединен с выходом первого элемента сложения по модулю два, входом запрета первого элемента ЗАПРЕТ, первым прямым входом второго элемента ЗАПРЕТ, первым входом четвертого элемента И, первым входом пятого элемента И, первым входом шестого элемента И и первым входом седьмого элемента И, третий вход третьего элемента сложения по модулю два соединен с выходом третьего элемента ЗАПРЕТ, прямой вход которого соединен выходом второго мажоритарного элемента с порогом два, вторым прямым входом второго элемента ЗАПРЕТ, вторым входом пятого элемента И и вторым входом седьмого элемента И, вход запрета третьего элемента ЗАПРЕТ соединен с выходом второго мажоритарного элемента с порогом шесть, вторым входом четвертого элемента И, вторым входом шестого элемента И и входом запрета второго элемента ЗАПРЕТ, выход которого соединен с первым входом четвертого элемента сложения по модулю два, второй вход которого соединен с выходом первого элемента ЗАПРЕТ, третий вход четвертого элемента сложения по модулю два соединен с выходом первого мажоритарного элемента с порогом два, вторым входом второго элемента И и третьим входом пятого элемента И, четвертый вход четвертого элемента сложения по модулю два соединен с выходом первого мажоритарного элемента с порогом четыре, третьим входом шестого элемента И и первым входом первого элемента ИЛИ, пятый вход четвертого элемента сложения по модулю два соединен с выходом первого мажоритарного элемента с порогом шесть, вторым входом третьего элемента И и третьим входом седьмого элемента И, шестой вход четвертого элемента сложения по модулю два соединен с выходом первого элемента И и первым входом второго элемента ИЛИ, а выход четвертого элемента сложения по модулю два соединен с информационным входом первого триггера, выход которого соединен с седьмым входом второго элемента сложения по модулю два, седьмым входом второго мажоритарного элемента с порогом два, седьмым входом второго мажоритарного элемента с порогом четыре и седьмым входом второго мажоритарного элемента с порогом шесть, выход второго элемента И соединен со вторым входом первого элемента ИЛИ, третий вход которого соединен с выходом четвертого элемента И, четвертый вход первого элемента ИЛИ соединен с выходом пятого элемента И, а выход первого элемента ИЛИ соединен с информационным входом второго -триггера,выход которого соединен с седьмым входом первого элемента сложения по модулю два,седьмым входом первого мажоритарного элемента с порогом два, седьмым входом первого мажоритарного элемента с порогом четыре, седьмым входом первого мажоритарного элемента с порогом шесть и седьмым входом первого элемента И, второй вход второго элемента ИЛИ соединен с выходом третьего элемента И, третий вход соединен с выходом шестого элемента И, четвертый вход соединен с выходом седьмого элемента И, а выход соединен с информационным входом третьего -триггера, выход которого соединен с восьмым входом первого элемента сложения по модулю два, восьмым входом первого мажоритарного элемента с порогом два, восьмым входом первого мажоритарного элемента с порогом четыре, восьмым входом первого мажоритарного элемента с порогом шесть и восьмым входом первого элемента И. 2(56) Белоус А.И. и др. Микропроцессорный комплект БИС серии К 1815 для цифровой обработки сигналов. - М. Радио и связь, 1992. - С. 119.950174 , 1997.960199 , 1997.2047216 1, 1995.1783516 1, 1992.1464155 1, 1989.0656582 1, 1992.5227989 , 1994. Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано для построения быстродействующих арифметических устройств ЭВМ и специализированных процессоров. Известно устройство для сложения четырех двоичных чисел в последовательном коде,содержащее три одноразрядных двоичных сумматора и два триггера 1. Недостатками устройства являются ограниченные функциональные возможности(устройство не выполняет сложение более четырех двоичных чисел) и низкое быстродействие, которое обусловлено представлением суммируемых чисел в последовательном коде. Наиболее близким по конструкции и функциональным возможностям техническим решением к предлагаемому является устройство для сложениядвоичных чисел в последовательно-параллельном коде (числа поступают на входы устройства по два разряда одновременно). Устройство содержит дерево конвейерных двухразрядных сумматоров с запоминанием переноса 2. Недостатком известного устройства является высокая конструктивная сложность. Так,например, при 6 известное устройство содержит пять конвейерных сумматоров, каждый из которых включает в себя два комбинационных двоичных сумматора и пять триггеров. Изобретение направлено на решение задачи упрощения конструкции устройства для сложения чисел в последовательно-параллельном коде. Названный технический результат достигается путем введения в состав устройства элементов сложения по модулю два, мажоритарных элементов, элементов И, элементов ИЛИ, элементов ЗАПРЕТ, а также изменением связей между элементами устройства. Устройство для сложения шести -разрядных двоичных чисел в последовательнопараллельном коде содержит три -триггера, входы установки в ноль которых соединены с входом начальной установки устройства, а входы синхронизации соединены с входом синхронизации устройства. В отличие от прототипа устройство содержит четыре элемента сложения по модулю два, три элемента ЗАПРЕТ, семь элементов И, два элемента ИЛИ, два мажоритарных элемента с порогом два, два мажоритарных элемента с порогом четыре и два мажоритарных элемента с порогом шесть. При этом -й (1, 6 ) вход первого мажоритарного элемента с порогом шесть соединен с -м входом первого мажоритарного элемента с порогом два, -м входом первого мажоритарного элемента с порогом четыре, -м входом первого элемента сложения по модулю два, -м входом первого элемента И и -м входом первой группы информационных входов устройства. В устройстве -й вход второй группы информационных входов соединен с -м входом второго мажоритарного элемента с порогом два, -м входом второго мажоритарного элемента с порогом четыре, -м входом второго мажоритарного элемента с порогом шесть и -м входом второго элемента сложения по модулю два, выход которого соединен с первым выходом устройства. Второй выход устройства соединен с выходом третьего элемента сложения по модулю два, первый вход которого соединен с выходом второго мажоритарного элемента с порогом четыре, прямым входом первого 3 6530 1 элемента ЗАПРЕТ, первым входом второго элемента И и первым входом третьего элемента И. Второй вход третьего элемента сложения по модулю два соединен с выходом первого элемента сложения по модулю два, входом запрета первого элемента ЗАПРЕТ, первым прямым входом второго элемента ЗАПРЕТ, первым входом четвертого элемента И, первым входом пятого элемента И, первым входом шестого элемента И и первым входом седьмого элемента И. Третий вход третьего элемента сложения по модулю два соединен с выходом третьего элемента ЗАПРЕТ. Прямой вход третьего элемента ЗАПРЕТ соединен с выходом второго мажоритарного элемента с порогом два, вторым прямым входом второго элемента ЗАПРЕТ, вторым входом пятого элемента И и вторым входом седьмого элемента И. Вход запрета третьего элемента ЗАПРЕТ соединен с выходом второго мажоритарного элемента с порогом шесть, вторым входом четвертого элемента И, вторым входом шестого элемента И и входом запрета второго элемента ЗАПРЕТ. Выход второго элемента ЗАПРЕТ соединен с первым входом четвертого элемента сложения по модулю два. Второй вход четвертого элемента сложения по модулю два соединен с выходом первого элемента ЗАПРЕТ. Третий вход четвертого элемента сложения по модулю два соединен с выходом первого мажоритарного элемента с порогом два, вторым входом второго элемента И и третьим входом пятого элемента И. Четвертый вход четвертого элемента сложения по модулю два соединен с выходом первого мажоритарного элемента с порогом четыре, третьим входом шестого элемента И и первым входом первого элемента ИЛИ. Пятый вход четвертого элемента сложения по модулю два соединен с выходом первого мажоритарного элемента с порогом шесть, вторым входом третьего элемента И и третьим входом седьмого элемента И. Шестой вход четвертого элемента сложения по модулю два соединен с выходом первого элемента И и первым входом второго элемента ИЛИ. Выход четвертого элемента сложения по модулю два соединен с информационным входом первого -триггера, выход которого соединен с седьмым входом второго элемента сложения по модулю два, седьмым входом второго мажоритарного элемента с порогом два, седьмым входом второго мажоритарного элемента с порогом четыре и седьмым входом второго мажоритарного элемента с порогом шесть. Выход второго элемента И соединен со вторым входом первого элемента ИЛИ, третий вход которого соединен с выходом четвертого элемента И. Четвертый вход первого элемента ИЛИ соединен с выходом пятого элемента И. Выход первого элемента ИЛИ соединен с информационным входом второго -триггера, выход которого соединен с седьмым входом первого элемента сложения по модулю два, седьмым входом первого мажоритарного элемента с порогом два, седьмым входом первого мажоритарного элемента с порогом четыре, седьмым входом первого мажоритарного элемента с порогом шесть и седьмым входом первого элемента И. Второй вход второго элемента ИЛИ соединен с выходом третьего элемента И, третий вход соединен с выходом шестого элемента И,четвертый вход соединен с выходом седьмого элемента И. Выход второго элемента ИЛИ соединен с информационным входом третьего -триггера, выход которого соединен с восьмым входом первого элемента сложения по модулю два, восьмым входом первого мажоритарного элемента с порогом два, восьмым входом первого мажоритарного элемента с порогом четыре, восьмым входом первого мажоритарного элемента с порогом шесть и восьмым входом первого элемента И. На фиг. 1 представлена схема устройства для сложения шести -разрядных двоичных чисел в последовательно-параллельном коде. Устройство содержит четыре элемента сложения по модулю два 1-4, два мажоритарных элемента с порогом два 5 и 6, два мажоритарных элемента с порогом четыре 7 и 8, два мажоритарных элемента с порогом шесть 9 и 10, семь элементов И 11-17, три элемента ЗАПРЕТ 18-20, два элемента ИЛИ 21 и 22, три -триггера 23-25, шесть информационных входов первой группы 26-31, шесть информационных входов второй группы 32-37, вход начальной установки 38, вход синхронизации 39 и два выхода 40 и 41. 4 6530 1 Устройство выполняет сложение шести -разрядных двоичных чиселх 021422-1 х-11,6 , поступающих на его входы в последовательно-параллельном коде по два разряда одновременно (без потери общности полагаем, что- четное) 6( 22 21 ), где 30. Разрядность суммы 0242222 равна 3 бит, и сложение выполняется за /22 тактов. На каждом такте формируются одновременно по два разряда суммы. Принцип работы устройства для сложения шести -разрядных двоичных чисел в последовательно-параллельном коде заключается в потактном сложении двух векторов двоичных переменных (элементы одного вектора имеют веса, равные 20, а элементы второго вектора веса 21) и формировании на каждом такте очередной пары разрядов суммы (один разряд имеет вес, равный 20, а второй разряд - вес 21) и трехразрядного вектора переносов. При этом в каждом такте сложения участвуют шесть пар очередных разрядов операндов (старшие разряды пар поступают на информационные входы первой группы 26-31, младшие - на информационные входы второй группы 32-37) и три одноразрядных переноса, хранящихся в триггерах 23-25 и сформированных на предыдущем такте работы. Элементы 1-22 (фиг. 1) образуют блок сложения , который выполняет сложение семи одноразрядных двоичных чисел с весом 20 (четные разряды шести операндов и младший перенос С 1, задержанный на один такт с помощью триггера 23) и восьми одноразрядных двоичных чисел с весом 21 (нечетные разряды шести операндов и два старших переноса с одинаковыми весами С 2 и С 3 , задержанные на один такт с помощью триггеров 24 и 25). Здесь и далее веса указаны относительно весов очередных пар разрядов суммируемых чисел. Блок сложенияформирует пятиразрядный двоичный код младший разряд текущей пары суммы с весом 20 (выход устройства 41), старший разряд текущей пары суммы с весом 21 (выход устройства 40), младший перенос С 1 с весом 22 (вход триггера 23) и два старших переноса С 2 и С 3 с весами 23 (входы триггеров 24 и 25). Перенос С 1 формируется на выходе элемента сложения по модулю два 4, перенос С 2 на выходе элемента ИЛИ 21, перенос С 3 - на выходе элемента ИЛИ 22. Переносы С 1, С 2 и С 3 задерживаются на один такт с помощью триггеров 23, 24 и 25 соответственно, поскольку при сложении на следующем такте они должны иметь одинаковые веса с очередными парами разрядов операндов. Математическое описание работы устройства для сложения шести -разрядных двоичных чисел в последовательно-параллельном коде имеет вид 1 ( )22,122, 222,322, 422,522, 6 где ,0,1 ,1,6 , - значение -го разряда -го операнда (очевидно, что 1,2,3,0) 1, 2, 3 - значения переносов С 1, С 2 и С 3 соответственно, формируемых на -м такте и записываемых соответственно в триггеры 23, 24 и 25 в момент окончания такта 1, 2, 3 - состояния соответственно триггеров 23, 24 и 25 на -м такте (очевидно, что 1(1)2(1)3(1)0, поскольку триггеры перед началом работы обнулены,и 1(/23)2(/23)3(/23)0, так как 1(/22)2(/22)3(/22)0). 5 6530 1 Работа блока сложенияописывается следующей системой булевых функций 0(2) 6(2)12-2,12-2,22-2,32-2,42-2,52-2,6 8(1), 7(2) - функции, реализуемые мажоритарными элементами с порогами 2,4,6,8, которые определяются следующим образом 1, если 2 ( )3 ( )21,121, 221,321, 421,521, 6 1, если 1 ( )22,122, 222,322, 422,522, 60, если 1 ( )22,122, 222,322, 422,522, 6, Очевидно, что 8 (1) - конъюнкция, реализуемая элементом И 88 (Х 1)232-1,1 х 2-1,22-1,32-1,42-1,52-1,6. 8 Устройство для сложения шести -разрядных двоичных чисел в последовательнопараллельном коде работает следующим образом. На вход начальной установки 38 подается импульс, обнуляющий триггеры 23-25. В сопровождении серии из /2 тактовых импульсов, поступающих на вход синхронизации 39,на информационные входы первой группы 26-31 последовательно подаются /2 векторов нечетных (старших) разрядов (11, 12 16), (31, 32 36) (-1,1, -1,2 -1,6) суммируемых чисел, а на информационные входы второй группы 32-37 - /2 векторов четных(младших) разрядов (01, 02 06), (21, 22 26) (-2,1, -2,2 -2,6) суммируемых чисел. На выходах 40 и 41 устройства также последовательно формируются пары нечетных и четных разрядов суммы (, 0), (3, 2) (-1, -2). После этого подача сигналов на информационные входы 26-37 блокируется, а на вход синхронизации 39 подаются дополнительно два тактовых импульса, которые обеспечивают формирование трех старших разрядов суммы. Первый (из двух дополнительных) импульс формирует пару (, ), а второй - пару (0, 2), так как 30. После прихода (/22)-го тактового импульса устройство готово к сложению очередных чисел без предварительного обнуления триггеров 23-25. Укажем, что нечетные разряды 1, 3 1 формируются на выходе 40 устройства, а четные разряды 0, 2 2 - на выходе 41 устройства. Работа устройства для сложения шести -разрядных двоичных чисел в последовательно-параллельном коде иллюстрируется таблицей (фиг. 2), в которой представлены сигналы на входах и выходах устройства, а также содержимое триггеров 23-25 при сложении шести шестиразрядных двоичных чисел (6) 1100111, 2011110, 3110011, 4111101, 5110110, 6101011 6 6530 1 Достоинствами устройства для сложения шести -разрядных двоичных чисел в последовательно-параллельном коде являются простая конструкция, высокое быстродействие и отсутствие латентности при формировании результата. Источники информации 1.1783516 1. 1992. 2. Белоус А.И. и др. Микропроцессорный комплект БИС серии К 1815 для цифровой обработки сигналов. -М. Радио и связь, 1992. - . 119. Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20.

МПК / Метки

МПК: G06F 7/50

Метки: сложения, чисел, двоичных, шести, последовательно-параллельном, устройство, n-разрядных, коде

Код ссылки

<a href="https://by.patents.su/7-6530-ustrojjstvo-dlya-slozheniya-shesti-n-razryadnyh-dvoichnyh-chisel-v-posledovatelno-parallelnom-kode.html" rel="bookmark" title="База патентов Беларуси">Устройство для сложения шести n-разрядных двоичных чисел в последовательно-параллельном коде</a>

Предыдущий патент: Двигательно-движительный комплекс ВИГ-3

Следующий патент: Способ и аппарат для обработки зерен злаков, обработанные зерна и их применение

Случайный патент: Способ лечения прогностически неблагоприятных вариантов лимфогранулематоза