Устройство для сложения шести n-разрядных двоичных чисел в последовательно-параллельном коде

Номер патента: 5224

Опубликовано: 30.06.2003

Авторы: Авгуль Леонид Болеславович, Булаш Юрий Леонидович, Супрун Валерий Павлович

Текст

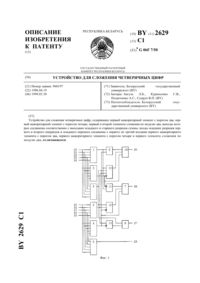

(12) НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ШЕСТИ -РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ В ПОСЛЕДОВАТЕЛЬНО-ПАРАЛЛЕЛЬНОМ КОДЕ(71) Заявитель Белорусский государственный университет(72) Авторы Авгуль Леонид Болеславович Булаш Юрий Леонидович Супрун Валерий Павлович(73) Патентообладатель Белорусский государственный университет(57) 1. Устройство для сложения шестиразрядных двоичных чисел в последовательнопараллельном коде, содержащее три синхронных двухступенчатых -триггера, входы синхронизации которых соединены со входом синхронизации устройства, входы установки в ноль соединены со входом начальной установки устройства, отличающееся тем, что содержит полусумматор, блок суммирования и два семивходовых одноразрядных сумматора, -й (1, 2, , 6) вход первого из которых соединен с -м информационным входом устройства, -й вход второго семивходового одноразрядного сумматора соединен с (6)-м информационным входом устройства, первый выход первого семивходового одноразрядного сумматора соединен с первым выходом устройства, второй выход первого семивходового одноразрядного сумматора соединен с первым входом полусумматора, второй вход которого соединен с первым выходом второго семивходового одноразрядного сумматора, второй выход которого соединен с первым входом блока суммирования, второй и третий входы которого соединены с выходом переноса полусумматора и третьим выходом 5224 1 первого семивходового одноразрядного сумматора соответственно, первый выход блока суммирования соединен с информационным входом первого -триггера, прямой выход которого соединен с четвертым входом блока суммирования, второй выход которого соединен с информационным входом второго -триггера, прямой выход которого соединен с седьмым входом второго семивходового одноразрядного сумматора, третий выход которого соединен с пятым входом блока суммирования, третий выход которого соединен с информационным входом третьего -триггера, прямой выход которого соединен с седьмым входом первого семивходового одноразрядного сумматора, а выход суммы полусумматора соединен с вторым выходом устройства. 2. Устройство по п. 1, отличающееся тем, что блок суммирования содержит мажоритарный элемент с порогом два, два элемента И, элемент ИЛИ и два элемента сложения по модулю два, -й (1, 2, 3, 4) вход первого из которых соединен с -м входом блока суммирования, -м входом мажоритарного элемента с порогом два и -м входом первого элемента И, выход мажоритарного элемента с порогом два соединен с первым входом второго элемента сложения по модулю два, выход первого элемента И соединен с первым входом второго элемента И, первым входом элемента ИЛИ и вторым входом второго элемента сложения по модулю два, третий вход которого соединен с пятым входом блока суммирования и вторым входом второго элемента И, выход которого соединен со вторым входом элемента ИЛИ, выход которого соединен с первым выходом блока суммирования,выходы второго и первого элемента сложения по модулю два соединены со вторым и третьим выходами блока суммирования соответственно.(56) Белоус А.И. и др. Микропроцессорный комплект БИС серии К 1815 для цифровой обработки сигналов. - М. Радио и связь, 1992. - С. 119.950174 , 1997.960199 , 1997.2047216 1, 1995.1783516 1, 1992.1464155 1, 1989.0656582 1, 1995.5227989 , 1994. Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано для построения арифметических устройств ЭВМ и специализированных процессоров. Известно устройство для сложения четырех двоичных чисел в последовательном коде,содержащее три одноразрядных двоичных сумматора и два триггера 1. Недостатками устройства являются низкое быстродействие и ограниченные функциональные возможности, поскольку оно не обеспечивает сложение более четырех операндов. Наиболее близким по функциональным возможностям и конструкции техническим решением к предлагаемому является конвейерное устройство для сложениядвоичных чисел в последовательно-параллельном коде, содержащее при 6 пять конвейерных сумматоров, каждый из которых включает в себя два комбинационных одноразрядных двоичных сумматора и пять триггеров 2. Недостатками известного устройства для сложения двоичных чисел в последовательно-параллельном коде является высокая конструктивная сложность, а также наличие задержки в выдаче результата сложения (латентность), обусловленной конвейерной структурой устройства. 2 5224 1 Изобретение направлено на решение задачи упрощения конструкции устройства для сложения двоичных чисел в последовательно-параллельном коде и устранения латентности. Названный технический результат достигается путем использования новых элементов(многовходовых одноразрядных сумматоров, полусумматора, блока суммирования), а также изменением межсоединений элементов в схеме устройства. Устройство для сложения шести -разрядных двоичных чисел в последовательнопараллельном коде содержит три синхронных двухступенчатых -триггера, входы синхронизации которых соединены с входом синхронизации устройства, входы начальной установки соединены с входом начальной установки устройства. В отличие от прототипа, устройство содержит полусумматор, блок суммирования и два семивходовых одноразрядных сумматора, -й (1,26) вход первого из которых соединен с -м информационным входом устройства, -й вход второго семивходового одноразрядного сумматора соединен с (6)-м информационным входом устройства. Первый выход первого семивходового одноразрядного сумматора соединен с первым выходом устройства. Второй выход первого семивходового одноразрядного сумматора соединен с первым входом полусумматора, второй вход которого соединен с первым выходом второго семивходового одноразрядного сумматора, второй выход которого соединен с первым входом блока суммирования, второй и третий входы которого соединены соответственно с выходом переноса полусумматора и третьим входом первого семивходового одноразрядного сумматора. Первый выход блока суммирования соединен с информационным входом первого -триггера, прямой выход которого соединен с четвертым входом блока суммирования, второй выход которого соединен с информационным входом второго -триггера, прямой выход которого соединен с седьмым входом второго семивходового одноразрядного сумматора, третий выход которого соединен с пятым входом блока суммирования, третий выход которого соединен с информационным входом третьего -триггера, прямой выход которого соединен с седьмым входом первого семивходового одноразрядного сумматора. Выход суммы полусумматора соединен со вторым выходом устройства. При этом блок суммирования содержит мажоритарный элемент с порогом два, два элемента И, элемент ИЛИ и два элемента сложения по модулю два, -й (1,2,3,4) вход первого из которых соединен с -м входом блока сложения, -м входом мажоритарного элемента с порогом два и -м входом первого элемента И. Выход мажоритарного элемента с порогом два соединен с первым входом второго элемента сложения по модулю два. Выход первого элемента И соединен с первым входам второго элемента И, первым входом элемента ИЛИ и вторым входом второго элемента сложения по модулю два,третий вход которого соединен с пятым входом блока суммирования и вторым входом второго элемента И, выход которого соединен со вторым входом элемента ИЛИ, выход которого соединен с первым выходом блока сложения. Выходы второго и первого элементов сложения по модулю два соединены соответственно со вторым и третьим выходами блока сложения. На фиг. 1 представлена схема устройства для сложения шести -разрядных двоичных чисел в последовательно-параллельном коде, на фиг. 2 - схема блока суммирования,входящая в состав устройства. Устройство для сложения шести -разрядных двоичных чисел в последовательнопараллельном коде (фиг. 1) содержит два семивходовых одноразрядных сумматора 1 и 2,полусумматор 3, блок суммирования 4, три синхронных двухступенчатых -триггера 5, 6 и 7, двенадцать информационных входов 8-19, вход синхронизации 20, вход начальной установки 21 и два выхода 22 и 23. Блок суммирования (фиг. 2) содержит два элемента сложения по модулю два 24 и 25,мажоритарный элемент с порогом два 26, два элемента И 27 и 28, элемент ИЛИ 29, пять входов 30-34 и три выхода 35-37. 3 5224 1 Блок суммирования выполняет сложение четырех двоичных цифр с весом 20 и одной двоичной цифры с весом 21 х 2 х 3 х 42 х 542210,где 1, х 2, х 3, х 4 - сигналы, подаваемые на входы блока (в произвольном порядке) с первого по четвертый 30-33 х 5 - сигнал, подаваемый на пятый вход 34 блока 2, 1, 0 - сигналы, формируемые соответственно на первом 35, втором 36 и третьем 37 выходах блока. На фиг. 2 представлен один из возможных вариантов построения блока суммирования,схема которого описывается выражениями 01234 12(1, 2, 3, 4)12345 2123452(1, 2, 3, 4),где М 2(х 1, х 2, х 3, х 4) - функция, реализуемая мажоритарным элементом с порогом два,которая определяется следующим образом 1, если 123422 ( 1 ,2 ,3 ,4 )0, если 12342. Семивходовый одноразрядный сумматор формирует трехразрядный позиционный двоичный код числа единиц, содержащихся во входном семиразрядном двоичном словех 2 х 3 х 4 х 5 х 6742210,где , 2, , 7 - сигналы, подаваемые на входы (в произвольном порядке) семивходового одноразрядного сумматора 2, 1, 0 - сигналы, формируемые на выходах семивходового одноразрядного сумматора. В описании и формуле изобретения и принято, что сигнал 0 формируется на первом,сигнал 1 - на втором и сигнал 2 - на третьем выходах семивходового одноразрядного сумматора. Предлагаемое устройство выполняет сложение шести -разрядных двоичных чисел 02 х 1422-1-1,6 , поступающих на входы устройства в последовательно-параллельном коде по два разряда одновременно 6 где,0,1,0,1,1,6,0,2 . Отметим, что при сложении шести -разрядных двоичных чисел суммабудет иметь длину 3 бит. В дальнейшем (при описании работы устройства) полагаем, что- четное. Еслинечетное, то к суммируемым двоичным числам добавляются по одному тождественно равному нулю старшему разряду. При этом устройство будет выполнять сложение шести где р/2-1,/21, 30. На входы устройства числа Х поступают в последовательно-параллельном коде по два разряда (2 2,) одновременно (начиная с младших разрядов 0, и 1,). Результат 5224 1 сложения также формируется в последовательно-параллельном коде по два разряда (2,2) одновременно за каждый такт сложения (начиная с младших разрядов 0 и 1). Устройство работает следующим образом. На вход начальной установки 21 подается импульс, обнуляющий триггеры 5, 6 и 7. В сопровождении серии из /2 тактовых импульсов, поступающих на вход синхронизации 20, на информационные входы 8-13 последовательно подаются /2 векторов четных разрядов суммируемых чисел (01, 02,06), (21,22,26), , (-2,1, -2,2,-2,6) на информационные входы 14-19 - /2 векторов нечетных разрядов суммируемых чисел (11, 12,16), (31, 32,36), , (-1,1, -1,2,-1,6). При этом на выходах устройства 22 и 23 формируются соответственно четные и нечетные пары разрядов суммы (0, 1), (2, 3), , (-2, -1). После этого подача сигналов на информационные входы 8-19 блокируется, а на вход синхронизации 20 подаются дополнительно два тактовых импульса, которые обеспечивают формирование трех старших разрядов суммы. Первый (из двух дополнительных) импульс формирует пару (, 1), второй - пару (2, 0). После прихода (/22)-го тактового импульса устройство готово к выполнению сложения очередных чисел без предварительного обнуления триггеров. Укажем, что четные разряды (0, 2, , 2) формируются на выходе 22 устройства, а нечетные разряды (1, 3, , 1) - на выходе 23 устройства. Работа устройства иллюстрируется временными диаграммами (фиг. 3), которые соответствуют сложению шести чисел при 6 1111111 2101101 Х 3010010 Х 41011 Х 51111 Х 6111110. Достоинствами устройства являются широкие функциональные возможности, простая конструкция, высокое быстродействие и отсутствие латентности при формировании результата. Источники информации 1. А.с. СССР 1783516, 1992. 2. А.И. Белоус и др. Микропроцессорный комплект БИС серии К 1815 для цифровой обработки сигналов. - М. Радио и связь, 1992. - С. 119. Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20.

МПК / Метки

МПК: G06F 7/50

Метки: чисел, последовательно-параллельном, устройство, шести, коде, n-разрядных, сложения, двоичных

Код ссылки

<a href="https://by.patents.su/6-5224-ustrojjstvo-dlya-slozheniya-shesti-n-razryadnyh-dvoichnyh-chisel-v-posledovatelno-parallelnom-kode.html" rel="bookmark" title="База патентов Беларуси">Устройство для сложения шести n-разрядных двоичных чисел в последовательно-параллельном коде</a>

Предыдущий патент: Способ вакуумной сушки древесины

Следующий патент: Устройство для вычисления фундаментальных симметрических булевых функций

Случайный патент: Электрическая подстанция