Устройство для сложения N чисел в последовательном коде

Номер патента: 4931

Опубликовано: 30.03.2003

Авторы: Супрун Валерий Павлович, Булаш Юрий Леонидович, Авгуль Леонид Болеславович

Текст

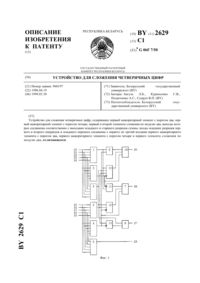

(12) НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯЧИСЕЛ В ПОСЛЕДОВАТЕЛЬНОМ КОДЕ(71) Заявитель Белорусский государственный университет(72) Авторы Авгуль Леонид Болеславович Булаш Юрий Леонидович Супрун Валерий Павлович(73) Патентообладатель Белорусский государственный университет(57) Устройство для сложениячисел в последовательном коде, содержащее многовходовый одноразрядный сумматор, -й вход которого, где 1, 2 соединен с -м информационным входом устройства, выход которого соединен с первым выходом многовходового одноразрядного сумматора, отличающееся тем, что содержит р сдвигающих регистров, каждый из которых имеет разрядность , причем р 2, гдер, а 1, 2,р, при этом -й выход -го сдвигающего регистра соединен с -м входом многовходового одноразрядного сумматора, (1)-й - выход которого соединен со входом -го сдвигающего регистра, входы синхронизации и установки в ноль которых соединены соответственно с входами синхронизации и начальной установки устройства.(56)2047216 1, 1995.2043651 1, 1995.2059286 1, 1996.2006915 1, 1994.4229802 , 1980.5548546 , 1996.04128922 , 1992.3216196 1, 1983. Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано для построения арифметических устройств ЭВМ и специализированных процессоров. Известно устройство для сложения четырех двоичных чисел в последовательном коде,содержащее три одноразрядных двоичных сумматора и два триггера 1. Недостатком устройства являются ограниченные функциональные возможности, поскольку оно не обеспечивает одновременное сложение более четырех операндов. Наиболее близким по функциональным возможностям и конструкции техническим решением к предлагаемому является устройство для сложенияодноразрядных двоичных чисел (многовходовый одноразрядный сумматор), содержащее два элемента сложения по модулю два и /2 мажоритарных элементов 2. Недостатком известного устройства являются ограниченные функциональные возможности, поскольку оно не обеспечивает сложение-разрядных двоичных чисел. Изобретение направлено на решение задачи расширения функциональных возможностей устройства для сложения чисел в последовательном коде. Названный технический результат достигается путем использования новых элементов(сдвигающих регистров), а также изменением межсоединений элементов в схеме устройства. Устройство для сложениячисел в последовательном коде содержит многовходовый одноразрядный сумматор, -й вход которого, где 1, 2 , соединен с -м информационным входом устройства, выход которого соединен с первым выходом многовходового одноразрядного сумматора. В отличие от прототипа, в устройство дополнительно введены р сдвигающих регистров, каждый из которых имеет разрядность , причем 2, гдер, а 1,2 р. При этом -й выход -го сдвигающего регистра соединен с -м входом многовходового одноразрядного сумматора, (1)-й выход которого соединен с входом -го сдвигающего регистра. Входы синхронизации и установки в ноль сдвигающих регистров соединены соответственно с входами синхронизации и начальной установки устройства. На фиг. 1 представлена схема устройства для сложениячисел в последовательном коде. Устройство содержит многовходовый одноразрядный сумматор 1, р сдвигающих регистров 21-2 р,информационных входов 31-3, вход синхронизации 4, вход начальной установки 5 и один выход 6. Принцип работы устройства для сложениячисел в последовательном коде основан на использовании многовходового одноразрядного сумматора 1 для одновременного сложения одноименных разрядов операндов и кортежа переносов (задержанных на соответствующее число тактов), которые хранятся в р сдвигающих регистрах 21-2 р. Эти регистры представляют собой регистровый файл типа . При этом -й (1, 2 р) сдвигающий регистр имеет разрядность, равную . 4931 1 Многовходовый одноразрядный сумматор 1 формирует (р 1)-разрядный позиционный двоичный код числа единиц, содержащихся во входном -разрядном двоичном слове(величинаопределяется из соотношения, где р 2) 1222-1-1210,где 1, 2, ,- сигналы одноименных разрядовоперандов, подаваемые на входы 31-3 многовходового одноразрядного сумматора 1 (эти входы одновременно являются информационными входами устройства) 1, 2- сигналы переносов, подаваемые на входы многовходового одноразрядного сумматора 1 с выходов сдвигающих регистров 21-2 р 0, 1, ,- сигналы, формируемые на выходах многовходового одноразрядного сумматора 1. В формуле изобретения принято, что сигнал суммы 0 формируется на первом, а сигналы переносов 1, 2, ,- на выходах многовходового одноразрядного сумматора 1 со второго по (1)-й соответственно. Предлагаемое устройство выполняет сложение-разрядных двоичных чиселх 0214 х 22-1-11,, представленных в последовательном коде 2, где ,00,1 ,1,,0,1 ,2. Устройство для сложениячисел в последовательном коде работает следующим образом. На вход начальной установки 5 подается импульс, обнуляющий регистры 21-2,служащие для приема, хранения и выдачи сигналов переносов на определенных тактах работы. На информационные входы 31-3 подаются последовательно во времени разряды 0, х 1 х-1, всех суммируемых чисел Х, начиная с младших разрядов 0. При этом каждая группа разрядов сопровождается серией изтактовых импульсов, поступающих на вход синхронизации 4 устройства. После этого поступление данных на информационные входы 31-3 блокируется, а на вход синхронизации 4 дополнительно подаются(2) тактовых импульса (разрядность результатапри сложении-разрядных чисел равнабита), по заднему фронту которых осуществляется синхронный сдвиг информации в регистрах 21-2. На выходе 6 устройства последовательно во времени формируются разряды 0, 1-1 суммы , начиная с младшего 0. После -го тактового импульса устройство готово к выполнению сложения очередных чисел без предварительного обнуления триггеров. Таким образом, устройство обеспечивает сложение-разрядных двоичных чисел,подаваемых младшими разрядами вперед, затактов работы. На фиг. 2 представлена схема устройства при 8 и 4. На фиг. 2 показаны сдвигающие регистры 71-78 и 8, которые не входят в состав заявляемого устройства и предназначены соответственно для хранения восьми входных операндов Х 1-Х 8 и результата сложения . Разрядность регистров 71-78 равна 4 бит, а регистра 8 -7 бит. Работа устройства (фиг. 2) поясняется таблицей (фиг. 3), в которой показано содержимое его регистров на всех тактах работы при сложении восьми четырехразрядных чисел(8,4,11, р 3,3) 11011, Х 20101, 31101, Х 41010,51111, 60111, 71100, 81001. Через 7 тактов работы в регистре 8 будет записано число 1010010, представляющее собой сумму 2810110101110110101111011111001001. 3 4931 1 В таблице (фиг. 3) нулевой такт соответствует исходному состоянию, а символом х обозначено безразличное состояние. Заметим, что информация из регистров 71-78 необходима лишь в течение первых четырех тактов. Поэтому к моменту окончания четвертого тактового импульса эти регистры должны либо быть обнулены (чтобы не влиять на работу сумматора 1 на последующих тактах), либо поступление информации с выходов этих регистров должно быть заблокировано. Достоинствами устройства являются широкие функциональные возможности, простая конструкция, высокое быстродействие и отсутствие задержки в выдаче результата сложения (латентности). Источники информации 1. А.с. СССР 1783516, 1992. 2.20472164, 1995. Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20. 5

МПК / Метки

МПК: G06F 7/50

Метки: чисел, последовательном, устройство, сложения, коде

Код ссылки

<a href="https://by.patents.su/5-4931-ustrojjstvo-dlya-slozheniya-n-chisel-v-posledovatelnom-kode.html" rel="bookmark" title="База патентов Беларуси">Устройство для сложения N чисел в последовательном коде</a>

Предыдущий патент: Отражатель для спицевого колеса транспортного средства

Следующий патент: Стенд для диагностирования электродвигателей

Случайный патент: Генератор маскирующих сигналов