Сумматор унитарных кодов по модулю семь

Номер патента: 16091

Опубликовано: 30.06.2012

Авторы: ГОРОДЕЦКИЙ Данила Андреевич, Супрун Валерий Павлович

Текст

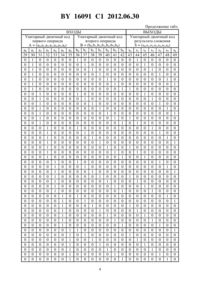

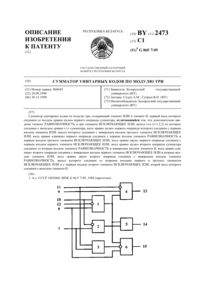

(51) МПК НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ СУММАТОР УНИТАРНЫХ КОДОВ ПО МОДУЛЮ СЕМЬ(71) Заявитель Белорусский государственный университет(72) Авторы Супрун Валерий Павлович Городецкий Данила Андреевич(73) Патентообладатель Белорусский государственный университет(57) Сумматор унитарных кодов по модулю семь, содержащий семь элементов И, выход го, где 1,27, из которых соединен с выходом сумматора равно- 1 результата суммы, отличающийся тем, что содержит двадцать один элемент ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, выход (3- 3)-го из которых, где 1,2,3, соединен с -м входом го элемента И, вход сумматора равно нулю -го операнда, где 1,2, соединен с -м входом четвертого, седьмого, десятого, тринадцатого, шестнадцатого и девятнадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, вход сумматора равно единице -го операнда соединен с -м входом первого, одиннадцатого, четырнадцатого, семнадцатого и двадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с -м инверсным входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, вход сумматора равно двум -го операнда соединен с -м входом второго, пятого, восемнадцатого и двадцать 16091 1 2012.06.30 первого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с -м инверсным входом седьмого и одиннадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, вход сумматора равно трем -го операнда соединен с -м входом третьего, шестого и восьмого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с -м инверсным входом десятого,четырнадцатого и восемнадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два,вход сумматора равно четырем -го операнда соединен с -м входом девятого и двенадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с -м инверсным входом третьего, тринадцатого, семнадцатого и двадцать первого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, вход сумматора равно пяти -го операнда соединен с -м входом пятнадцатого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с -м инверсным входом второго, шестого, девятого, шестнадцатого и двадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, вход сумматора равно шести -го операнда соединен с -м инверсным входом первого, пятого, восьмого, двенадцатого, пятнадцатого и девятнадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два. Изобретение относится к области вычислительной техники и может быть использовано для построения цифровых устройств, реализующих вычислительные операции модулярной арифметики. Известен -операндный сумматор унитарных кодов по модулю , который при 2 и 7 содержит сорок девять элементов И, семь элементов ИЛИ, четырнадцать входов и семь выходов 1. Сложность сумматора равна 147, а быстродействие составляет 2, гдезадержка на логический элемент. Известный сумматор, как и заявляемый сумматор унитарных кодов по модулю семь,содержит семь элементов И. Недостатком известного сумматора является высокая конструктивная сложность. Наиболее близким по функциональным возможностям и конструкции техническим решением к предлагаемому сумматору является сумматор унитарных кодов по модулю семь, который содержит семь элементов ИЛИ, двадцать один элемент РАВНОЗНАЧНОСТЬ, семь элементов И, четырнадцать входов и семь выходов 2. Сложность сумматора (по числу входов логических элементов) равна 77, а быстродействие, определяемое глубиной схемы, составляет 3, где- задержка на логический элемент. Сумматор-прототип, как и предлагаемый сумматор, содержит семь элементов И, выход -го из которых, где 1,27, соединен с выходом сумматора равно -1 результата сложения по модулю семь. Недостатком сумматора-прототипа является низкое быстродействие. Изобретение направлено на повышение быстродействия (уменьшение глубины логической схемы) сумматора-прототипа. Сумматор унитарных кодов содержит семь элементов И, выход -го из которых, где 1,27, соединен с выходом сумматора равно -1 результата сложения. В отличие от прототипа сумматор содержит двадцать один элемент ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, выход (3-3)-го из которых, где 1,2,3, соединен с -м входом -го элемента И. Вход сумматора равно нулю -го операнда, где 1,2, соединен с -м входом четвертого, седьмого, десятого, тринадцатого, шестнадцатого и девятнадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два. Вход сумматора равно единице -го операнда соединен с -м входом первого, одиннадцатого, четырнадцатого, семнадцатого и двадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с -м инверсным входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два. Вход сумматора равно двум -го операнда соединен с -м входом второго, пятого,восемнадцатого и двадцать первого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с 2-м инверсным входом седьмого и одиннадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два. Вход сумматора равно трем -го операнда соединен с -м входом третьего, шестого и восьмого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с -м инверсным входом десятого, четырнадцатого и восемнадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два. Вход сумматора равно четырем -го операнда соединен с -м входом девятого и двенадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с -м инверсным входом третьего, тринадцатого, семнадцатого и двадцать первого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два. Вход сумматора равно пяти -го операнда соединен с -м входом пятнадцатого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с -м инверсным входом второго, шестого,девятого, шестнадцатого и двадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два. Вход сумматора равно шести -го операнда соединен с -м инверсным входом первого, пятого, восьмого, двенадцатого, пятнадцатого и девятнадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два. Основной технический результат изобретения заключается в повышении быстродействия сумматора-прототипа. Названный эффект достигается путем введения в логическую схему сумматора новых элементов (элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два) с последующим изменением соединений между элементами логической схемы. На фиг. 1 представлена схема сумматора унитарных кодов по модулю семь. Сумматор содержит двадцать один элемент ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два 1,221, семь элементов И 22, 2328, четырнадцать входов 29,3042 и семь выходов 43,4449. Сумматор унитарных кодов по модулю семь работает следующим образом. На входы 29,3035 сумматора поступают значения разрядов унитарного двоичного кода первого операнда(0,1,2,3,4,5,6), на входы 36,3742 сумматора - значения разрядов унитарного двоичного кода второго операнда(0,1,2,3,4,5,6), где 0,1,2,3,4,5,6, 0,1,2,3,4,5,60, 1. При этом 1 и 1 тогда и только тогда,когда( 7) и( 7), где 0,1,26. На выходах 43,4449 сумматора формируется унитарный двоичный код результата выполнения операции сложения( 7), где(0,1,2,3,4,5,6) и 0,1,2,3,4,5,60, 1. Здесь 1 тогда и только тогда, когда( 7) и 0,1,26. Логические функции 0,1,2,3,4,5,6, реализуемые на выходах сумматора унитарных кодов по модулю семь, представлены посредством таблицы истинности. ВХОДЫ ВЫХОДЫ Унитарный двоичный код Унитарный двоичный код Унитарный двоичный код первого операнда второго операнда результата сложения(0,1,2,3,4,5,6)(0,1,2,3,4,5,6)(0,1,2,3,4,5,6) 0 1 2 3 4 5 6 0 1 2 3 4 5 6 0 1 2 3 4 5 6 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 3 16091 1 2012.06.30 Продолжение табл. ВХОДЫ ВЫХОДЫ Унитарный двоичный код Унитарный двоичный код Унитарный двоичный код первого операнда второго операнда результата сложения(0,1,2,3,4,5,6)(0,1,2,3,4,5,6)(0,1,2,3,4,5,6) 0 1 2 3 4 5 6 0 1 2 3 4 5 6 0 1 2 3 4 5 6 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 0 1 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 1 0 4 16091 1 2012.06.30 Логическая схема заявляемого сумматора синтезирована на основе применения следующих аналитических представлений логических функций 0,1,2,3,4,5,6, зависящих от переменных 0,16,0,16 1, если 11662, 1, если 22552,01, если 33442,0 в противном случае, 1, если 00112, 1, если 22662,11, если 33552,0 в противном случае, 1, если 00222, 1, если 33662,21, если 44552,0 в противном случае, 1, если 00332, 1, если 11222,31, если 44662,0 в противном случае, 1, если 00442, 1, если 11332,41, если 55662,0 в противном случае,Основным достоинством заявляемого сумматора унитарных кодов по модулю семь является высокое быстродействие, определяемое глубиной схемы и равное 2, где- задержка на логический элемент (быстродействие сумматора-прототипа составляет 3). 5 Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20.

МПК / Метки

Метки: унитарных, семь, кодов, модулю, сумматор

Код ссылки

<a href="https://by.patents.su/6-16091-summator-unitarnyh-kodov-po-modulyu-sem.html" rel="bookmark" title="База патентов Беларуси">Сумматор унитарных кодов по модулю семь</a>

Предыдущий патент: Керамический пигмент сиреневого цвета

Следующий патент: Состав для ограничения притока пластовых вод и способ его получения

Случайный патент: Лазерно-плазменный двигатель