Сумматор унитарных кодов по модулю семь

Номер патента: 3704

Опубликовано: 30.12.2000

Текст

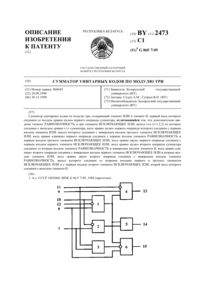

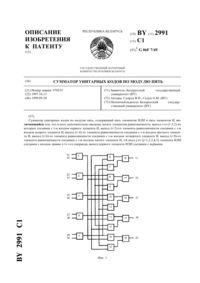

ГОСУДАРСТВЕННЫЙ ПАТЕНТНЫЙ КОМИТЕТ РЕСПУБЛИКИ БЕЛАРУСЬ СУММАТОР УНИТАРНЫХ КОДОВ ПО МОДУЛЮ СЕМЬ(71) Заявители Белорусский государственный университет, Белорусский государственный экономический университет(73) Патентообладатели Белорусский государственный университет, Белорусский государственный экономический университет(57) Сумматор унитарных кодов по модулю семь, содержащий семь элементов ИЛИ и семь элементов И, отличающийся тем, что в него дополнительно введены двадцать один элемент РАВНОЗНАЧНОСТЬ, -й(1, 2) вход -го (1, 2 7) элемента ИЛИ соединен с входом равно -1 -го операнда, выход -го элемента И соединен с выходом равно -1 сумматора, а -й (1, 2, 3) вход соединен с выходом (3- 3)-го элемента РАВНОЗНАЧНОСТЬ, выход первого элемента ИЛИ соединен с первыми входами четвертого,седьмого, десятого, тринадцатого, шестнадцатого и девятнадцатого элементов РАВНОЗНАЧНОСТЬ, выход второго элемента ИЛИ соединен с первыми входами первого, одиннадцатого, четырнадцатого, семнадцатого и двадцатого элементов РАВНОЗНАЧНОСТЬ и со вторым входом четвертого элемента РАВНОЗНАЧНОСТЬ, выход третьего элемента ИЛИ соединен с первыми входами второго,3704 1 пятого, восемнадцатого и двадцать первого элементов РАВНОЗНАЧНОСТЬ и со вторыми входами седьмого и одиннадцатого элементов РАВНОЗНАЧНОСТЬ, выход четвертого элемента ИЛИ соединен с первыми входами третьего, шестого и восьмого элементов РАВНОЗНАЧНОСТЬ и со вторыми входами десятого,четырнадцатого и восемнадцатого элементов РАВНОЗНАЧНОСТЬ, выход пятого элемента ИЛИ соединен с первыми входами девятого и двенадцатого элементов РАВНОЗНАЧНОСТЬ и со вторыми входами третьего,тринадцатого, семнадцатого и двадцать первого элементов РАВНОЗНАЧНОСТЬ, выход шестого элемента ИЛИ соединен с первым входом пятнадцатого элемента РАВНОЗНАЧНОСТЬ и со вторыми входами второго, шестого, девятого, шестнадцатого и двадцатого элементов РАВНОЗНАЧНОСТЬ, выход седьмого элемента ИЛИ соединен со вторыми входами первого, пятого, восьмого, двенадцатого, пятнадцатого и девятнадцатого элементов РАВНОЗНАЧНОСТЬ. Изобретение относится к области вычислительной техники и микроэлектроники и может быть использовано для построения средств аппаратурного контроля и цифровых устройств, работающих в системе остаточных классов. Наиболее близким по функциональным возможностям и конструкции техническим решением к предлагаемому является сумматорунитарных кодов по модулю , который при 7 и 2 содержит сорок девять элементов И и семь элементов ИЛИ 1. Сложность сумматора равна 147, а быстродействие - 2, гдезадержка на логический элемент. Недостатком известного сумматора является высокая конструктивная сложность. Изобретение направлено на решение технической задачи понижения конструктивной сложности сумматора унитарных кодов по модулю семь. Сумматор унитарных кодов по модулю семь, содержащий семь элементов ИЛИ и семь элементов И. В отличие от прототипа, в него дополнительно введены двадцать один элемент РАВНОЗНАЧНОСТЬ, -й (1,2) вход -го (1, 27) элемента ИЛИ соединен с входом равно -1 -го операнда, выход -го элемента И соединен с выходом равно -1 сумматора, а -й (1, 2, 3) вход соединен с выходом (3-3)-го элемента РАВНОЗНАЧНОСТЬ. Выход первого элемента ИЛИ соединен с первыми входами четвертого, седьмого, десятого, тринадцатого, шестнадцатого и девятнадцатого элементов РАВНОЗНАЧНОСТЬ. Выход второго элемента ИЛИ соединен с первыми входами первого, одиннадцатого, четырнадцатого, семнадцатого и двадцатого элементов РАВНОЗНАЧНОСТЬ и со вторым входом четвертого элемента РАВНОЗНАЧНОСТЬ. Выход третьего элемента ИЛИ соединен с первыми входами второго, пятого, восемнадцатого и двадцать первого элементов РАВНОЗНАЧНОСТЬ и со вторыми входами седьмого и одиннадцатого элементов РАВНОЗНАЧНОСТЬ. Выход четвертого элемента ИЛИ соединен с первыми входами третьего, шестого и восьмого элементов РАВНОЗНАЧНОСТЬ и со вторыми входами десятого, четырнадцатого и восемнадцатого элементов РАВНОЗНАЧНОСТЬ. Выход пятого элемента ИЛИ соединен с первыми входами девятого и двенадцатого элементов РАВНОЗНАЧНОСТЬ и со вторыми входами третьего, тринадцатого, семнадцатого и двадцать первого элементов РАВНОЗНАЧНОСТЬ. Выход шестого элемента ИЛИ соединен с первым входом пятнадцатого элемента РАВНОЗНАЧНОСТЬ и со вторыми входами второго, шестого, девятого, шестнадцатого и двадцатого элементов РАВНОЗНАЧНОСТЬ. Выход седьмого элемента ИЛИ соединен со вторыми входами первого, пятого, восьмого, двенадцатого, пятнадцатого и девятнадцатого элементов РАВНОЗНАЧНОСТЬ. Основной технический результат изобретения заключается в понижении конструктивной сложности сумматора унитарных кодов по модулю семь. Названный технический результат достигается путем введения в логическую схему сумматора унитарных кодов по модулю семь новых логических элементов (элементов РАВНОЗНАЧНОСТЬ), а также изменением межсоединений в логической схеме сумматора. На чертеже (фиг. 1) представлена схема сумматора унитарных кодов по модулю семь. Сумматор унитарных кодов по модулю семь содержит семь элементов ИЛИ 1, 2,7, двадцать один элемент РАВНОЗНАЧНОСТЬ 8, 9 28, семь элементов И 29, 3035, семь входов первого операнда 36, 3742,семь входов второго операнда 43, 4449 и семь выходов 50, 5156. Сумматор унитарных кодов по модулю семь работает следующим образом. На входы 36,3742 сумматора поступает унитарный двоичный код первого операнда А(а 0, 1 а 6), на входы 43,4449 - унитарный двоичный код второго операнда В(0, 16), где а 0, 1 а 6, 0, 160, 1. При этом а 1(1) тогда и только тогда, когда( 7) (( 7, где 0, 16. На выходах 50, 5156 сумматора формируется унитарный двоичный код результата суммы(0, 16), где 0,160,1. При этом 1 тогда и только тогда, когда АВ( 7). Первообразная сумматора унитарных кодов по модулю имеет вид 2 Работа сумматора унитарных кодов по модулю семь описывается таблицей. Достоинством сумматора унитарных кодов по модулю семь является низкая конструктивная сложность устройства по числу входов логических элементов, равная 77 (в то время как сложность сумматорапрототипа составляет 147), а также относительно высокое быстродействие, которое вычисляется как 3, где- задержка на логический элемент. Таблица, описывающая работу сумматора унитарных кодов по модулю семь Входы Унитарный двоичный Унитарный двоичный код перкод второго операнда вого операнда В(0, 16) А(0, 12) а 0 а 1 а 2 а 3 а 4 а 5 а 6012345 36 37 38 39 40 41 42 43 44 45 46 47 48 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 0 0 0 0 1 1 0 0 0 0 0 Выходы Унитарный двоичный код результата суммы(0, 16) 6 0 1 2 3 4 5 49 50 51 52 53 54 55 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 Государственный патентный комитет Республики Беларусь. 220072, г. Минск, проспект Ф. Скорины, 66. 4

МПК / Метки

МПК: G06F 7/49

Метки: модулю, унитарных, кодов, сумматор, семь

Код ссылки

<a href="https://by.patents.su/4-3704-summator-unitarnyh-kodov-po-modulyu-sem.html" rel="bookmark" title="База патентов Беларуси">Сумматор унитарных кодов по модулю семь</a>

Предыдущий патент: Система промывки доильной установки

Следующий патент: Устройство для попеременной подачи защитных газов

Случайный патент: Крыло ветроустановки, парусный ветродвигатель и ветроустановка со средствами ее крепления