Вычислительное устройство по модулю три

Текст

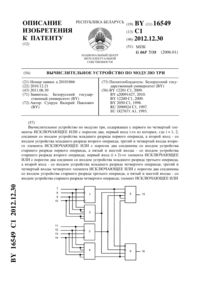

(51) МПК НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ПО МОДУЛЮ ТРИ(71) Заявитель Белорусский государственный университет(72) Автор Супрун Валерий Павлович(73) Патентообладатель Белорусский государственный университет(57) Вычислительное устройство по модулю три, характеризующееся тем, что содержит первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три, выход первого из которых соединен с выходом младшего разряда результата, а выход второго - с выходом старшего разряда результата, вход младшего разряда первого операнда соединен с первым и вторым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три и с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три, второй и третий входы которого соединены со входом старшего разряда первого операнда и с третьим входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три, четвертый вход которого соединен со входом младшего разряда второго операнда и с четвертым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три, пятый вход которого соединен со входом старшего разряда второго операнда и с пятым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три, шестой вход которого соединен с шестым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три и с первым настроечным входом устройства, второй настроечный вход которого соединен с седьмым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три, а третий настроечный вход - с седьмым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три. Изобретение относится к области вычислительной техники, автоматики и микроэлектроники и может быть использовано для построения систем передачи и обработки дис 18234 1 2014.06.30 кретной информации, построения систем аппаратного контроля, а также для построения вычислительных устройств, реализующих алгоритмы модулярной арифметики, и цифровых устройств, работающих в системе остаточных классов. Известен сумматор по модулю три, содержащий два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, четыре входа и два выхода 1. Сложность сумматора (по числу входов логических элементов) равна 12. Известный сумматор, как и заявляемое устройство, содержит два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого из которых соединен с выходом младшего разряда результата, а выход второго - с выходом старшего разряда результата, с тем лишь отличием,что в известном сумматоре элементы ИСКЛЮЧАЮЩЕЕ ИЛИ выполнены с порогом два,а в изобретении - с порогом три. Так как известный сумматор предназначен для вычисления операции( 3),то основным его недостатком являются низкие функциональные возможности, поскольку сумматор не реализует арифметические операции( 3) и( 3). Наиболее близким по конструкции и функциональным возможностям техническим решением к предлагаемому устройству является вычислительное устройство по модулю три, содержащее два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три, четыре информационных и один настроечный входа,два выхода 2. Устройство предназначено для выполнения операций( 3) и( 3), а его сложность равна 14. Устройство-прототип, как и заявляемое устройство, содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три, -й вход которого, где 1, 2, соединен с входом младшего разряда -го операнда, третий и четвертый входы соединены с входом старшего разряда первого операнда, пятый вход соединен с входом старшего разряда второго операнда, а выход - с выходом старшего разряда результата. Недостатком устройства-прототипа является низкое быстродействие, определяемое глубиной логической схемы, которое составляет 2, где- задержка на один логический элемент. Изобретение направлено на решение технической задачи повышения быстродействия устройства при вычислении операций( 3),( 3) и( 3). Вычислительное устройство по модулю три характеризуется тем, что содержит первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три, выход первого из которых соединен с выходом младшего разряда результата, а выход второго - с выходом старшего разряда результата. Вход младшего разряда первого операнда соединен с первым и вторым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три и с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три. Второй и третий входы второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три соединены с входом старшего разряда первого операнда и с третьим входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три. Четвертый вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три соединен с входом младшего разряда второго операнда и с четвертым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три. Пятый вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три соединен с входом старшего разряда второго операнда и с пятым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три. Шестой вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три соединен с шестым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три и с первым настроечным входом устройства. 18234 1 2014.06.30 Второй настроечный вход устройства соединен с седьмым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три, а третий настроечный вход - с седьмым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три. Основной технический результат изобретения заключается в повышении быстродействия (уменьшение глубины логической схемы) устройства при вычислении операций( 3),( 3) и( 3). Названный эффект достигается путем введения в логическую схему вычислительного устройства по модулю три второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три, а также посредством удаления из схемы двух элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и изменения соединений между логическими элементами схемы устройствапрототипа. На фигуре представлена схема вычислительного устройства по модулю три. Вычислительное устройство по модулю три содержит два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом три 1 и 2, четыре информационных входа 3, 4, 5 и 6, три настроечных входа 7, 8 и 9, два выхода 10 и 11. Первый и второй операндыизадаются двухразрядными двоичными кодами(1, 2) и(1, 2), где 1, 1 - первые (младшие) разряды операндов 2, 2 - вторые(старшие) разряды операндов, т.е.122 и 122. В соответствии с выбранным модулем, равным 3, операндыимогут принимать значения 0 (00), 1 (01), 2 (10). В этой связи результат выполнения арифметических операций( 3),( 3) и( 3) задается двухразрядными двоичными кодами(1, 2),(1, 2) и(1, 2), где 122,122 и 122. Заявляемое устройство работает следующим образом. На информационные входы 3 и 4 устройства поступают значения младшего 1 и старшего 2 разрядов первого операнда 122, на информационные входы 5 и 6 - значения младшего 1, и старшего 2 разрядов второго операнда 122, на настроечные входы 7, 8 и 9 - значения переменных 1, 2 и 3. Если 10 и 232, то на выходах 10 и 11 устройства формируются значения младшего 1 и старшего 2 разрядов результата выполнения операции( 3) если 11, 21 и 32, то на выходах 10 и 11 устройства формируются значения младшего 1 и старшего 2 разрядов результата выполнения операции( 3) если 11, 22 и 31, то на выходах 10 и 11 устройства формируются значения младшего 1 и старшего 2 разрядов результата выполнения операции( 3), где 122,122 и 1 22. Первообразные функции заявляемого вычислительного устройства по модулю три имеют вид 1, если 12212123,1 (1,2 , 1,2 , 1,2 )0 в противном случае,1, если 1312 2123,2 (1,3 , 1 ,2 , 1,2 )0 в противном случае. Если 10, 22 и 32, то 1(0, 2, 1, 2, 1, 2)1(1, 2, 1, 2),2(0, 2, 1, 2, 1, 2)2(1, 2, 1, 2) и 1, если 21212 23,1 (1,2 , 1,2 )0 в противном случае,1, если 12 212 23,2 (1,2 , 1,2 )0 в противном случае. 18234 1 2014.06.30 Входы Выходы Двоичный код Двоичный код Двоичный код(1, 2) реСигналы настройки первого операнда второго операнда зультата умножения(1, 2)(1, 2)( 3) 1 2 3 2 1 2 1 2 (2) 1 (Р 1) 7 8 9 4 3 6 5 11 10 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 1 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 1 0 1 0 1 1 0 1 1 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 1 1 0 0 1 1 1 0 1 0 0 1 Двоичный код Двоичный код Двоичный код(1, 2) реСигналы настройки первого операнда второго операнда зультата сложения(1, 2)(1, 2)( 3) 1 2 3 2 1 2 1 2 (2) 1 (1) 7 8 9 4 3 6 5 11 10 1 0 0 0 0 0 0 0 0 1 1 0 0 0 0 1 0 1 1 0 1 0 0 1 0 1 0 1 0 0 0 1 0 0 0 1 1 1 0 0 1 0 1 1 0 1 0 1 0 1 1 0 0 0 1 0 0 1 0 0 0 1 0 1 1 0 1 0 0 1 0 0 1 0 1 1 0 1 0 0 1 Двоичный код Двоичный код Двоичный код(1, 2) реСигналы настройки первого операнда второго операнда зультата вычитания(1, 2)(1, 2)( 3) 1 2 3 2 1 2 1 2 (2) 1 (1) 7 8 9 4 3 6 5 11 10 1 0 0 0 0 0 0 0 0 1 0 1 0 0 0 1 1 0 1 1 0 0 0 1 0 0 1 1 0 0 0 1 0 0 0 1 1 0 1 0 1 0 1 0 0 1 1 0 0 1 1 0 1 0 1 0 0 1 0 0 0 1 0 1 0 1 1 0 0 1 0 1 1 1 0 1 0 1 0 0 0 Если 11, 2 и 32, то 1(1, 1, 1, 2, 1, 2)1(1, 2, 1, 2),2(1, 2, 1, 2, 1, 2)2(1, 2, 1, 2) и 18234 1 2014.06.30 1, если 2122122,1 (1,2 , 1,2 )0 в противном случае,1, если 12 212 22,2 (1,2 , 1,2 )0 в противном случае. Если 11, 22 и 31, то 1(1, 2, 1, 2, 1, 2)1(1, 2, 1, 2),2(1, 1, 1, 2, 1, 2)2(1, 2, 1, 2) и 1, если 21212 22,1 (1,2 , 1,2 )0 в противном случае,1, если 12 22122, 2 (1,2 , 1,2 )0 в противном случае. Работа вычислительного устройства по модулю три описывается таблицей истинности логических функций 1, 2, 1, 2, 1 и 2 (таблица), которые реализуются на его выходах при соответствующей настройке. Основным достоинством вычислительного устройства по модулю три является высокое быстродействие логической схемы устройства, равное , где- задержка на один логический элемент. Кроме того, устройство имеет более широкие функциональные возможности по сравнению с устройством-прототипом. К дополнительным достоинствам заявляемого устройства необходимо отнести тот факт, что его конструктивная сложность совпадает со сложностью устройства-прототипа. Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20. 5

МПК / Метки

МПК: G06F 7/38

Метки: вычислительное, модулю, три, устройство

Код ссылки

<a href="https://by.patents.su/5-18234-vychislitelnoe-ustrojjstvo-po-modulyu-tri.html" rel="bookmark" title="База патентов Беларуси">Вычислительное устройство по модулю три</a>

Предыдущий патент: Автоматическая сифонная безарматурная фильтрующая установка для обезжелезивания подземных вод

Следующий патент: Инструмент для отделочно-упрочняющей обработки вала

Случайный патент: Кристаллизатор для непрерывного и непрерывно-циклического литья