Вычислительное устройство по модулю три

Номер патента: 17664

Опубликовано: 30.10.2013

Текст

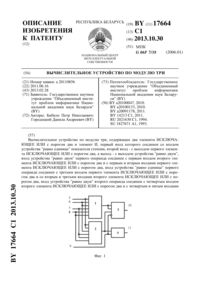

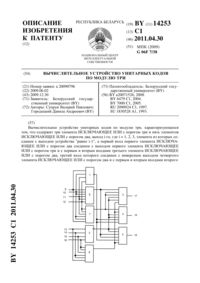

(51) МПК НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ПО МОДУЛЮ ТРИ(71) Заявитель Государственное научное учреждение Объединенный институт проблем информатики Национальной академии наук Беларуси(72) Авторы Бибило Петр Николаевич Городецкий Данила Андреевич(73) Патентообладатель Государственное научное учреждение Объединенный институт проблем информатики Национальной академии наук Беларуси(57) Вычислительное устройство по модулю три, содержащее два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и элемент И, первый вход которого соединен со входом устройства равно единице показателя степени, второй вход - с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, а выход - с выходом устройства равно двум,вход устройства равно двум первого операнда соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с первым и вторым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, вход устройства равно единице первого операнда соединен с третьим входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и со вторым и третьим входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, вход устройства равно двум второго операнда соединен с четвертым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с четвертым и пятым входами 17664 1 2013.10.30 первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, вход устройства равно единице второго операнда соединен с шестым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с пятым и шестым входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два мажоритарный элемент с порогом два, первый и второй входы которого соединены с выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, третий вход соединен с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два,инверсный вход соединен со входом устройства равно единице показателя степени, а выход - с выходом устройства равно единице. Изобретение относится к области вычислительной техники, автоматики и микроэлектроники и может быть использовано для построения систем передачи и переработки дискретной информации, построения систем аппаратного контроля, а также для построения вычислительных устройств, реализующих алгоритмы модулярной арифметики, и цифровых устройств, работающих в системе остаточных классов. Известно вычислительное устройство по модулю три 1, выполняющее операцию( 3) и содержащее два мажоритарных элемента с порогом два, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И, пять входов и два выхода. Недостатком вычислительного устройства является низкое быстродействие, определяемое глубиной схемы и равное 4, где- задержка одного логического элемента. Наиболее близким по конструкции и функциональным возможностям техническим решением к предлагаемому является вычислительное устройство по модулю три 2, содержащее два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом один и элемент И, пять входов и два выхода. Недостатком устройства-прототипа является низкое быстродействие, определяемое глубиной схемы и равное 3, где- задержка одного логического элемента. Изобретение направлено на решение технической задачи повышения быстродействия устройства при реализации операции ( 3). Задача решается следующим образом. Вычислительное устройство по модулю три,содержащее два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и элемент И, первый вход которого соединен со входом устройства равно единице показателя степени, второй вход - с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, а выход с выходом устройства равно двум. Вход устройства равно двум первого операнда соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с первым и вторым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два. Вход устройства равно единице первого операнда соединен с третьим входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и со вторым и третьим входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два. Вход устройства равно двум второго операнда соединен с четвертым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с четвертым и пятым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два. Вход устройства равно единице второго операнда соединен с шестым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с пятым и шестым входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два. Мажоритарный элемент с порогом два, первый и второй входы которого соединены с выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, третий вход соединен с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, инверсный вход соединен со входом устройства равно единице показателя степени, а выход - с выходом устройства равно единице. Основной технический результат изобретения заключается в повышении быстродействия (уменьшения глубины логической схемы) вычислительного устройства при выполнении операции ( 3). 2 17664 1 2013.10.30 На фиг. 1 представлена схема заявляемого вычислительного устройства по модулю три, работа которого описывается таблицей истинности (фиг. 2). Вычислительное устройство по модулю три содержит два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два 1 и 2, мажоритарный элемент с порогом два 3, элемент И 4, пять входов 59 и два выхода 10 и 11. Первый и второй операнды , , а также показатель степенизадаются двухразрядными двоичными кодами(1, 2),(1, 2) и(1, 2), где 1, 1, 1 - первые(младшие) разряды операндов и показателя степени 2, 2, 2 - вторые (старшие) разряды операндов и показателя степени, т.е.122,122 и 122. В соответствии с выбранным модулем Р 3 показатель и основание степени могут принимать значения 0 (00), 1 (01), 2 (10). Результат выполнения операции ( 3),задается двухразрядным двоичным кодом(1,2), где 122. Вычислительное устройство по модулю три работает следующим образом. На входы устройства 6 и 8 подаются значения младших разрядов 1,1 первогои второго операндовсоответственно на входы 5 и 7 - значения старших разрядов 2, 2 первогои второгооперандов соответственно, на вход 9 - значение младшего разряда 1 показателя степени , на выходе 10 реализуется младший разряд 1, на выходе 11 - старший разряд 2 результата выполнения операции ( 3). Логическая схема вычислительного устройства по модулю три (фиг. 1) синтезирована по следующим аналитическим представлениям функций 1 и 2 1, если 21 (1,2 , 1,2 )2 (1,2 , 1 ,2 )12 10 в противном случае,22(1,2,1,2)1,где 1, если 2122122 1 (1 ,2 , 1 ,2 )0 в противном случае,1, если 12 212 222 ( 1 ,2 , 1 ,2 )0 в противном случае. Фиг. 2 представляет собой таблицу истинности логических функций 1 и 2, описывающих работу вычислительного устройства по модулю три. Отметим, что при реализации операции возведения в степень возникает неопределенность вида 0. Так как в модулярной арифметике 0( ), то 00( ). Следовательно, здесь 00( 3). Основным достоинством вычислительного устройства является высокое быстродействие,определяемое глубиной схемы и равное 2, где- задержка одного логического элемента. К дополнительным достоинствам необходимо отнести небольшое число внешних выводов, равное 7, и относительно небольшую конструктивную сложность (по числу входов логических элементов), равную 18. Источники информации 1. Патент РБ 12977, МПК 067/38, 2010. 2. Заявка на изобретение 20100047, МПК 06 7/00, 7/38, 2010 (прототип). Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20. 4

МПК / Метки

МПК: G06F 7/38

Метки: устройство, модулю, три, вычислительное

Код ссылки

<a href="https://by.patents.su/4-17664-vychislitelnoe-ustrojjstvo-po-modulyu-tri.html" rel="bookmark" title="База патентов Беларуси">Вычислительное устройство по модулю три</a>

Предыдущий патент: Способ получения полимерного электретного волокнистого материала

Следующий патент: Устройство для защиты электрооборудования от коммутационных перенапряжений в низковольтных электрических сетях

Случайный патент: Предметный стол