Вычислительное устройство унитарных кодов по модулю три

Номер патента: 10221

Опубликовано: 28.02.2008

Авторы: Супрун Валерий Павлович, ГОРОДЕЦКИЙ Данила Андреевич

Текст

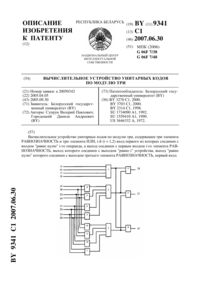

(51) МПК (2006) НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО УНИТАРНЫХ КОДОВ ПО МОДУЛЮ ТРИ(71) Заявитель Белорусский государственный университет(72) Авторы Супрун Валерий Павлович Городецкий Данила Андреевич(73) Патентообладатель Белорусский государственный университет(57) Вычислительное устройство унитарных кодов по модулю три, содержащее три элемента РАВНОЗНАЧНОСТЬ, выход -го, где 1, 2, 3, из которых соединен с -м выходом устройства, отличающееся тем, что содержит первый и второй элементы ЗАПРЕТ, первый и второй элементы И, первый и второй элементы ИЛИ-НЕ, мажоритарный элемент с порогом два, выход которого соединен с первым входом первого элемента РАВНОЗНАЧНОСТЬ и первым входом второго элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен с выходом первого элемента ИЛИ-НЕ и первым входом третьего элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен со вторым входом первого элемента РАВНОЗНАЧНОСТЬ и с выходом второго элемента ИЛИ-НЕ, первый вход которого соединен с выходом первого элемента И, первый вход которого соединен с первым входом 10221 1 2008.02.28 второго элемента И, с входами запрета первого и второго элементов ЗАПРЕТ и с управляющим входом устройства, вход которого равно нулю первого операнда соединен с первым входом первого элемента ИЛИ-НЕ и с первым входом мажоритарного элемента с порогом два, второй вход которого соединен с входом устройства равно двум первого операнда и со вторым входом второго элемента ИЛИ-НЕ, третий вход которого соединен с выходом второго элемента ЗАПРЕТ, прямой вход которого соединен с входом устройства равно двум второго операнда, с третьим входом мажоритарного элемента с порогом два и со вторым входом второго элемента И, выход которого соединен со вторым входом первого элемента ИЛИ-НЕ, третий вход которого соединен с выходом первого элемента ЗАПРЕТ, прямой вход которого соединен со вторым входом первого элемента И, четвертым входом мажоритарного элемента с порогом два и с входом устройства равно нулю второго операнда. Изобретение относится к области вычислительной техники и микроэлектроники и может быть использовано для построения средств аппаратурного контроля и цифровых устройств, работающих в системе остаточных классов. Известен сумматор унитарных кодов по модулю три, который содержит шесть элементов РАВНОЗНАЧНОСТЬ, три элемента И, шесть входов и три выхода 1. Сложность сумматора (по числу входов логических элементов) равна 18, а быстродействие, определяемое глубиной схемы, составляет 2, где- задержка на логический элемент. Число внешних выводов сумматора равно девяти. Недостатками известного сумматора являются высокая конструктивная сложность и большое число внешних выводов. Наиболее близким по функциональным возможностям и конструкции техническим решением к предлагаемому является сумматор унитарных кодов по модулю три, который содержит три элемента ИЛИ, три элемента РАВНОЗНАЧНОСТЬ, шесть входов и три выхода 2. Сложность сумматора равна 12, а быстродействие - 2, где- задержка на логический элемент. При этом число внешних выводов равно девяти. Недостатками известного сумматора являются низкие функциональные возможности,поскольку сумматор не реализует операцию вычитания в унитарных кодах по модулю три,а также большое число внешних выводов. Изобретение направлено на решение следующих технических задач 1) расширение функциональных возможностей сумматора за счет реализации операции вычитания в унитарных кодах по модулю три 2) уменьшение числа внешних выводов вычислительного устройства унитарных кодов по модулю три. Вычислительное устройство унитарных кодов по модулю три содержит три элемента РАВНОЗНАЧНОСТЬ, выход -го (1, 2, 3) элемента из которых соединен с -м выходом устройства. В отличие от прототипа в устройство дополнительно введены первый и второй элементы ЗАПРЕТ, первый и второй элементы И, первый и второй элементы ИЛИ-НЕ,мажоритарный элемент с порогом два. Выход мажоритарного элемента с порогом два соединен с первым входом первого элемента РАВНОЗНАЧНОСТЬ и первым входом второго элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен с выходом первого элемента ИЛИ-НЕ и первым входом третьего элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен со вторым входом первого элемента РАВНОЗНАЧНОСТЬ и с выходом второго элемента ИЛИ-НЕ. Первый вход второго элемента ИЛИ-НЕ соединен с выходом первого элемента И, первый вход которого соединен с первым входом второго элемента И, с входами запрета первого и второго элементов ЗАПРЕТ и с управляющим входом устройства. Вход устройства равно нулю первого операнда соединен с первым входом первого элемента ИЛИ-НЕ и с первым входом мажоритарного элемента с порогом два,второй вход которого соединен с входом устройства равно двум первого операнда и со 2 10221 1 2008.02.28 вторым входом второго элемента ИЛИ-НЕ. Третий вход первого элемента ИЛИ-НЕ соединен с выходом первого элемента ЗАПРЕТ, прямой вход которого соединен с входом устройства равно двум второго операнда, с третьим входом мажоритарного элемента с порогом два и со вторым входом второго элемента И, выход которого соединен со вторым входом первого элемента ИЛИ-НЕ. Третий вход второго элемента ИЛИ-НЕ соединен с выходом второго элемента ЗАПРЕТ, прямой вход которого соединен со вторым входом первого элемента И, четвертым входом мажоритарного элемента с порогом два и с входом устройства равно нулю второго операнда. Основные технические результаты предлагаемого изобретения заключаются в расширении функциональных возможностей устройства и в уменьшении числа внешних выводов сумматора унитарных кодов по модулю три. Названные технические результаты достигаются путем введения в логическую схему новых логических элементов (элементов ЗАПРЕТ, элементов И, элементов ИЛИ-НЕ и мажоритарного элемента с порогом два). На чертеже (фигура) представлена схема вычислительного устройства унитарных кодов по модулю три. Вычислительное устройство содержит два элемента ЗАПРЕТ 1 и 2,два элемента И 3 и 4, два элемента ИЛИ-НЕ 5 и 6, мажоритарный элемент с порогом два 7,три элемента РАВНОЗНАЧНОСТЬ 8, 9 и 10, четыре информационных входа 1114,управляющий вход 15 и три выхода 16, 17 и 18. Вычислительное устройство унитарных кодов по модулю три работает следующим образом. На входы 11 и 14 сумматора поступают значения а 0 и а 2 унитарного двоичного кода первого операнда А(а 0, а 1, а 2) соответственно, на входы 12 и 13 поступают значения 0 и 2 унитарного двоичного кода второго операнда В(0, 1, 2) соответственно,где 0, , 2, 0, 1, 20,1. При этом 1 (1) тогда и только тогда, когда А( 3) (В( 3, где 0, 1, 2. На управляющий вход 15 подается управляющий сигнал , принимающий значения из множества 0, 1. Если 0, то на выходах вычислительного устройства 17, 16 и 18 формируется унитарный двоичный код(0, 1, 2) результата выполнения операции А( 3). Если 1, то на выходах вычислительного устройства 16, 18 и 17 формируется унитарный двоичный код(0, 1, 2) результата выполнения операции А - В( 3). Здесь(0, 1, 2) и(0, 1, 2), где 0, 0, 1, 1, 2, 20, 1. Причем 1 (1) тогда и только тогда, когда АВ( 3) (соответственно А - В( 3 и 0, 1, 2. Первообразная вычислительного устройства унитарных кодов по модулю три имеет вид 1 ( )022( 0 ,0 ,2 ,2 ),2 ( )020( 0 ,0 ,2 ,2 ),2 ( )020022 ,где-логическая операция равнозначность,(0, 0, 2, 2) - функция, реализуемая на выходе мажоритарного элемента с порогом два, т.е. 1, если 00222( 0 ,0 ,2 ,2 )0 в противном случае. Отметим, что здесь 1 , если 0, 0 , если 0, , если 0,1 ( )3 ( )2 2 ( )1 , если 1. 0 , если 1,2 , если 1,Работа вычислительного устройства унитарных кодов по модулю три описывается таблицей истинности логических функций 0, 1, 2, 0, 1, 2. К основным достоинствам предлагаемого вычислительного устройства унитарных кодов по модулю три можно отнести следующее 1) широкие функциональные возможности,поскольку устройство реализует операции сложения и вычитания унитарных кодов по мо 3 10221 1 2008.02.28 дулю три 2) небольшое число внешних выводов, равное 8. В то время как устройствопрототип реализует только операцию сложения унитарных кодов по модулю три, а число его внешних выводов равно 9. Вычислительное устройство унитарных кодов по модулю три Входы Выходы Управляющий Унитарный двоичный Унитарный двоичный Унитарный двоичный двоичный код код первого операнда код второго операнда код результата суммы а 0 1 а 2 0 1 2 0 1 2 15 11 14 12 13 17 16 18 0 1 0 0 1 0 0 1 0 0 0 1 0 0 0 1 0 0 1 0 0 1 0 0 0 0 1 0 0 1 0 0 1 0 1 0 0 0 1 0 0 0 1 0 0 1 0 0 0 1 0 0 1 0 0 0 1 1 0 0 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 1 0 1 0 0 0 0 0 1 0 0 1 0 1 0 Управляющий Унитарный двоичный Унитарный двоичный Унитарный двоичный двоичный код код первого операнда код второго операнда код результата разности Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20. 4

МПК / Метки

МПК: G06F 7/38

Метки: устройство, кодов, модулю, унитарных, вычислительное, три

Код ссылки

<a href="https://by.patents.su/4-10221-vychislitelnoe-ustrojjstvo-unitarnyh-kodov-po-modulyu-tri.html" rel="bookmark" title="База патентов Беларуси">Вычислительное устройство унитарных кодов по модулю три</a>

Предыдущий патент: Металлическая связка для получения композиционного материала и способ ее приготовления

Следующий патент: Способ измерения амплитуды и частоты вибрации

Случайный патент: Рулевой механизм с гидравлическим усилителем