Сумматор широкополосный

Номер патента: 7877

Опубликовано: 28.02.2006

Авторы: Пилипович Владимир Антонович, Есман Александр Константинович, Кулешов Владимир Константинович

Текст

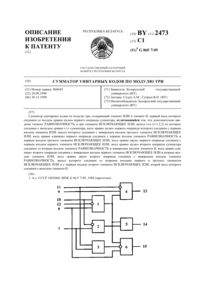

(51)06 7/50 НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ(71) Заявитель Государственное научное учреждение Институт электроники Национальной академии наук Беларуси(72) Авторы Пилипович Владимир Антонович Есман Александр Константинович Кулешов Владимир Константинович(73) Патентообладатель Государственное научное учреждение Институт электроники Национальной академии наук Беларуси(57) 1. Сумматор широкополосный, содержащий два транзистора, связанных между собой в транзисторный каскад и с выходом устройства, отличающийся тем, что содержит полосковый разветвитель и набор нелинейных элементов, выполненных в виде первой и второй нелинейных формирующих линий и первого и второго двухэлектродных нелинейных элементов, причем вход первой нелинейной формирующей линии через полосковый разветвитель связан с входами устройства, а выход через первый двухэлектродный нелинейный элемент соединен с транзисторным каскадом и через второй двухэлектродный нелинейный элемент - со второй нелинейной формирующей линией, выход которой связан с транзисторным каскадом, при этом первый и второй двухэлектродные нелинейные элементы соединены с соответствующими цепями смещения напряжения, а первая и вторая нелинейные формирующие линии выполнены солитонными с низким волновым сопротивлением, согласованным с импедансом используемых двухэлектродных нелинейных элементов. 2. Сумматор по п. 1, отличающийся тем, что первый и второй двухэлектродные нелинейные элементы выполнены в виде туннельных диодов. 7877 1 2006.02.28 Изобретение относится к элементной базе вычислительной техники и может быть использовано в высокопроизводительных системах обработки изображений. Наиболее близким по технической сущности является сумматор на КМД-транзисторах 1, содержащий тактовые транзисторы п-типа и р-типа, дополнительный инвертор и М разрядов, каждый из которых состоит из первого и второго инверторов, триггера, 4-х транзисторов р-типа и логического блока, выполненного на 20-ти транзисторах п-типа. Указанный сумматор не обеспечивает высокое быстродействие, т.к. в каждом логическом блоке имеется 7 транзисторных каскадов, цепь сквозного переноса одного разряда содержит 3 каскада последовательно включенных инверторов, поэтому процесс суммирования содержит 3 М 7 переключений КМД-транзисторов, которые не являются достаточно широкополосными. Техническая задача - увеличение быстродействия при одновременном упрощении. Поставленная техническая задача в заявленном устройстве решается тем, что в сумматор, содержащий 2 транзистора, связанных между собой в транзисторный каскад и с выходом устройства, введены полосковый разветвитель и набор нелинейных элементов, выполненных в виде первой и второй нелинейных формирующих линий и первого и второго двухэлектродных нелинейных элементов, причем вход первой нелинейной формирующей линии через полосковый разветвитель связан с входами устройства, выход через первый двухэлектродный нелинейный элемент (ДНЭ) соединен с транзисторным каскадом и через второй двухэлектродный нелинейный элемент - со второй нелинейной формирующей линией, выход которой связан с транзисторным каскадом, при этом первый и второй двухэлектродные нелинейные элементы соединены с соответствующими цепями смещения напряжения, а первая и вторая нелинейные формирующие линии выполнены солитонными с низким волновым сопротивлением, согласованным с импедансом используемых двухэлектродных нелинейных элементов. Для эффективного решения поставленной технической задачи первый и второй ДНЭ выполнены в виде туннельных диодов. Сущность изобретения представлена на фигуре, где 1 - полосковый разветвитель, 2,5 - первая и вторая нелинейные формирующие линии, 3, 4 - первый и второй двухэлектродные нелинейные элементы (ДНЭ), 6 - транзисторный каскад. Входы устройства через полосковый разветвитель 1 соединены с первой нелинейной формирующей линией 2, которая через первый ДНЭ 3 соединена с транзисторным каскадом 6, а через второй ДНЭ 4 - с второй нелинейной формирующей линией 5. Последняя подключена к транзисторному каскаду 6, выход которого является выходом устройства. В конкретном исполнении полосковый разветвитель 1 - это копланарный разветвитель с геометрией расположения проводников, имеющих выходное волновое сопротивление,согласованное с нагрузкой. Первая 2 и вторая 5 нелинейные формирующие линии - это квазираспределенные копланарные полосковые линии с равномерно расположенными в них нелинейными элементами, диодами Д 1 Дк и Д 1 Дп, например Д 524 Б. Дисперсионные свойства таких линий позволяют формировать в них солитоноподобные импульсы с пикосекундными фронтами. Первый 3 и второй 4 ДНЭ, выполненные, например, из туннельных диодов, идеальным образом сопрягаются по волновому сопротивлению с низкоомными нелинейными формирующими линиями 2, 5 и таким образом могут работать в широкой полосе частот. Транзисторный каскад 6 выполнен на мощных полевых СВЧтранзисторах, при этом достаточно большая емкость базы таких транзисторов является элементом согласования транзисторного каскада 6 по волновому сопротивлению с выходом ДНЭ 3 и нелинейной формирующей линии 5. Работает сумматор следующим образом. Входные разрядные сигналыи У, закодированные в двоичной знакоразрядной системе счисления, последовательно поступают на входы устройства. При отсутствии входных разрядных сигналов на выходе также будет присутствовать нулевой логический уровень. При появлении одного из разрядных сигна 2 7877 1 2006.02.28 ловили У, указанный сигнал через входной разветвитель 1 поступает на вход первой нелинейной формирующей линии 2, по которой низкочастотные составляющие импульсных логических сигналов распространяются с меньшей скоростью, поэтому амплитуда А этих сигналов на выходе линии 2 увеличивается, фронт и срез сокращаются по длительности. Ввиду того, что напряжения смещения первого 3 ДНЭ - И 1 и второго 4 ДНЭ - И 2 выбраны в соответствии с выражением И 1 АИ 22 А, то сигнал амплитудой А смещает в положительном направлении только первый 3 ДНЭ, часть амплитуды указанного сигнала,пройдя через первый 3 ДНЭ, поступает сразу на вход транзисторного каскада 6, где усиливается по амплитуде и поступает на выход устройства. Если разрядные сигналыи У поступают на вход устройства одновременно, то во входном разветвителе 1 они складываются по амплитуде и аналогично вышеописанному проходят через нелинейную формирующую линию 2, где фронт и срез суммарного импульсного разрядного сигналаУ укорачивается. Первый 3 ДНЭ отрывается только на фронте указанного сигнала, далее первый 3 ДНЭ переходит в закрытое состояние и открывается второй 4 ДНЭ, который пропускает часть амплитуды суммарного разрядного сигналаУ на вход второй нелинейной формирующей линии 5, где данный сигнал увеличивается по амплитуде. Кратковременный выброс с выхода первого 3 ДНЭ интегрируется на входной емкости транзисторного каскада 6 и на выход устройства не проходит. Суммарный разрядный сигналУ во второй нелинейной формирующей линии 5 задерживается на время тактового интервала и переходит в соседний такт и его значение изменяется в соответствии с весовыми коэффициентами двоичной системы счисления 21, т.е. этот сигнал, пришедший на вход транзисторного каскада 6, восстановленный в нем по амплитуде, представляет собой значение арифметической суммы разрядных сигналовУ. В избыточной двоичной знакоразрядной системе счисления существуют представления чисел, когда у значащих цифр имеются соседи только нулевые значения, поэтому в этом случае при суммировании возникают переносы только в соседние разряды. Полный сумматор в двоичной знакоразрядной системе состоит из двух описанных устройств одно - для положительной, второе - для отрицательной частей числа. Увеличение быстродействия сложения достигается за счет совмещения во времени операций логических - выявление совпадающих во времени сигналов, и формирования выходных сигналов, расположенных в требуемом временном интервале. Источники информации 1. Патент России 2185655, 2002. Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20.

МПК / Метки

МПК: G06F 7/50

Метки: сумматор, широкополосный

Код ссылки

<a href="https://by.patents.su/3-7877-summator-shirokopolosnyjj.html" rel="bookmark" title="База патентов Беларуси">Сумматор широкополосный</a>

Предыдущий патент: Способ сушки сыпучих материалов в кипящем слое и устройство для его осуществления

Следующий патент: Способ переработки технического лигнина с получением росторегулирующего вещества

Случайный патент: Устройство для полунепрерывного прессования длинномерных заготовок