Пороговый декодер сверточного кода

Номер патента: 17471

Опубликовано: 30.08.2013

Авторы: Королев Алексей Иванович, Конопелько Валерий Константинович, Аль-алем Ахмед Саид

Текст

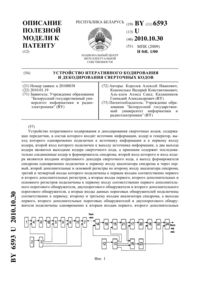

(51) МПК НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ ПОРОГОВЫЙ ДЕКОДЕР СВЕРТОЧНОГО КОДА(71) Заявитель Учреждение образования Белорусский государственный университет информатики и радиоэлектроники(72) Авторы Королев Алексей Иванович Конопелько Валерий Константинович Аль-алем Ахмед Саид(73) Патентообладатель Учреждение образования Белорусский государственный университет информатики и радиоэлектроники(57) Пороговый декодер сверточного кода, характеризующийся тем, что содержит последовательно соединенные демультиплексор, корректор ошибок и мультиплексор, причем вход демультиплексора и выход мультиплексора являются соответственно входом и выходом устройства кодер, объединенный по входу с корректором ошибок, формирователь синдрома, анализатор синдрома, обнаружитель некорректируемых пакетных ошибок, обнаружитель частично корректируемых пакетных ошибок, обнаружитель корректируемых случайных и пакетных ошибок, дешифратор ошибок, 0 пороговых блоков и 0 блоков запрета,где 01, 2, 3 при этом второй вход формирователя синдрома подключен к соответствующему выходу демультиплексора, объединенные входы второй группы корректора ошибок и 0 групп анализатора синдрома подключены к выходам соответствующих блоков запрета, один из входов которых подключен к выходу дешифратора ошибок, входы 17471 1 2013.08.30 которого подключены соответственно к выходам обнаружителей некорректируемых пакетных ошибок, частично корректируемых пакетных ошибок и корректируемых случайных и пакетных ошибок, входы которых объединены со входами 0 пороговых блоков и подключены к соответствующим выходам анализатора синдрома, а выходы 0 пороговых блоков подключены ко второму входу соответствующего блока запрета, вход анализатора синдрома подключен через формирователь синдрома к выходу кодера, входы которого подключены к соответствующим выходам демультиплексора. Изобретение относится к технике электросвязи и может использоваться в устройствах помехоустойчивого кодирования при передаче двоичной информации по каналам связи. Известен двухканальный пороговый декодер сверточного кода, содержащий первый и второй распределители ветвей, первый и второй формирователи проверочных последовательностей, первый и второй формирователи синдромных последовательностей, первый и второй анализаторы синдромных последовательностей, первый и второй корректоры ошибок, первый и второй регистры сдвига, первый и второй сумматоры по модулю два,первый и второй формирователи интервалов анализа, первый и второй элементы совпадения, а также коммутатор, первый, второй и третий счетчики, блок фазовой автоподстройки частоты и элемент ИЛИ 1. Однако известному пороговому декодеру сверточного кода присущи следующие недостатки отсутствует возможность коррекции пакетных ошибок, превышающих гарантированную исправляющую способность сверточного кода, определяемую равенством-неравенством вида исп/2,- количество ортогональных проверок используемого сверточного кода более чем двухкратное увеличение объема оборудования декодера, определяемое использованием двух каналов декодирования. Известен пороговый декодер сверточного кода, содержащий кодер, анализатор синдрома, пороговый обнаружитель, корректор ошибок, первый и второй блоки запрета коррекции, дополнительный пороговый обнаружитель и обнаружитель пакетов 2. Однако известному пороговому декодеру сверточного кода присущи следующие недостатки возможность размножения ошибок при поступлении на вход декодера необнаруживаемого и некорректируемого пакета ошибок большая задержка информации при декодировании, так как на обнаружитель пакетов синдромные символы поступают в последовательном коде. Известен пороговый декодер сверточного кода, содержащий кодер, корректор ошибок,формирователь синдрома, анализатор синдрома, три пороговых блока, корректор пакетов ошибок, мультиплексор импульсов коррекции, блок формирования тактовых импульсов,элемент совпадения, пороговый счетчик, формирователь временного интервала, -триггер, инвертор, ключ и три блока запрета коррекции информационных и синдромных символов 3. Однако известный пороговый декодер сверточного кода обладает недостаточной помехоустойчивостью, которая определяется тем, что пороговый декодер корректирует пакеты ошибок только кратностью (длиной) 0 кодовых символов (0 - длина миниблока кодовых символов, зависящая от скорости передачи сверточного кода 0/0, 01, 2, 3 001 двоичных символов), а также исключается возможность частичной коррекции ошибочных информационных символов при поступлении на вход декодера пакета ошибок кратностью. Задача изобретения - повышение помехоустойчивости порогового декодера сверточного кода при передаче двоичной информации по каналам связи. Поставленная задача достигается тем, что пороговый декодер сверточного кода, характеризующийся тем, что содержит последовательно соединенные демультиплексор,2 17471 1 2013.08.30 корректор ошибок и мультиплексор, причем вход демультиплексора и выход мультиплексора являются соответственно входом и выходом устройства кодер, объединенный по входу с корректором ошибок, формирователь синдрома, анализатор синдрома, обнаружитель некорректируемых пакетных ошибок, обнаружитель частично корректируемых пакетных ошибок, обнаружитель корректируемых случайных и пакетных ошибок, дешифратор ошибок, 0 пороговых блоков и 0 блоков запрета, где 01, 2, 3 при этом второй вход формирователя синдрома подключен к соответствующему выходу демультиплексора,объединенные входы второй группы корректора ошибок и 0 групп анализатора синдрома подключены к выходам соответствующих блоков запрета, один из входов которых подключен к выходу дешифратора ошибок, входы которого подключены соответственно к выходам обнаружителей некорректируемых пакетных ошибок, частично корректируемых пакетных ошибок и корректируемых случайных и пакетных ошибок, входы которых объединены со входами 0 пороговых блоков и подключены к соответствующим выходам анализатора синдрома, а выходы 0 пороговых блоков подключены ко второму входу соответствующего блока запрета, вход анализатора синдрома подключен через формирователь синдрома к выходу кодера, входы которого подключены к соответствующим выходам демультиплексора. На фиг. 1 приведена структурная схема порогового декодера сверточного кода. На фиг. 2 (а и б), 3 (а и б), 4 (а и б) приведены некоторые структуры ошибок и соответствующие им синдромные конфигурации (синдромы), а именно фиг. 2 (а и б) - при коррекции случайных двухкратных (сл.2) и пакетных ошибок кратностью 4 двоичных символов фиг. 3 (а и б) - коррекция одиночных ошибок при приеме некорректируемых пакетных ошибок кратностью 5 двоичных символов фиг. 4 (а и б) - при приеме некорректируемых пакетных ошибок кратностью .6 и 7 двоичных символов. На фиг. 5 и 6 приведены соответственно функциональная схема и таблица с правилом формирования выходного сигнала порогового блока. На фиг. 7 приведена функциональная схема дешифратора ошибок 10, формирующего выходной сигнал по следующему правилу (фиг. 8). Пороговый декодер сверточного кода (фиг. 1) содержит последовательно соединенные демультиплексор 1, корректор ошибок 2 и мультиплексор 3, вход демультиплексора 1 и выход мультиплексора 3 являются соответственно входом и выходом порогового декодера, а также кодер 4, формирователь синдрома 5, анализатор синдрома 6, обнаружитель некорректируемых пакетных ошибок 7, обнаружитель частично корректируемых пакетных ошибок 8, обнаружитель корректируемых случайных и пакетных ошибок 9, дешифратор ошибок 10, 0 (01, 2, 3) пороговых блоков 11 и 0 блоков запрета 12, при этом второй вход формирователя синдрома 5 подключен к соответствующему выходу демультиплексора 1, а объединенные входы второй группы корректора ошибок 2 и 0 групп анализатора синдрома 6 подключены к выходам соответствующих блоков запрета 12,один из входов которых подключен к выходу дешифратора ошибок 10, входы которого подключены соответственно к выходам обнаружителей некорректируемых пакетных ошибок 7, частично корректируемых пакетных ошибок 8 и корректируемых случайных и пакетных ошибок 9, входы которых, объединенные с входами 0 пороговых блоков 11,подключены ко соответствующим выходам анализатора синдрома 6, а выходы 0 пороговых блоков 11 подключены ко второму входу соответствующего блока запрета 12, а вход анализатора синдрома 6 подключен через формирователь синдрома 5 к выходу кодера 4,входы которого подключены к соответствующим выходам демультиплексора 1. Пороговый декодер сверточного кода работает следующим образом. Рассмотрим принцип работы порогового декодера сверточного кода со скоростью передачи кода 0/02/3, корректирующего случайные, или независимые, ошибки (сл.) кратно 3 17471 1 2013.08.303 двоичных символов на длине кодового ограничения(1)0 22(81)327 кодовых символов, где- количество ортогональных проверочных уравнений (проверок),8 - максимальная степень порождающих полиномов сверточного кода, имеющих вид 1117 и 2138- формальная переменная или оператор задержки. Принятые символы кодовой последовательностив демультиплексоре 1 разделяются на символы 0 (02) информационных подпотоков и (00)(32)1 проверочных подпотоков. Принятые символы двух информационных подпотоков 1 и 2 одновременно поступают на входы корректора ошибок 2 и на входы кодера 4, в котором формируются символы проверочной последовательности сф., которые поступают в формирователь синдрома 5, в который поступают также символы принятой проверочной последовательности пер. производится формирование символов синдромной последовательностипо правилу пер.сф., где пер. и сф. - символы проверочных последовательностей соответственно принятой и сформированной. Структура синдромной последовательности зависит от типа ошибок в информационных и проверочных символах кодовой последовательности , а также от количества и структуры порождающих полиномов кода, т.е. каждому типу ошибок соответствует определенная структура синдромной последовательности, что позволяет пороговому декодеру определять (классифицировать) количество и тип принятых ошибок. Данное свойство синдромной последовательности положено в основу работы заявляемого (предложенного) порогового декодера сверточного кода. Вся совокупность синдромных последовательностей сверточного кода разделяется на три группы, так называемых, простых синдромных множеств, или конфигураций 4. Первая группа простых синдромных конфигураций соответствует некорректируемым пакетным ошибкам, кратность (длина) которых составляет 2(1) двоичных символов. Вторая группа простых синдромных конфигураций соответствует частично корректируемым информационным ошибкам при приеме некорректируемых пакетных ошибок. Третья группа простых синдромных конфигураций соответствует корректируемым случайным ошибкам кратностью сл./2 и пакетным ошибкам кратностью 2(1) двоичных символов, или битов. Сформированные символы синдромной последовательностипоследовательно поступают в анализатор синдрома 6, с выходов которого данные синдромные символы одновременно поступают на входы 0 пороговых блоков 11 и входы трех обнаружителей ошибок 7-9, каждый из которых имеет(1)(81)9 входов. Каждый из пороговых блоков 11 имеет три входа и выполняется в виде комбинационного автомата с порогом срабатывания П 1312. Из таблицы формирования (фиг. 6) следует, что если на вход порогового блока 11 поступят два или три ненулевых символа, то на выходе порогового блока сформируется ненулевой двоичный символ, или сигнал коррекции ошибочного информационного символа. Данный символ поступает на один из входов соответствующего блока запрета 12, а(1)9 синдромных символов, поступивших на входы обнаружителей ошибок 7-9, используются для классификации принятых ошибочных кодовых (информационных и проверочных) символов. Классификация ошибок производится по следующему правилу если структура сформированной синдромной конфигурации соответствует синдромной конфигурации обнаружителя ошибок 7-9, то на выходе данного обнаружителя ошибок формируется ненулевой двоичный символ, а в противном случае - нулевой двоичный символ. Сформированные обнаружителями ошибок 7-9 выходные сигналы поступают на соответствующие входы дешифратора ошибок 10, который формирует либо разрешающий,либо запрещающий сигнал коррекции информационных и синдромных символов, запистьюсл. 17471 1 2013.08.30 санных в анализаторе синдрома 6. Выходной сигнал дешифратора ошибок 10 поступает одновременно на соответствующий вход 0 блоков запрета 12. При обнаружении корректируемых случайных и пакетных ошибок (фиг. 2 (а и б на входы дешифратора 10 поступит кодовая комбинация 001 ненулевой двоичный символ поступает с выхода обнаружителя корректируемых случайных и пакетных ошибок 9, а нулевые двоичные символы с выходов обнаружителей ошибок 7 и 8. Дешифратором ошибок 10 формируется разрешающий сигнал коррекции, который поступает на один из входов 0 блоков запрета 12, на второй вход которых поступают сигналы коррекции с выхода соответствующего порогового блока 11. При обнаружении частично корректируемых ошибок (фиг. 3 (а и б в некорректируемых пакетных ошибках на вход дешифратора ошибок 10 поступает кодовая комбинация 010 ненулевой двоичный символ поступает с выхода обнаружителя частично корректируемых пакетных ошибок 8, а нулевые двоичные символы - с обнаружителей ошибок 7 и 9. Дешифратором ошибок 10 в данном случае также формируется разрешающий сигнал коррекции. В этом случае осуществляется выборочная, т.е. частичная, коррекция ошибочных информационных символов в некорректируемых пакетных ошибках соответствующими выходными сигналами с выходов определенных пороговых блоков. При обнаружении некорректируемых пакетных ошибок (фиг. 4 (а и б на входы дешифратора ошибок 10 поступает кодовая комбинация 100 ненулевой двоичный символ поступает с выхода обнаружителя некорректируемых пакетных ошибок 7, а нулевые двоичные символы - с обнаружителей ошибок 8 и 9. Дешифратором ошибок 10 формируется запрещающий сигнал коррекции как информационных, так и синдромных символов, что полностью исключает возможность размножения ошибок пороговым декодером. Информационные символы с выхода корректора ошибок 2 поступают на соответствующие входы мультиплексора 3 декодера, который формирует последовательный поток информационных символовиз символов 0 информационных подпотоков. Таким образом, коррекция случайных ошибок кратностью сл.2 двоичных символа и пакетных ошибок кратностью .3 и 4 двоичных символа (фиг. 2 (а и б, а также коррекция одиночных и двойных ошибочных информационных символов при приеме некорректируемых пакетных ошибок кратностью 5 двоичных символов (фиг. 3 (а и б и запрет коррекции информационных и синдромных символов при приеме некорректируемых пакетных ошибок кратностью 6 двоичных символов (фиг. 4 (а и б обеспечивают повышение помехоустойчивости порогового декодера сверточного кода при передаче двоичной информации по каналам связи. Лабораторные испытания подтвердили преимущества предложенного порогового декодера сверточного кода по сравнению с известным пороговым декодером энергетический выигрыш кодирования (ЭВК) составляет 3,5 дБ при вероятности ошибочного приема двоичного символа к 10-5 и полностью отсутствует эффект размножения ошибок. Источники информации 1. А.с. СССР 524316, МПК 03 13/49, 1976. 2. А.с. СССР 581589, МПК 03 13/25, 1977. 3. А.с. РБ 3901, МПК 03 13/00, 2007. 4. Касами Т., Токура Н., Ивадарии др. Теория кодирования. / Пер. с япон. под ред. Б.С. Цыбакова. - ММир, 1978. - С. 222-298. Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20. 8

МПК / Метки

МПК: H03M 13/23, H04L 1/00

Метки: декодер, сверточного, кода, пороговый

Код ссылки

<a href="https://by.patents.su/8-17471-porogovyjj-dekoder-svertochnogo-koda.html" rel="bookmark" title="База патентов Беларуси">Пороговый декодер сверточного кода</a>

Предыдущий патент: Динамометрический ключ с легкой и быстрой регулировкой величины момента затяжки

Следующий патент: Радиальный вентилятор (варианты)

Случайный патент: Светотехническое стекло