Сумматор унитарных кодов по модулю пять

Номер патента: 16188

Опубликовано: 30.08.2012

Авторы: ГОРОДЕЦКИЙ Данила Андреевич, Супрун Валерий Павлович

Текст

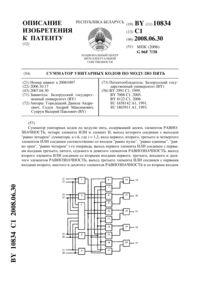

(51) МПК НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ СУММАТОР УНИТАРНЫХ КОДОВ ПО МОДУЛЮ ПЯТЬ(71) Заявитель Белорусский государственный университет(72) Авторы Супрун Валерий Павлович Городецкий Данила Андреевич(73) Патентообладатель Белорусский государственный университет(57) Сумматор унитарных кодов по модулю пять, характеризующийся тем, что содержит пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, выход -го, где 1, 2 5, из которых соединен с выходом сумматора равно -1 результата сложения, вход сумматора равно нулю первого операнда соединен с первым инверсным входом -го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, первый вход которого соединен со входом сумматора равно двум первого операнда, вход сумматора равно трем первого операнда 16188 1 2012.08.30 соединен со вторым и третьим входами -го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, четвертый, пятый и шестой входы которого соединены со входом сумматора равно четырем первого операнда, вход сумматора равно нулю второго операнда соединен с седьмым, восьмым и девятым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, с седьмым и восьмым входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, с седьмым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре и со вторым инверсным входом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, вход сумматора равно единице второго операнда соединен со вторым инверсным входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, с девятым, десятым и одиннадцатым входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, с восьмым и девятым входами третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре и с седьмым входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, вход сумматора равно двум второго операнда соединен со вторым инверсным входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, с десятым, одиннадцатым и двенадцатым входами третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, с восьмым и девятым входами четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре и с седьмым входом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, вход сумматора равно трем второго операнда соединен с десятым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, со вторым инверсным входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, с десятым,одиннадцатым и двенадцатым входами четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре и с восьмым и девятым входами пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, вход сумматора равно четырем второго операнда соединен с одиннадцатым и двенадцатым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, с двенадцатым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, со вторым инверсным входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре и с десятым, одиннадцатым и двенадцатым входами пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре. Изобретение относится к области вычислительной техники и микроэлектроники и может быть использовано для построения средств аппаратурного контроля и цифровых устройств, работающих в системе остаточных классов. Известен сумматор унитарных кодов по модулю пять, который со держит пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом шесть, десять входов и пять выходов 1. Недостатком известного сумматора является высокая конструктивная сложность, которая по числу входов логических элементов равна 150. Известный сумматор, как и изобретение, содержит пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с тем лишь отличием, что в заявляемом сумматоре элементы ИСКЛЮЧАЮЩЕЕ ИЛИ выполнены с порогом четыре. Наиболее близким по функциональным возможностям и конструкции техническим решением к заявляемому сумматору является сумматор унитарных кодов по модулю пять,содержащий пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, девять входов и пять выходов 2. Недостатком сумматора-прототипа является высокая конструктивная сложность, которая равна 100. Сумматор-прототип, как и заявляемый сумматор, содержит пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, выход -го, где 1, 2, 3, 4, 5, из которых соединен с выходом сумматора равно -1 результата выполнения операции сложения. 16188 1 2012.08.30 Изобретение направлено на решение технической задачи уменьшения конструктивной сложности (по числу входов логических элементов) сумматора унитарных кодов по модулю пять. Сумматор унитарных кодов по модулю пять характеризуется тем, что содержит пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, выход -го, где 1, 2 5, из которых соединен с выходом сумматора равно -1 результата сложения. Вход сумматора равно нулю первого операнда соединен с первым инверсным входом -го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, первый вход которого соединен с входом сумматора равно двум первого операнда. Вход сумматора равно трем первого операнда соединен со вторым и третьим входами -го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, четвертый, пятый и шестой входы которого соединены с входом сумматора равно четырем первого операнда. Вход сумматора равно нулю второго операнда соединен с седьмым, восьмым и девятым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, с седьмым и восьмым входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, с седьмым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре и со вторым инверсным входом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре. Вход сумматора равно единице второго операнда соединен со вторым инверсным входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, с девятым, десятым и одиннадцатым входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, с восьмым и девятым входами третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре и с седьмым входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре. Вход сумматора равно двум второго операнда соединен со вторым инверсным входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, с десятым, одиннадцатым и двенадцатым входами третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, с восьмым и девятым входами четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре и с седьмым входом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре. Вход сумматора равно трем второго операнда соединен с десятым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, со вторым инверсным входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, с десятым, одиннадцатым и двенадцатым входами четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре и с восьмым и девятым входами пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре. Вход сумматора равно четырем второго операнда соединен с одиннадцатым и двенадцатым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, с двенадцатым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре, со вторым инверсным входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре и с десятым, одиннадцатым и двенадцатым входами пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре. Основной технический результат изобретения заключается в уменьшении конструктивной сложности логической схемы сумматора, выполняющего операцию( 5) в унитарных кодах. Названный эффект достигается путем изменения соединений между элементами логической схемы сумматора. На фигуре представлена схема сумматора унитарных кодов по модулю пять. Сумматор содержит пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом четыре 15, девять входов 614 и пять выходов 1519. Сумматор предназначен для выполнения в унитарных кодах арифметической операции( 5) и работает следующим образом. На входы сумматора 69 поступают значения разрядов равно нулю, равно двум,равно трем и равно четырем унитарного двоичного кода первого операнда 3 16188 1 2012.08.30 А(а 0, а 1, а 2, а 3, а 4), на входы 1014 - значения разрядов равно нулю, равно единице,равно двум, равно трем и равно четырем унитарного двоичного кода второго операнда(0, 1, 2, 3, 4), где 0, 1, 2, 3, 40, 1 и 0, 1, 2, 3, 40, 1. Здесь 1 и 1 тогда и только тогда, когда( 5) и( 5), где 0, 1, 2, 3, 4. На выходах сумматора 1519 формируется унитарный двоичный код(0,1,2,3,4) результата выполнения операции сложения( 5), где 0, 1, 2, 3, 40, 1. При этом 1 тогда и только тогда, когда( 5), где 0, 1, 2, 3, 4. Работа сумматора унитарных кодов по модулю пять описывается таблицей истинности логических функций 0, 1, 2, 3, 4 (таблица), реализуемых на его выходах. Сумматор унитарных кодов по модулю пять Входы Выходы Унитарный двоичный код Унитарный двоичный код Унитарный двоичный код первого операнда второго операнда результата сложения(0, , 2, 3, 4)(0, 1, 2, 3, 4)(0, 1, 2, 3, 4) 0 2 3 4 0 1 2 3 4 0 1 2 3 4 6 7 8 9 10 11 12 13 14 15 16 17 18 19 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 1 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 1 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 1 0 0 0 1 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 1 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 1 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 1 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 Логическая схема сумматора унитарных кодов по модулю пять синтезирована на основе применения следующих аналитических представлений функций 0, 1, 2, 3, 4 1, если 022 33 43 0132 44 00 в противном случае,4. 20 в противном случае, 1, если 022 33 412 23 344 30 в противном случае,1, если 022 33 4022 33 44 40 в противном случае. Быстродействие сумматора, определяемое глубиной схемы, равно , где- задержка на один логический элемент. Сложность сумматора по числу входов логических элементов равна 70, а число внешних выводов равно четырнадцати. Основным достоинством заявляемого сумматора унитарных кодов по модулю пять является низкая конструктивная сложность. К дополнительным достоинствам сумматора необходимо отнести высокое быстродействие и небольшое число внешних выводов. Источники информации 1. Патент РБ 13821, МПК 067/00, 7/38, 2010. 2. Заявка на патент РБ а 20100357, МПК 067/38, 2010 (прототип). Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20. 5

МПК / Метки

МПК: G06F 7/38

Метки: пять, модулю, кодов, сумматор, унитарных

Код ссылки

<a href="https://by.patents.su/5-16188-summator-unitarnyh-kodov-po-modulyu-pyat.html" rel="bookmark" title="База патентов Беларуси">Сумматор унитарных кодов по модулю пять</a>

Предыдущий патент: Способ подготовки пробы для определения содержания фолиевой кислоты в воздухе рабочей зоны

Следующий патент: Устройство для умножения унитарных кодов по модулю пять

Случайный патент: Пищевая эмульсия типа "масло в воде"