Сумматор унитарных кодов по модулю три

Текст

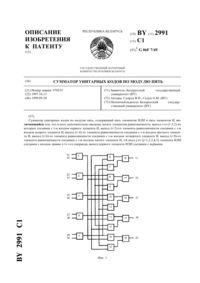

ГОСУДАРСТВЕННЫЙ ПАТЕНТНЫЙ КОМИТЕТ РЕСПУБЛИКИ БЕЛАРУСЬ СУММАТОР УНИТАРНЫХ КОДОВ ПО МОДУЛЮ ТРИ(71) Заявитель Белорусский государственный университет(73) Патентообладатель Белорусский государственный университет(57) Сумматор унитарных кодов по модулю три, содержащий три элемента ИЛИ, отличающийся тем, что в него дополнительно введены три элемента РАВНОЗНАЧНОСТЬ, -й (1, 2) вход первого из которых соединен с выходом (1)-го элемента ИЛИ, -й вход второго элемента РАВНОЗНАЧНОСТЬ соединен с выходом -го элемента ИЛИ, первый вход третьего элемента РАВНОЗНАЧНОСТЬ соединен с выходом первого элемента ИЛИ, а второй вход - с выходом третьего элемента ИЛИ, -й вход -го (1, 2, 3) элемента ИЛИ соединен со входом равно -1 -го операнда, а выход -го элемента РАВНОЗНАЧНОСТЬ соединен с выходом равно -1 сумматора. Изобретение относится к области вычислительной техники и микроэлектроники и может быть использовано для построения средств аппаратурного контроля и цифровых устройств, работающих в системе остаточных классов. Известен сумматор по модулю три двух полных двухразрядных операндов, который содержит четыре элемента И, элемент СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, два элемента РАВНОЗНАЧНОСТЬ, четыре входа и два выхода 1. Недостатком сумматора является невозможность выполнения операции сложения унитарных кодов по модулю три. 3270 1 Наиболее близким по функциональным возможностям и конструкции техническим решением к предлагаемому является сумматорунитарных кодов по модулю , который при 3 и 2 содержит девять элементов И и три элемента ИЛИ 2. Недостатком известного сумматора является высокая конструктивная сложность. Изобретение направлено на решение технической задачи понижения конструктивной сложности сумматора унитарных кодов по модулю три. Сумматор унитарных кодов по модулю три содержит три элемента ИЛИ. В отличие от прототипа в него дополнительно введены три элемента РАВНОЗНАЧНОСТЬ, -й (1,2) вход первого из которых соединен с выходом -г элемента ИЛИ, -й вход второго элемента РАВНОЗНАЧНОСТЬ соединен с выходом -го элемента ИЛИ. Первый вход третьего элемента РАВНОЗНАЧНОСТЬ соединен с выходом первого элемента ИЛИ, а второй вход - с выходом третьего элемента ИЛИ. Далее, -й вход -го (1,2,3) элемента ИЛИ соединен со входом равно -1 -го операнда, а выход -го элемента РАВНОЗНАЧНОСТЬ соединен с выходом равно -1 сумматора. Основным техническим результатом изобретения является уменьшение конструктивной сложности (по числу входов логических элементов) прототипа. Названный технический результат достигается путем введения в логическую схему сумматора новых логических элементов (элементов РАВНОЗНАЧНОСТЬ), а также изменением соединений между элементами в логической схеме. На чертеже (фиг. 1) представлена логическая схема, а посредством таблицы (фиг. 2) описывается работа сумматора унитарных кодов по модулю три. Сумматор унитарных кодов по модулю три содержит три элемента ИЛИ 1, 2 и 3, три элемента РАВНОЗНАЧНОСТЬ 4, 5 и 6, входы равно нулю 7, равно единице 9, равно двум 11 первого операнда,входы равно нулю 8, равно единице 10, равно двум 12 второго операнда, выходы равно нулю 13,равно единице 14, равно двум 15 результата сложения операндов по модулю три. Сумматор работает следующим образом. На входы 7, 9 и 11 сумматора поступает унитарный двоичный код первого операнда(а 0, а 1, а 2), на входы 8, 10 и 12 - унитарный двоичный код второго операнда В(0,1, 2), где а 0, а 1, а 2, 0, 1, 20,1. При этом а 1(1) тогда и только тогда, когда А( 3)(В( 3, где 0,1,2. На выходах 13, 14 и 15 сумматора формируется унитарный двоичный код результата сложения операндов(0, 1, 2), где 0, 1, 20,1. При этом 1 тогда и только тогда, когда( 3), где 0,1,2. Логическая схема сумматора унитарных кодов по модулю три (фиг. 1) синтезирована по следующим аналитическим представлениям логических функций 0, 1, 2 0(11)(22),1(00)(11),2(00)(22),где- обозначение логической операции равнозначность (или эквивалентность). Достоинством сумматора унитарных кодов по модулю три является простая конструкция. Так, его сложность по числу входов логических элементов равна 12, в то время как сложность прототипа (при 3 и 2) равна 27. Дополнительным достоинством сумматора является высокое быстродействие, определяемое глубиной схемы, которое совпадает с быстродействием сумматора-прототипа и составляет 2 , гдезадержка на логический элемент. Государственный патентный комитет Республики Беларусь. 220072, г. Минск, проспект Ф. Скорины, 66.

МПК / Метки

МПК: G06F 7/49

Метки: сумматор, унитарных, кодов, модулю, три

Код ссылки

<a href="https://by.patents.su/2-3270-summator-unitarnyh-kodov-po-modulyu-tri.html" rel="bookmark" title="База патентов Беларуси">Сумматор унитарных кодов по модулю три</a>

Предыдущий патент: Способ определения устойчивости асфальтобетона

Следующий патент: Способ получения спирта-ректификата из молочной сыворотки

Случайный патент: Фунгицидный состав