Сумматор по модулю три

Номер патента: 2080

Опубликовано: 30.03.1998

Авторы: Гагарин Андрей Владимирович, Зверович Игорь Эдмундович, Супрун Валерий Павлович

Текст

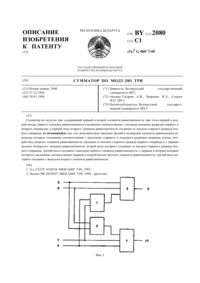

ГОСУДАРСТВЕННЫЙ ПАТЕНТНЫЙ КОМИТЕТ РЕСПУБЛИКИ БЕЛАРУСЬ СУММАТОР ПО МОДУЛЮ ТРИ(71) Заявитель Белорусский государственный университет(73) Патентообладатель Белорусский государственный университет(57) Сумматор по модулю три, содержащий первый и второй элементы равнозначности, при этом первый и второй входы первого элемента равнозначности соединены соответственно с входами младших разрядов первого и второго операндов, а первый вход второго элемента равнозначности соединен со входом старшего разряда второго операнда, отличающийся тем, что дополнительно введены третий и четвертый элементы равнозначности,выходы которых соединены соответственно с выходами старшего и младшего разрядов операнда суммы, второй вход второго элемента равнозначности соединен со входом старшего разряда первого операнда и с первым входом четвертого элемента равнозначности, второй вход которого соединен со входом старшего разряда второго операнда, третий вход соединен с выходом первого элемента равнозначности, с первым и вторым входами которого соединены соответственно первый и второй входы третьего элемента равнозначности, третий вход которого соединен с выходом второго элемента равнозначности. 2080 1 Изобретение относится к области автоматики и вычислительной техники и предназначено для построения контролепригодных арифметических устройств. Известен сумматор по модулю три, содержащий мажоритарный элемент с порогом два, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, четыре входа и два выхода 1. Недостатком сумматора по модулю три является низкая контролепригодность. Наиболее близким по конструкции и функциональным возможностям техническим решением к предлагаемому является сумматор по модулю три, содержащий два элемента равнозначности, два элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, четыре входа и два выхода 2. Недостатком известного сумматора по модулю три является низкая контролепригодность, так как для проверки константных неисправностей сумматора требуется большое количество тестовых наборов. Изобретение направлено на решение технической задачи повышения контролепригодности сумматора по модулю три. Сумматор по модулю три содержит первый и второй элементы равнозначности, при этом первый и второй входы первого элемента равнозначности соединены соответственно с входами младших разрядов первого и второго операндов, а первый вход второго элемента равнозначности соединен со входом старшего разряда второго операнда. В отличие от прототипа в сумматор дополнительно введены третий и четвертый элементы равнозначности, выходы которых соединены соответственно с выходами старшего и младшего разрядов операнда суммы. Второй вход второго элемента равнозначности соединен со входом старшего разряда первого операнда и с первым входом четвертого элемента равнозначности, второй вход которого соединен со входом старшего разряда второго операнда, третий вход соединен с выходом первого элемента равнозначности. Первый и второй входы первого элемента равнозначности соединены соответственно с первым и вторым входом третьего элемента равнозначности, третий вход которого соединен с выходом второго элемента равнозначности. Основной технический результат изобретения заключается в повышении контролепригодности логической схемы сумматора по модулю три. Названный технический результат достигается путем дополнительного введения элементов равнозначности, а также изменением межсоединений элементов в схеме сумматора. На чертеже представлена логическая схема (фиг.1), а посредством таблицы описывается работа сумматора по модулю три. Сумматор по модулю три содержит четыре элемента равнозначности 1, 2, 3 и 4, входы младших разрядов операндов 5 и 6, входы старших разрядов операндов 7 и 8, выход старшего 9 и выход младшего 10 разрядов операнда суммы. В соответствии с выбранным модулем Р 3 каждый операнд Х,иможет принимать значения 0 (00), 1(01) и 2 (10). Входные операнды сумматора Х изадаются двухразрядными двоичными кодами Хх 2 х 1 и 21,где х 1, 1 - первые (младшие) разряды операндов, а х 2, 2 - вторые (старшие) разряды операндов Х исоответственно, т.е. Х 2 х 2 х 1 и 221. Результатом работы сумматора по модулю три является операнд суммы , который задается двухразрядным двоичным кодом 21 , где 221 . Сумматор работает следующим образом. На входы 5, 6 подаются значения младших разрядов х 1, 1 операндов Х исоответственно на входы 7, 8 - значения старших разрядов х 2, 2 операндов Х исоответственно на выходах 9, 10 реализуются соответственно значения старшего 2 и младшего 1 разрядов операнда суммы , гдеХ( 3). Логические функции 1 и 2 , значения которых представлены в таблице, реализуются сумматором по модулю три согласно следующим аналитическим выражениям 1(х 2, 2, (х 1, 1 и 2(х 1, 1, (х 2, 2, где (а 1, а 2, а 3) функция равнозначности от двоичных переменных а 1, а 2, а 3 . Достоинством сумматора по модулю три является высокая контролепригодность, поскольку для проверки одиночных и кратных константных неисправностей в логической схеме сумматора достаточно четыре тестовых набора (х 1, 1, х 2, 2,)(0011), (1100), (0001), (0100). Дополнительным достоинством сумматора является низкая сложность, которая по числу входов логических элементов не превосходит конструктивную сложность устройства-прототипа и равна 10. 2080 1 СУММАТОР ПО МОДУЛЮ ТРИ ВХОДНЫЕ ОПЕРАНДЫ Х Заказ 0045 Тираж 20 экз. Государственный патентный комитет Республики Беларусь. 220072, г. Минск, проспект Ф. Скорины, 66.

МПК / Метки

МПК: G06F 7/49

Код ссылки

<a href="https://by.patents.su/3-2080-summator-po-modulyu-tri.html" rel="bookmark" title="База патентов Беларуси">Сумматор по модулю три</a>

Предыдущий патент: Электронагреватель текучих токопроводящих сред

Следующий патент: Способ восстановления дебита водозаборной скважины

Случайный патент: Способ диагностики протекающей латентно вертеброгенной вестибулярной дисфункции