Сумматор по модулю пять

Номер патента: 8122

Опубликовано: 30.06.2006

Авторы: Супрун Валерий Павлович, Терешко Сергей Михайлович, Авгуль Леонид Болеславович, Курносенко Сергей Васильевич

Текст

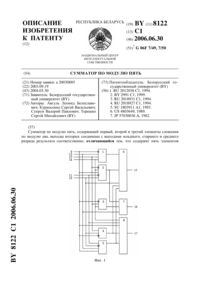

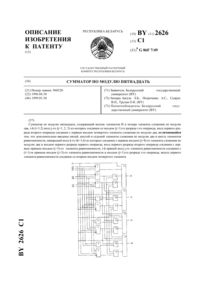

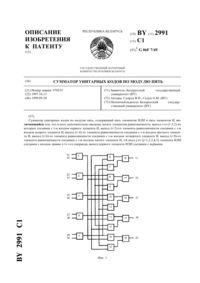

(51)06 7/49, 7/50 НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ СУММАТОР ПО МОДУЛЮ ПЯТЬ(71) Заявитель Белорусский государственный университет(72) Авторы Авгуль Леонид Болеславович Курносенко Сергей Васильевич Супрун Валерий Павлович Терешко Сергей Михайлович(73) Патентообладатель Белорусский государственный университет(57) Сумматор по модулю пять, содержащий первый, второй и третий элементы сложения по модулю два, выходы которых соединены с выходами младшего, старшего и среднего разряда результата соответственно, отличающийся тем, что содержит пять элементов 8122 1 2006.06.30 равнозначности, при этом вход старшего разряда первого операнда соединен с инверсным входом первого элемента равнозначности, первым прямым входом второго элемента равнозначности, инверсным входом третьего элемента равнозначности, инверсным входом четвертого элемента равнозначности, первым прямым входом пятого элемента равнозначности и первым входом первого элемента сложения по модулю два, выход которого выполнен инверсным, вход среднего разряда первого операнда соединен с первым прямым входом первого элемента равнозначности, первым инверсным входом второго элемента равнозначности, первым прямым входом третьего элемента равнозначности и первым прямым входом четвертого элемента равнозначности, вход младшего разряда первого операнда соединен со вторым инверсным входом второго элемента равнозначности, вторым прямым входом пятого элемента равнозначности и вторым входом первого элемента сложения по модулю два, третий вход которого соединен со входом младшего разряда второго операнда, вторым прямым входом первого элемента равнозначности, вторым прямым входом второго элемента равнозначности и вторым прямым входом третьего элемента равнозначности, а четвертый вход соединен с выходом четвертого элемента равнозначности и первым входом второго элемента сложения по модулю два, пятый вход соединен с выходом пятого элемента равнозначности и вторым входом второго элемента сложения по модулю два, третий вход которого соединен с выходом первого элемента равнозначности, а четвертый вход соединен с выходом второго элемента равнозначности и первым входом третьего элемента сложения по модулю два, второй вход которого соединен с выходом третьего элемента равнозначности, а третий вход соединен с входом среднего разряда второго операнда, третьим прямым входом первого элемента равнозначности и третьим прямым входом пятого элемента равнозначности, инверсный вход которого соединен с входом старшего разряда второго операнда, третьим прямым входом второго элемента равнозначности, вторым прямым входом четвертого элемента равнозначности и пятым входом второго элемента сложения по модулю два. Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано для построения систем аппаратурного контроля и вычислительных устройств, реализующих алгоритмы модулярной арифметики. Известен сумматор по модулю пять, содержащий четыре полусумматора, пять элементов ИЛИ-НЕ, элемент ЗАПРЕТ, элемент ИЛИ и элемент И 1. Недостатком сумматора является низкое быстродействие, определяемое большой глубиной схемы. Наиболее близким по конструкции и функциональным возможностям техническим решением к предлагаемому является сумматор по модулю пять, содержащий три элемента ЗАПРЕТ, пять элементов И, элемент ИЛИ, мажоритарный элемент с порогом три и три элемента сложения по модулю два 2. Недостатками известного сумматора по модулю пять являются высокая конструктивная сложность. Изобретение направлено на решение задачи упрощения конструкции сумматора по модулю пять. Названный технический результат достигается путем использования элементов равнозначности в схеме сумматора. Сумматор по модулю пять содержит первый, второй и третий элементы сложения по модулю два, выходы которых соединены с выходами младшего, старшего и среднего разрядов соответственно. 2 8122 1 2006.06.30 В отличие от прототипа сумматор содержит пять элементов равнозначности. В сумматоре вход старшего разряда первого операнда соединен с инверсным входом первого элемента равнозначности, первым прямым входом второго элемента равнозначности, инверсным входом третьего элемента равнозначности, инверсным входом четвертого элемента равнозначности, первым прямым входом пятого элемента равнозначности и первым входом первого элемента сложения по модулю два. Вход среднего разряда первого операнда соединен с первым прямым входом первого элемента равнозначности, первым инверсным входом второго элемента равнозначности,первым прямым входом третьего элемента равнозначности и первым прямым входом четвертого элемента равнозначности. Вход младшего разряда первого операнда соединен со вторым инверсным входом второго элемента равнозначности, вторым прямым входом пятого элемента равнозначности и вторым входом первого элемента сложения по модулю два. Третий вход первого элемента сложения по модулю два соединен со входом младшего разряда второго операнда, вторым прямым входом первого элемента равнозначности, вторым прямым входом второго элемента равнозначности и вторым прямым входом третьего элемента равнозначности. Четвертый вход первого элемента сложения по модулю два соединен с выходом четвертого элемента равнозначности и первым входом второго элемента сложения по модулю два. Пятый вход первого элемента сложения по модулю два соединен с выходом пятого элемента равнозначности и вторым входом второго элемента сложения по модулю два. Третий вход второго элемента сложения по модулю два соединен с выходом первого элемента равнозначности. Четвертый вход второго элемента сложения по модулю два соединен с выходом второго элемента равнозначности и первым входом третьего элемента сложения по модулю два. Второй вход третьего элемента сложения по модулю два соединен с выходом третьего элемента равнозначности. Третий вход третьего элемента сложения по модулю соединен с входом среднего разряда второго операнда, третьим прямым входом первого элемента равнозначности и третьим прямым входом пятого элемента равнозначности. Инверсный вход пятого элемента равнозначности соединен со входом старшего разряда второго операнда, третьим прямым входом второго элемента равнозначности,вторым прямым входом четвертого элемента равнозначности и пятым входом второго элемента сложения по модулю два. На чертеже (фиг. 1) представлена схема сумматора по модулю пять. Сумматор по модулю пять содержит пять элементов равнозначности 1-5, три элемента сложения по модулю два 6, 7 и 8, входы старшего, среднего и младшего разрядов первого операнда 9, 10 и 11 соответственно, входы старшего, среднего и младшего разрядов второго операнда 12, 13 и 14 соответственно, выходы старшего, среднего и младшего разрядов результата 15, 16 и 17 соответственно. Отметим, что первый 1 и пятый 5 элементы равнозначности имеют по одному инверсному и по три прямых входа, второй 2 элемент равнозначности имеет два инверсных и три прямых входа, третий 3 и четвертый 4 элементы равнозначности имеют по одному инверсному и по два прямых входа, а первый 8 элемент сложения по модулю два имеет инверсный выход. Сумматор выполняет сложение по модулю пять двух полных операндов5,8122 1 2006.06.30 При этом операнды ,и результаткодируются трехразрядными двоичными кодами следующим образом Десятичная цифра Сумматор по модулю пять работает следующим образом. На входы 9 и 12 подаются старшие разряды х 1 и у 1 первого и второго операндов соответственно, на входы 10 и 13 - средние разряды 2 и 2 первого и второго операндов соответственно, на входы 11 и 14 - младшие разряды х 3 и у 3 первого и второго операндов соответственно. На выходе 15 формируется старший разряд 1, на выходе 16 - средний разряд 2, а на выходе 17 - младший разряд 3 результата. Работа сумматора по модулю пять описывается приводимой ниже таблицей (фиг. 2). Как следует из таблицы, на некоторых наборах кортеж (1, 2, 3) двоичных разрядов результатаимеет вид (0,0,1) или (1,1,0). Это правомерно, поскольку на входах сумматора действуют полные операнды, и 0555. Сумматор по модулю пять построен согласно следующим соотношениям 11(1 ,2 , 1 )(1 ,3 , 1 ,2 )(1 ,2 ,2 ,3 )(1 ,2 ,3 , 1 ,3 ) 22(1 ,2 ,3 )(1 ,2 ,3 , 1 ,3 ) 3133(1 ,2 , 1 )(1 ,3 , 1 ,2 ) где(1, х 2 х)х 1 х 2 х 1 ,2- функция равнозначности. Очевидно,что(1 ,1 )1111. Достоинствами сумматора по модулю пять являются высокое быстродействие и простая конструкция. 8122 1 2006.06.30 Таблица работы сумматора по модулю пять Первый операндДесяДвоичный код тичная цифра 1/9 х 2/10 3/11 Второй операндРезультатДесяДесяДвоичный код Двоичный код тичная тичная цифра 1/12 2/13 3/14 цифра 1/15 2/16 3/17 0 1 2 3 4 5 0 1 2 3 4 5 0 1 2 3 4 5 0 1 2 3 4 5 0 1 2 3 4 5 0 1 2 3 4 5 Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20.

МПК / Метки

Код ссылки

<a href="https://by.patents.su/5-8122-summator-po-modulyu-pyat.html" rel="bookmark" title="База патентов Беларуси">Сумматор по модулю пять</a>

Предыдущий патент: Вакуумная сушилка

Следующий патент: Ветроэлектростанция

Случайный патент: Способ магнитного контроля дефектности, электрических, магнитных и механических свойств ферромагнитного материала