Устройство для вычисления пороговых аддитивно симметрических булевых функций

Номер патента: 13045

Опубликовано: 30.04.2010

Авторы: Авгуль Леонид Болеславович, Булаш Юрий Леонидович, Терешко Сергей Михайлович, Кряжев Виктор Иванович

Текст

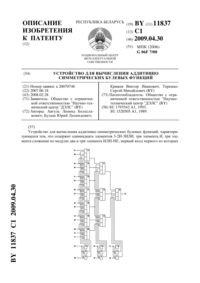

(51) МПК (2009) НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ПОРОГОВЫХ АДДИТИВНО СИММЕТРИЧЕСКИХ БУЛЕВЫХ ФУНКЦИЙ(72) Авторы Авгуль Леонид Болеславович Булаш Юрий Леонидович Кряжев Виктор Иванович Терешко Сергей Михайлович(73) Патентообладатель Общество с ограниченной ответственностью Научнотехнический центр ДЭЛС(57) Устройство для вычисления пороговых аддитивно симметрических булевых функций,содержащее элемент ИЛИ, два элемента 2-2 И-3 ИЛИ, четыре элемента 2 И-2 ИЛИ, шесть элементов ЗАПРЕТ, два элемента ИЛИ-НЕ, два элемента 2-2 И-2 ИЛИ, два элемента сложения по модулю два и девять элементов И, выход -го из которых, где 1, 4 , соединен 13045 1 2010.04.30 с -м выходом устройства, а первый вход соединен с выходом пятого элемента И и первым входом -го элемента 2-2 И-2 ИЛИ, где 1, 2, выход которого соединен с (4)-м выходом устройства, а второй вход соединен с выходом первого элемента сложения по модулю два, -й вход которого соединен с -м входом первого элемента ИЛИ-НЕ, -м входом пятого элемента И и -м входом первой группы входов устройства, -й вход второй группы входов которого соединен с -м входом второго элемента ИЛИ-НЕ, -м входом второго элемента сложения по модулю два и -м входом шестого элемента И, выход которого соединен с первым входом (6)-го элемента И, выход седьмого элемента И соединен с третьим входом первого элемента 2-2 И-2 ИЛИ и вторым входом третьего элемента И, выход восьмого элемента И соединен с третьим входом второго элемента 2-2 И-2 ИЛИ, а второй вход соединен с выходом девятого элемента И, -й вход которого соединен с -м входом третьей группы входов устройства, при этом инверсный выход -го элемента ЗАПРЕТ соединен с (6)-м выходом устройства, а прямой вход соединен с выходом первого элемента ИЛИ-НЕ и первым входом -го элемента 2-2 И-3 ИЛИ, выход которого соединен с (10)-м выходом устройства, (12)-й выход которого соединен с выходом-го элемента 2 И-2 ИЛИ, первый вход которого соединен со вторым входом -го элемента 2-2 И-3 ИЛИ и выходом пятого элемента И, второй вход соединен с третьим входом -го элемента 2-2 И-3 ИЛИ и выходом первого элемента сложения по модулю два, выход шестого элемента И соединен с первым входом (2)-го элемента 2 И-2 ИЛИ, второй вход которого соединен с выходом второго элемента сложения по модулю два, выход второго элемента ИЛИ-НЕ соединен с прямым входом (4)-го элемента ЗАПРЕТ, -й вход элемента ИЛИ соединен с -м входом третьей группы входов устройства, а выход соединен с входом запрета пятого элемента ЗАПРЕТ, третьим входом третьего элемента 2 И-2 ИЛИ и вторым входом седьмого элемента И, выход которого соединен с четвертым входом первого элемента 2-2 И-3 ИЛИ, пятый вход которого соединен с входом запрета первого элемента ЗАПРЕТ, четвертым входом первого элемента 2-2 И-2 ИЛИ и инверсным выходом пятого элемента ЗАПРЕТ, выход восьмого элемента И соединен со вторым входом четвертого элемента И и четвертым входом второго элемента 2-2 И-3 ИЛИ, пятый вход которого соединен с входом запрета второго элемента ЗАПРЕТ, четвертым входом второго элемента 2-2 И-2 ИЛИ и инверсным выходом шестого элемента ЗАПРЕТ, вход запрета которого соединен с выходом девятого элемента И и третьим входом четвертого элемента 2 И-2 ИЛИ, выход которого соединен с входом запрета четвертого элемента ЗАПРЕТ,третьим входом второго элемента 2 И-2 ИЛИ и вторым входом второго элемента И, выход третьего элемента 2 И-2 ИЛИ соединен с входом запрета третьего элемента ЗАПРЕТ,третьим входом первого элемента 2 И-2 ИЛИ и вторым входом первого элемента И. Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано для построения широкого класса цифровых устройств. Известен многопороговый логический модуль, содержащий элемент ИЛИ,элементов НЕ, -1 элементов 2 И-2 ИЛИ, -1 группу элементов 2-2 И-2 ИЛИ, управляющий вход,информационных входов и 1 выходов 1. Модуль реализует на своих выходах одновременно (в зависимости от сигнала настройки на управляющем входе) все фундаментальные или монотонные (пороговые) симметрические булевы функциипеременных. Недостатком модуля является невозможность вычисления пороговых аддитивно симметрических булевых функций. Наиболее близким по конструкции и функциональным возможностям техническим решением к предлагаемому является устройство для сложения, содержащее три элемента 13045 1 2010.04.30 сложения по модулю два, семнадцать элементов И, три элемента ИЛИ-НЕ, восемь элементов 2-2 И-2 ИЛИ, шесть входов и пятнадцать выходов 2. Устройство формирует пятнадцатиразрядный унитарный двоичный код суммы двух трехразрядных двоичных чисел, поступающих на его входы. Булевы функции, реализуемые на выходах устройства, являются фундаментальными аддитивно симметрическими и зависят от трех пар симметрических переменных. Недостатком известного устройства является невозможность вычисления пороговых аддитивно симметрических булевых функций. Изобретение направлено на решение задачи расширения функциональных возможностей устройства за счет реализации пороговых аддитивно симметрических булевых функций. Названный технический результат достигается путем использования новых логических элементов (ИЛИ, 2 И-2 ИЛИ, 2-2 И-3 ИЛИ, ЗАПРЕТ), а также изменением межсоединений элементов в схеме устройства. Устройство для вычисления пороговых аддитивно симметрических булевых функций содержит два элемента ИЛИ-НЕ, два элемента 2-2 И-2 ИЛИ, два элемента сложения по модулю два и девять элементов И, выход -го из которых, где 1, 4 , соединен с -м выходом устройства. Первый вход -го элемента И соединен с выходом пятого элемента И и первым входом-го элемента 2-2 И-2 ИЛИ, где 1, 2, выход которого соединен с (4)-м выходом устройства. Второй вход -го элемента 2-2 И-2 ИЛИ соединен с выходом первого элемента сложения по модулю два, -й вход которого соединен с -м входом первого элемента ИЛИ-НЕ,-м входом пятого элемента И и -м входом первой группы входов устройства. В устройстве -й вход второй группы входов соединен с -м входом второго элемента ИЛИ-НЕ, -м входом второго элемента сложения по модулю два и -м входом шестого элемента И, выход которого соединен с первым входом (6)-го элемента И. Выход седьмого элемента И соединен с третьим входом первого элемента 2-2 И-2 ИЛИ и вторым входом третьего элемента И. Выход восьмого элемента И соединен с третьим входом второго элемента 2-2 И-2 ИЛИ,а второй вход соединен с выходом девятого элемента И, -й вход которого соединен с -м входом третьей группы входов устройства. Устройство содержит элемент ИЛИ, два элемента 2-2 И-3 ИЛИ, четыре элемента 2 И 2 ИЛИ и шесть элементов ЗАПРЕТ, инверсный выход -го из которых соединен с (6)-м выходом устройства, а прямой вход соединен с выходом первого элемента ИЛИ-НЕ и первым входом -го элемента 2-2 И-3 ИЛИ. Выход -го элемента 2-2 И-3 ИЛИ соединен с (10)-м выходом устройства, (12)-й выход которого соединен с выходом -го элемента 2 И-2 ИЛИ, первый вход которого соединен со вторым входом -го элемента 2-2 И-3 ИЛИ и выходом пятого элемента И, второй вход соединен с третьим входом -го элемента 2-2 И-3 ИЛИ и выходом первого элемента сложения по модулю два. Выход шестого элемента И соединен с первым входом (2)-го элемента 2 И-2 ИЛИ,второй вход которого соединен с выходом второго элемента сложения по модулю два. Выход второго элемента ИЛИ-НЕ соединен с прямым входом (4)-го элемента ЗАПРЕТ, -й вход элемента ИЛИ соединен с -м входом третьей группы входов устройства, а выход соединен с входом запрета пятого элемента ЗАПРЕТ, третьим входом третьего элемента 2 И-2 ИЛИ и вторым входом седьмого элемента И. Выход седьмого элемента И соединен с четвертым входом первого элемента 2-2 И 3 ИЛИ, пятый вход которого соединен с входом запрета первого элемента ЗАПРЕТ, четвертым входом первого элемента 2-2 И-2 ИЛИ и инверсным выходом пятого элемента ЗАПРЕТ. 13045 1 2010.04.30 Выход восьмого элемента И соединен со вторым входом четвертого элемента И и четвертым входом второго элемента 2-2 И-3 ИЛИ, пятый вход которого соединен с входом запрета второго элемента ЗАПРЕТ, четвертым входом второго элемента 2-2 И-2 ИЛИ и инверсным выходом шестого элемента ЗАПРЕТ, вход запрета которого соединен с выходом девятого элемента И и третьим входом четвертого элемента 2 И-2 ИЛИ, выход которого соединен с входом запрета четвертого элемента ЗАПРЕТ, третьим входом второго элемента 2 И-2 ИЛИ и вторым входом второго элемента И. Выход третьего элемента 2 И-2 ИЛИ соединен с входом запрета третьего элемента ЗАПРЕТ, третьим входом первого элемента 2 И-2 ИЛИ и вторым входом первого элемента И. На фигуре представлена схема устройства для вычисления пороговых аддитивно симметрических булевых функций. Устройство содержит один элемент ИЛИ 1, девять элементов И 2-10, два элемента ИЛИ-НЕ 11 и 12, два элемента сложения по модулю два 13 и 14, шесть элементов ЗАПРЕТ с инверсными выходами 15-20, четыре элемента 2 И-2 ИЛИ 21-24, два элемента 2-2 И-3 ИЛИ 25 и 26, два элемента 2-2 И-2 ИЛИ 27 и 28, шесть входов 29-34 и четырнадцать выходов 35-48. На выходах устройства реализуются одновременно пороговые аддитивно симметрические булевы функции РР ,(х 1, х 2, , х 6), 114, которые определяются следующим образом 1, если 414 2232 4560, в противном случае, 114. Значения реализуемых функций на данном наборе переменных изсоставляют четырнадцатиразрядный уплотненный двоичный код, количество единиц в котором соответствует величине суммы 4 х 14 х 2232 х 4 х 56. Работа устройства поясняется таблицей. Устройство для вычисления пороговых аддитивно симметрических булевых функций(фигура) работает следующим образом. На входы первой группы 33 и 34 поступают двоичные переменные 1 и х 2 (в произвольном порядке), на входы второй группы 31 и 32 - двоичные переменные х 3 и х 4 (в произвольном порядке), на входы третьей группы 29 и 30 - двоичные переменные х 5 и х 6 (в произвольном порядке). На выходах 35, 36, , 48 формируются значения пороговых аддитивно симметрических булевых функций соответственно 11 , 22 , , 1414 на данном наборе переменных из(х 1, х 2, , х 6). Достоинствами устройства для вычисления пороговых аддитивно симметрических булевых функций являются простая конструкция, высокое быстродействие и широкая область применения. Сигналы на выходах устройства Р 5 Р 6 Р 7 Р 8 Р 9 Р 10 39 40 41 42 43 44 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 1 1 0 0 0 0 1 1 1 0 0 0 1 1 1 1 0 0 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20.

МПК / Метки

МПК: G06F 7/00

Метки: устройство, булевых, вычисления, функций, пороговых, симметрических, аддитивно

Код ссылки

<a href="https://by.patents.su/5-13045-ustrojjstvo-dlya-vychisleniya-porogovyh-additivno-simmetricheskih-bulevyh-funkcijj.html" rel="bookmark" title="База патентов Беларуси">Устройство для вычисления пороговых аддитивно симметрических булевых функций</a>

Предыдущий патент: Устройство для вычисления частично симметрических булевых функций

Следующий патент: Устройство для вычисления модулярных бисимметрических булевых функций n переменных

Случайный патент: Устройство для ухода за полостью рта