Сумматор унитарных кодов по модулю три

Номер патента: 15891

Опубликовано: 30.06.2012

Авторы: Супрун Валерий Павлович, ГОРОДЕЦКИЙ Данила Андреевич

Текст

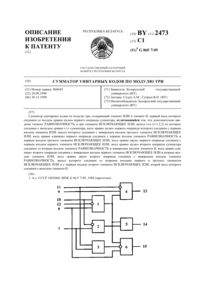

(51) МПК НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ СУММАТОР УНИТАРНЫХ КОДОВ ПО МОДУЛЮ ТРИ(71) Заявитель Белорусский государственный университет(72) Авторы Супрун Валерий Павлович Городецкий Данила Андреевич(73) Патентообладатель Белорусский государственный университет(57) Сумматор унитарных кодов по модулю три, содержащий пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, выход -го, где 1, 2, 3, из которых соединен с выходом сумматора равно 1 результата сложения, первый вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два соединен с первым и вторым входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, с первым инверсным входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с выходом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, -й, где 1, 2, вход которого соединен со входом сумматора равно нулю -го операнда и с -м инверсным входом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, выход которого соединен с первым прямым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, со вторым и третьим входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с третьим входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, четвертый вход которого соединен со входом сумматора равно двум третьего операнда, со вторым прямым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с четвертым и пятым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, шестой вход которого соединен с пятым и шестым входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, со вторым инверсным входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и со входом сумматора равно нулю третьего операнда, вход сумматора равно двум первого операнда соединен с третьим и четвертым входами четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом 15891 1 2012.06.30 два и с первым прямым входом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два,второй прямой вход которого соединен с пятым и шестым входами четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и со входом сумматора равно двум второго операнда. Изобретение относится к области вычислительной техники, автоматики и микроэлектроники и может быть использовано для построения систем передачи и переработки дискретной информации, построения систем аппаратного контроля, а также для построения вычислительных устройств, реализующих алгоритмы модулярной арифметики. Известен сумматор унитарных кодов по модулю три, содержащий три элемента ИЛИНЕ, три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, шесть элементов И, элемент СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, два элемента ИЛИ, девять входов и три выхода 1. Сумматор предназначен для реализации арифметической операции( 3). Недостатком известного сумматора является высокая конструктивная сложность (по числу входов логических элементов), равная 39. Наиболее близким по функциональным возможностям техническим решением к предлагаемому сумматору является сумматор унитарных кодов по модулю три, который содержит три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, четыре элемента ИЛИ-НЕ, три элемента И,элемент СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, элемент ИЛИ, девять входов и три выхода 2. Сумматор предназначен для реализации в унитарных кодах операции сложения( 3). Конструктивная сложность сумматора-прототипа равна 34, а его быстродействие, определяемое глубиной схемы, составляет 3, где- задержка на логический элемент. Число внешних выводов равно 12. К недостаткам сумматора-прототипа необходимо отнести следующее высокая конструктивная сложность, низкое быстродействие и большое число внешних выводов. Изобретение направлено на решение следующих технических задач понижение конструктивной сложности сумматора унитарных кодов по модулю три, повышение его быстродействия и уменьшение числа внешних выводов. Сумматор унитарных кодов по модулю три содержит пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, выход -го, где 1, 2, 3, из которых соединен с выходом сумматора равно 1 результата сложения. Первый вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два соединен с первым и вторым входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, с первым инверсным входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с выходом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, -й, где 1, 2,вход которого соединен с входом сумматора равно нулю -го операнда и с -м инверсным входом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два. Выход пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два соединен с первым прямым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, со вторым и третьим входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с третьим входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два. Четвертый вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два соединен со входом сумматора равно двум третьего операнда, со вторым прямым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с четвертым и пятым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два. Шестой вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два соединен с пятым и шестым входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два, со вторым инверсным входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и со входом сумматора равно нулю третьего операнда. 2 15891 1 2012.06.30 Вход сумматора равно двум первого операнда соединен с третьим и четвертым входами четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и с первым прямым входом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два. Второй прямой вход пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два соединен с пятым и шестым входами четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два и со входом сумматора равно двум второго операнда. Основными техническими результатами изобретения являются понижение конструктивной сложности повышение быстродействия уменьшение числа внешних выводов сумматора унитарных кодов по модулю три. Названные технические эффекты достигаются путем использования при синтезе логической схемы сумматора новых логических элементов (элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два). На фигуре представлена схема заявляемого сумматора унитарных кодов по модулю три. Сумматор унитарных кодов по модулю три содержит пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с порогом два 15, шесть входов 611 и три выхода 12, 13 и 14. Входные операнды , , С задаются унитарными двоичными кодами(0,1,2),(0, 1, 2),(0, 1, 2), где 0, 1, 2, 0, 1, 2, 0, 1, 20, 1. При этом 1,1 и 1 тогда и только тогда, когда( 3),( 3) и( 3), где 0, 1, 2. Выходной операндзадается посредством унитарного двоичного кода(0,1,2),где 0, 1, 20, 1. Здесь 1 тогда и только тогда, когда( 3), где 0, 1, 2. Сумматор унитарных кодов по модулю три предназначен для выполнения операции( 3) и работает следующим образом. На входы сумматора 6 и 9 поступают значения равно нулю и равно двум унитарного двоичного кода первого операнда(0, 1, 2), на входы 7 и 10 - значения равно нулю и равно двум унитарного двоичного кода второго операнда(0, 1, 2), на входы 8 и 11 - значения равно нулю и равно двум унитарного двоичного кода третьего операнда(0, 1, 2). На выходах сумматора 12, 13 и 14 реализуются значения равно нулю, равно единице и равно двум унитарного двоичного кода(0, 1, 2) результата выполнения арифметической операции сложения( 3). Логические функции 0, 1, 2, реализуемые на выходах заявляемого сумматора, представлены таблицей истинности (таблица). Логическая схема сумматора унитарных кодов по модулю три синтезирована на основе использования следующих аналитических представлений логических функций 0, 1, 2, зависящих от шести переменных а 0, а 2, 0, 2, с 0, с 2 1, если 2 022 022 1, если 02 202 22 100 в противном случае,0 в противном случае, 1, если 02022 20 в противном случае, где 1, если 020221, если 02 202 22 020 в противном случае,0 в противном случае. Основными достоинствами сумматора унитарных кодов по модулю три являются низкая конструктивная сложность (по числу входов логических элементов), равная 26, высокое быстродействие, равное 2, и небольшое число внешних выводов, которое равно 9 15891 1 2012.06.30 Входы Выходы Унитарный двоичУнитарный двоич- Унитарный двоичный Унитарный двоичный ный код первого опе- ный код второго опе- код третьего операнда код результата слоранда(0, 1, 2) ранда(0, 1, 2)(0, 1, 2) жения(0, 1, 2) 0 1 2 0 1 2 0 1 2 0 1 2 6 9 7 10 8 11 12 13 14 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 0 1 0 0 1 0 1 0 0 1 0 0 0 0 1 0 0 1 1 0 0 0 1 0 1 0 0 0 1 0 1 0 0 0 1 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0 1 1 0 0 1 0 0 0 0 1 1 0 0 0 0 1 1 0 0 0 0 1 0 1 0 1 0 0 1 0 0 0 0 1 0 0 1 0 1 0 0 1 0 1 0 0 1 0 0 0 1 0 0 1 0 1 0 0 0 1 0 0 0 1 0 1 0 1 0 0 0 0 1 1 0 0 0 1 0 0 1 0 1 0 0 0 0 1 0 1 0 0 1 0 0 1 0 1 0 0 0 1 0 0 1 0 0 0 1 0 1 0 0 1 0 0 0 1 1 0 0 1 0 0 0 1 0 0 0 1 0 1 0 0 1 0 0 1 0 0 0 1 0 0 1 0 0 1 0 0 1 1 0 0 1 0 0 0 0 1 0 0 1 1 0 0 0 1 0 1 0 0 0 0 1 1 0 0 0 0 1 0 1 0 0 0 1 0 1 0 1 0 0 1 0 0 0 0 1 0 1 0 0 1 0 0 1 0 0 0 1 0 1 0 0 0 1 0 0 1 0 0 1 0 0 1 1 0 0 0 1 0 0 0 1 0 0 1 0 1 0 0 0 1 0 0 1 0 0 1 0 0 1 1 0 0 Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20. 4

МПК / Метки

МПК: G06F 7/49

Метки: модулю, три, сумматор, кодов, унитарных

Код ссылки

<a href="https://by.patents.su/4-15891-summator-unitarnyh-kodov-po-modulyu-tri.html" rel="bookmark" title="База патентов Беларуси">Сумматор унитарных кодов по модулю три</a>

Предыдущий патент: Способ производства этилового спирта

Следующий патент: Способ проклейки и наполнения бумажной массы в присутствии коагулянта и катионного полиэлектролита при производстве высокозольных видов бумаги

Случайный патент: Способ подкормки поросят-сосунов