Система генерирования электрических сигналов в широком диапазоне частот

Номер патента: 9564

Опубликовано: 30.08.2007

Авторы: Беленкевич Наталья Ивановна, Романов Вячеслав Евгеньевич, Ильинков Валерий Андреевич

Текст

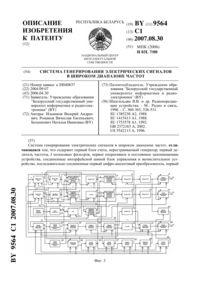

(51) МПК (2006) НАЦИОНАЛЬНЫЙ ЦЕНТР ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ СИСТЕМА ГЕНЕРИРОВАНИЯ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ В ШИРОКОМ ДИАПАЗОНЕ ЧАСТОТ(71) Заявитель Учреждение образования Белорусский государственный университет информатики и радиоэлектроники(72) Авторы Ильинков Валерий Андреевич Романов Вячеслав Евгеньевич Беленкевич Наталья Ивановна(73) Патентообладатель Учреждение образования Белорусский государственный университет информатики и радиоэлектроники(57) Система генерирования электрических сигналов в широком диапазоне частот, отличающаяся тем, что содержит первый блок счета, перестраиваемый генератор, первый делитель частоты,полосовых фильтров, первое оперативное и постоянное запоминающие устройства, соединенные интерфейсной шиной блок управления и вычислительное устройство, последовательно соединенные первый цифро-аналоговый преобразователь, первый 9564 1 2007.08.30 фильтр нижних частот и первый регулируемый усилитель, последовательно соединенные первый балансный модулятор и первый аналоговый коммутатор и последовательно соединенные второй аналоговый коммутатор и второй регулируемый усилитель, причем блок управления своимивыходами данных соединен с соответствующими двунаправленными выводами данных постоянного запоминающего устройства и соответствующими входами данных первого блока счета, перестраиваемого генератора, первого делителя частоты, первого и второго аналоговых коммутаторов, первого и второго регулируемых усилителей, а своимивыходами управления - с соответствующими входами управления первого блока счета, первого оперативного и постоянного запоминающих устройств, первого и второго аналоговых коммутаторов, первого и второго регулируемых усилителей,первого делителя частоты и перестраиваемого генератора, первый делитель частоты счетным входом соединен со входом синхронизации первого цифро-аналогового преобразователя и счетным входом первого блока счета, а выходом - со входом установки последнего,каждый изполосовых фильтров включен между соответствующим изканальных выходов первого и соответствующим изканальных входов второго аналоговых коммутаторов,выходов данных первого блока счета соединены с соответствующими входами адреса постоянного запоминающего устройства, а выходы первого и второго регулируемых усилителей соединены соответственно с первым и вторым выходами системы второй, третий и четвертый блоки счета,цифровых -разрядных коммутаторов двух каналов в один канал, (-1) оперативных запоминающих устройств, первый и второй цифровые -разрядные коммутаторыканалов в один канал, цифровой -разрядный коммутатор одного канала вканалов, второй цифро-аналоговый преобразователь, второй фильтр нижних частот, третий регулируемый усилитель, второй балансный модулятор, третий и четвертый аналоговые коммутаторы, первый и второй фильтры промежуточной частоты,второй, третий, четвертый и пятый делители частоты, при этом блок управления своимидвунаправленными выводами данных соединен с соответствующими входами данных второго, третьего и четвертого блоков счета, третьего и четвертого аналоговых коммутаторов, третьего регулируемого усилителя, цифрового -разрядного коммутатора одного канала вканалов, второго, третьего, четвертого и пятого делителей частоты, а своимивыходами управления - с соответствующими входами управления второго, третьего и четвертого блоков счета, третьего регулируемого усилителя, третьего и четвертого аналоговых коммутаторов, цифрового -разрядного коммутатора одного канала вканалов, (-1) оперативных запоминающих устройств, второго, третьего, четвертого и пятого делителей частоты, выходы переноса первого и третьего блоков счета соединены соответственно со счетными входами второго и четвертого блоков счета,выходов данных второго блока счета соединены с соответствующими входами установки первого цифрового разрядного коммутатораканалов в один канал и с соответствующими извходов первой группы входов установки каждого изцифровых -разрядных коммутаторов двух каналов в один канал,выходов данных четвертого блока счета соединены с соответствующими входами установки цифрового -разрядного коммутатора одного канала вканалов,второго цифрового -разрядного коммутатораканалов в один канал и с соответствующими извходов второй группы входов установки каждого изцифровых -разрядных коммутаторов двух каналов в один канал,выходов данных первого ивыходов данных третьего блоков счета соединены со входами соответственно первого и второго каналов каждого изцифровых -разрядных коммутаторов двух каналов в один канал, выходы каждого изцифровых -разрядных коммутаторов двух каналов в один канал соединены со входами адреса соответствующих изоперативных запоминающих устройств, выходы каждого из каналов цифрового -разрядного коммутатора одного канала вканалов соединены с двунаправленными выводами данных, соответствующих изоперативных запоминающих устройств и входами соответствующих каналов первого и второго цифровых -разрядных коммутаторовканалов в один канал, выходы которых соединены со 2 9564 1 2007.08.30 входами данных соответственно первого и второго цифро-аналоговых преобразователей,второй фильтр нижних частот включен между выходом второго цифро-аналогового преобразователя и сигнальным входом третьего регулируемого усилителя, соединенного выходом с третьим выходом системы, модулирующий, опорный входы и выход второго балансного модулятора соединены соответственно с выходом первого фильтра нижних частот, выходом пятого делителя частоты и входом третьего аналогового коммутатора,первый и второй выходы которого соответственно через первый и второй фильтры промежуточной частоты соединены соответственно с первым и вторым входами четвертого аналогового коммутатора, модулирующий и опорный входы первого балансного модулятора соединены соответственно с выходом четвертого аналогового коммутатора и выходом четвертого делителя частоты, счетный вход которого соединен со счетным входом пятого делителя частоты, первым выходом перестраиваемого генератора и счетным входом второго делителя частоты, соединенного выходом со счетным входом первого делителя частоты, второй выход перестраиваемого генератора соединен со счетным входом третьего блока счета, входом синхронизации второго цифро-аналогового преобразователя и счетным входом третьего делителя частоты, соединенного выходом со входом установки третьего блока счета. Важной для радиоэлектроники, телекоммуникаций и измерительной техники является проблема генерирования электрических сигналов различной формы и разных видов модуляции в широком диапазоне несущих частот. На практике она решается с помощью известной системы генерирования электрических сигналов 1. В известной системе формирование относительно низкочастотных сигналов осуществляется методом цифрового синтеза отсчетных значений с последующим их цифроаналоговым преобразованием в полезный сигнал ВЫХ 1. Формирование высокочастотных модулированных сигналов ВЫХ 2 выполняется модуляцией сигналом ВЫХ 1 по тому или (и) иному параметру колебания неизменной промежуточной частоты и последующим переносом на несущую частоту с помощью опорного колебания с изменяемой(перестраиваемой) частотой. Известная система генерирования электрических сигналов позволяет генерировать немодулированные и модулированные электрические сигналы в широком диапазоне частот. Однако она обладает следующими существенными недостатками обеспечивает недостаточную для многих применений стабильность несущей частоты модулированных сигналов имеет ограниченные функциональные возможности. Для устранения отмеченных существенных недостатков известной системы предлагается следующая система генерирования электрических сигналов в широком диапазоне частот. Задача изобретения - расширение функциональных возможностей и повышение стабильности несущей частоты генерируемых модулированных сигналов. Система генерирования электрических сигналов в широком диапазоне частот, отличающаяся тем, что содержит первый блок счета, перестраиваемый генератор, первый делитель частоты,полосовых фильтров, первое оперативное и постоянное запоминающие устройства, соединенные интерфейсной шиной блок управления и вычислительное устройство, последовательно соединенные первый цифро-аналоговый преобразователь, первый фильтр нижних частот и первый регулируемый усилитель, последовательно соединенные первый балансный модулятор и первый аналоговый коммутатор и последовательно соединенные второй аналоговый коммутатор и второй регулируемый усилитель, причем блок управления своимивыходами данных соединен с соответствующими двунаправленными выводами данных постоянного запоминающего устройства и соответствующими входами данных первого блока счета, перестраиваемого генератора, первого делителя частоты, первого и второго аналоговых коммутаторов, первого и второго регулируемых уси 3 9564 1 2007.08.30 лителей, а своимивыходами управления - с соответствующими входами управления первого блока счета, первого оперативного и постоянного запоминающих устройств, первого и второго аналоговых коммутаторов, первого и второго регулируемых усилителей,первого делителя частоты и перестраиваемого генератора, первый делитель частоты счетным входом соединен со входом синхронизации первого цифро-аналогового преобразователя и счетным входом первого блока счета, а выходом - со входом установки последнего,каждый изполосовых фильтров включен между соответствующим изканальных выходов первого и соответствующим изканальных входов второго аналоговых коммутаторов,выходов данных первого блока счета соединены с соответствующими входами адреса постоянного запоминающего устройства, а выходы первого и второго регулируемых усилителей соединены соответственно с первым и вторым выходами системы второй, третий и четвертый блоки счета,цифровых -разрядных коммутаторов двух каналов в один канал, (-1) оперативных запоминающих устройств, первый и второй цифровые -разрядные коммутаторыканалов в один канал, цифровой -разрядный коммутатор одного канала вканалов, второй цифро-аналоговый преобразователь, второй фильтр нижних частот, третий регулируемый усилитель, второй балансный модулятор, третий и четвертый аналоговые коммутаторы, первый и второй фильтры промежуточной частоты,второй, третий, четвертый и пятый делители частоты, при этом блок управления своимидвунаправленными выводами данных соединен с соответствующими входами данных второго, третьего и четвертого блоков счета, третьего и четвертого аналоговых коммутаторов, третьего регулируемого усилителя, цифрового -разрядного коммутатора одного канала вканалов, второго, третьего, четвертого и пятого делителей частоты, а своимивыходами управления - с соответствующими входами управления второго, третьего и четвертого блоков счета, третьего регулируемого усилителя, третьего и четвертого аналоговых коммутаторов, цифрового -разрядного коммутатора одного канала вканалов, (-1) оперативных запоминающих устройств, второго, третьего, четвертого и пятого делителей частоты, выходы переноса первого и третьего блоков счета соединены соответственно со счетными входами второго и четвертого блоков счета,выходов данных второго блока счета соединены с соответствующими входами установки первого цифрового -разрядного коммутатораканалов в один канал и соответствующими извходов первой группы входов установки каждого изцифровых -разрядных коммутаторов двух каналов в один канал,выходов данных четвертого блока счета соединены с соответствующими входами установки цифрового -разрядного коммутатора одного канала вканалов, второго цифрового -разрядного коммутатораканалов в один канал и с соответствующими извходов второй группы входов установки каждого изцифровых -разрядных коммутаторов двух каналов в один канал,выходов данных первого ивыходов данных третьего блоков счета соединены со входами соответственно первого и второго каналов каждого изцифровых -разрядных коммутаторов двух каналов в один канал, выходы каждого изцифровых -разрядных коммутаторов двух каналов в один канал соединены со входами адреса соответствующих изоперативных запоминающих устройств, выходы каждого из каналов цифрового -разрядного коммутатора одного канала вканалов соединены с двунаправленными выводами данных соответствующих изоперативных запоминающих устройств и входами соответствующих каналов первого и второго цифровых разрядных коммутаторовканалов в один канал, выходы которых соединены со входами данных соответственно первого и второго цифро-аналоговых преобразователей, второй фильтр нижних частот включен между выходом второго цифро-аналогового преобразователя и сигнальным входом третьего регулируемого усилителя, соединенного выходом с третьим выходом системы, модулирующий, опорный входы и выход второго балансного модулятора соединены соответственно с выходом первого фильтра нижних частот, выходом пятого делителя частоты и входом третьего аналогового коммутатора, первый и второй выходы которого соответственно через первый и второй фильтры промежуточной частоты соединены соответственно с первым и вторым входами четвертого аналогового 4 9564 1 2007.08.30 коммутатора, модулирующий и опорный входы первого балансного модулятора соединены соответственно с выходом четвертого аналогового коммутатора и выходом четвертого делителя частоты, счетный вход которого соединен со счетным входом пятого делителя частоты, первым выходом перестраиваемого генератора и счетным входом второго делителя частоты, соединенного выходом со счетным входом первого делителя частоты, второй выход перестраиваемого генератора соединен со счетным входом третьего блока счета,входом синхронизации второго цифро-аналогового преобразователя и счетным входом третьего делителя частоты, соединенного выходом со входом установки третьего блока счета. На фиг. 1 приведен синтезируемый аналоговый сигнал, на фиг. 2 - модулированный сигнал вспомогательной промежуточной частоты, на фиг. 3 - структурная схема предлагаемой системы генерирования, на фиг. 4 - спектры мощностей сигналов и АЧХ функциональных звеньев, поясняющие работу предлагаемой системы. Структурная схема предлагаемой системы генерирования содержит в себе (фиг. 3) первый 1, второй 2, третий 9 и четвертый 10 блоки счета, первый 31, второй 32 -ый 3 цифровые -разрядные коммутаторы двух каналов в один канал, первое 41, второе 42-ое 4 ОЗУ, первый 5 и второй 11 цифровые -разрядные коммутаторыканалов в один канал, первый 6 и второй 12 ЦАП, первый 7 и второй 13 ФНЧ, первый 8, второй 28 и третий 14 регулируемые усилители, вычислительное устройство 15, блок 16 управления, ПЗУ 17, цифровой -разрядный коммутатор 18 одного канала вканалов, первый 191, второй 192 -ый 19 ПФ, первый 25 и второй 20 балансные модуляторы, первый 26, второй 27,третий 21 и четвертый 24 аналоговые коммутаторы, первый 22 и второй 23 фильтры промежуточной частоты, перестраиваемый генератор 29, первый 32, второй 30, третий 31,четвертый 33 и пятый 34 делители частоты. Как и в известной системе, в предлагаемой системе генерирования вычислительное устройство 15 связано с блоком 16 управления интерфейсной шиной, представляющей совокупность трех информационных шин двунаправленной шины данных, шины управления и шины сигналов состояния. С помощью сигналов шины управления и шины сигналов состояния по шине данных из вычислительного устройства в блок управления и (через него) в другие функциональные блоки (в прямом направлении), а также из блока управления в вычислительное устройство (в обратном направлении) передаются необходимые данные. Блок 16 управления, помимо интерфейсной шины, связывающей его с вычислительным устройством 15, имеет еще две информационные шины -разрядную шину управления и-разрядную шину данных (см. фиг. 3). С помощью сигналов шины управления по шине данных из него в блоки 1, 2, 8-10, 14, 17, 21, 24, 26-34 заносятся необходимые числовые данные. Для их приема и хранения каждый из перечисленных функциональных блоков имеет в своем составе параллельный регистр. Дополнительно блок 16 управления содержит полноценные поле набора, поле индикации, другие необходимые блоки, что при выполнении системы по варианту с отдельным модулем генерирования сигналов обеспечивает возможность ее работы в автономном режиме. Первый блок 1 счета построен на основе -разрядного двоичного счетчика с максимальным коэффициентом счета К 2 и -разрядного параллельного регистра. Он является формирователем адресов данных, считываемых из ОЗУ 41-4 и ПЗУ 17 либо записываемых в эти устройства. Под действием непрерывной последовательности тактовых (счетных) импульсов, подаваемых на счетный вход блока счета, числовое значение,вырабатываемое в двоичном коде на еговыходах данных, циклически изменяется, последовательно принимая в каждом циклесоседних значений числовой последовательности 0,1,22-1,0,12-1,0,1, (в цикле число с номером 1 имеет значение М 1, число с номером- значение ). Значение М 1 можно устанавливать произвольно из условия 012-1, что обеспечивается занесением (через входы данных) в упомянутый параллельный регистр блока счета числового значения М 1. В конце каждого цикла двоичный счетчик импульсами установки, подаваемыми на вход установки блока счета, принуди 5 9564 1 2007.08.30 тельно переводится из состояния с числовым значениемв состояние со значением М 1. Длина цикла(12) является варьируемой и определяется отношением частот повторений тактовых импульсов и импульсов установки. При каждом переходе двоичного счетчика из состоянияв состояние М 1 на выходе переноса блока 1 счета вырабатывается короткий импульс переноса, подаваемый на счетный вход второго блока 2 счета. Третий 9 блок счета является формирователем адресов данных, считываемых из (записываемых в) ОЗУ 41-4. Его построение и функционирование такие же, как первого 1 блока счета. Второй 2 и четвертый 10 блоки счета предназначены для управления цифровыми коммутаторами 31-3, 5, 11 и 18. Каждый из блоков 2 и 10, реализованный на основе -разрядного двоичного счетчика с максимальным коэффициентом счета 2, работает в трех режимах записи и хранения циклического счета нейтральном. Выбор режима осуществляется сигналами управления, подаваемыми на ихвходов управления. В режиме циклического счета под действием непрерывной последовательности импульсов переноса, подаваемых на счетный вход блока 2 (10), числовое значение на еговыходах данных циклически изменяется (через единицу) в пределах от 0 до 2-1. В режиме записи и хранения в блок счета 2(10) записывается (через входы данных), хранится и присутствует на выходах данных числовое значение 2 (10). При этом 02(10)2-1,210, т.е. одновременное наличие одинаковых значений на выходах блоков 2 и 10 - невозможное состояние. В нейтральном режиме (в так называемом третьем состоянии) обеспечивается высокое значение выходного сопротивления на всех выходах данных, что эквивалентно их отключению. Каждый из 31-3 цифровых коммутаторов имеетвходов первого ивходов второго каналов, соединенных с выходами данных соответственно первого 1 и третьего 9 блоков счета, а такжевходов первой ивходов второй групп входов установки, которые подключены к выходам данных соответственно второго 2 и четвертого 10 блоков счета. При этом коммутатор 3(1) пропускает на свои выходы цифровые данные со входов первого (второго) каналов только тогда, когда навходах первой (второй) группы его входов установки присутствует числовое значение (в двоичном коде), равное (-1). Цифровой -разрядный коммутатор 18 одного канала вканалов содержитвходов данных, входов управления,входов установки,-разрядных канальных выходов и работает в двух режимах коммутации нейтральном. В режиме коммутации он передает входные данные на выходы -го канала, если на входы установки подан двоичный код, соответствующий значению (-1). В нейтральном режиме цифровые данные через коммутатор не проходят и на всех его выходах реализуется высокое значение выходного сопротивления,что обеспечивает нормальное функционирование ОЗУ. Выбор режима осуществляется сигналами управления, подаваемыми навходов управления коммутатора 18. Первый 5 и второй 11 цифровые -разрядные коммутаторыканалов в один канал имеютразрядных канальных входов,входов установки ивыходов. В любой момент времени через коммутатор 5(11) проходят данные с одного изканальных входов, например с требуемого -го (1), для чего на входы установки необходимо подать в двоичном коде числовое значение (-1) (см. фиг. 3). ПЗУ 17 своимидвунаправленными выводами данных,входами управления ивходами адреса подключено к соответствующим выводам шины данных и шины управления блока 16 управления и выходам данных блока 1 счета. Оно имеет максимальный размер адресного пространства и максимальный объем памяти соответственно 2 адресов и(2) бит, что обеспечивает одновременное хранение отсчетных значений нескольких сигналов. Выбор необходимой области памяти для записи (считывания) отсчетных значений конкретного сигнала достигается занесением в параллельный регистр блока 1 счета адреса М 1 и заданием длиныцикла. ПЗУ 17 работает в трех режимах записи считывания нейтральном (в третьем состоянии). В предлагаемой системе ОЗУ выполнено в видесамостоятельных устройств (ОЗУ 41-4) с независимым друг от друга доступом к ячейкам памяти, что необходимо при одновремен 6 9564 1 2007.08.30 ном формировании двух смещенных по времени (фазе) сигналов 1 и 1(-). Каждое из ОЗУ 41-4 посредством блоков 2, 10 и 31-3 может подключаться к обоим формирователям адресов - блокам 1 и 9 счета - и иметь такие же, как и ПЗУ 17, максимальный размер адресного пространства и максимальный объем памяти. При использовании последнего суммарный максимальный объем памяти всех ОЗУ превысит максимальный объем памяти ПЗУ 17 враз, что соответствует лишь частичной (на 100/ ) загрузке ОЗУ в автономном режиме работы системы генерирования. Поэтому целесообразно общее количествоОЗУ,а также максимальный размер адресного пространства и максимальный объем памяти каждого из них выбирать соответственно равными 2, 2- и (2-). Тогда суммарный максимальный объем памяти всех ОЗУ 41-4 будет равен максимальному объему памяти ПЗУ 17, а при доступе к ячейкам памяти ОЗУ на выходах первого 1 и третьего 9 блоков счета будут изменяться состояния только младших (-) разрядов. ОЗУ, как и ПЗУ, работает в трех режимах записи считывания нейтральном. Первый 8, второй 28 и третий 14 регулируемые усилители выполняют функцию усиления и регулирования уровня. Для установки требуемых уровней выходных сигналов в их -разрядные параллельные регистры из вычислительного устройства 15 (блока управления 16) по шине данных с помощью сигналов шины управления заносятся соответствующие числовые значения. Первый аналоговый коммутатор 26 представляет собой устройство, коммутирующее входной сигнал на требуемый -й (1) канальный выход, а второй аналоговый коммутатор 27 - устройство, передающее на свой выход сигнал с -го канального входа. Третий 21 и четвертый 24 аналоговые коммутаторы, являясь двухканальными, выполняют функции, аналогичные соответственно коммутаторам 26 и 27. Перестраиваемый генератор 29 представляет собой синтезатор стабильных колебаний в широком диапазоне частот, построенный на основе управляемого напряжением генератора, генератора опорного колебания, фазового детектора и четырех делителей частоты с переменными коэффициентами деления. Он формирует на своих первом и втором выходах стабильные колебания на частотах соответственно 1 и 2. Эти частоты, благодаря такой структуре синтезатора, могут быть одинаковыми (12), кратными (отличаться в целое количество раз) либо некратными. Выбор требуемых значений частот колебаний на выходах перестраиваемого генератора 29 обеспечивается занесением с помощью сигналов шины управления по шине данных необходимых значений коэффициентов деления упомянутых четырех делителей частоты, входящих в перестраиваемый генератор. Предлагаемая система генерирования электрических сигналов имеет два режима работы режим записи режим генерирования. В режиме записи вычислительное устройство 15 вычисляет-разрядных значений цифрового сигнала Ц, соответствующих отсчетным значениямсинтезируемого аналогового сигналана Р периодахего повторения (фиг. 1). С помощью сигналов шины управления по шине данных из вычислительного устройства 15 через блок управления 16 передается и записывается в параллельный регистр первого 1 блока счета значение М 1 - граничное значение адресов области памяти ПЗУ 17, отводимой для хранения цифровых данных сигнала Ц. Далее сигналами управления ПЗУ переводится в режим записи, после чего с помощью серии изтактовых импульсов и других управляющих сигналов, подаваемых по шине управления в первый блок счета, в ПЗУ 17 записываются-разрядных значений цифрового сигнала Ц. В процессе записи числовое значение навыходах данных блока 1 счета последовательно принимаетсоседних значений в пределах от М 1 до . На каждом -м изтактов записи оно задает адрес группы изячеек памяти, в которые на этом же такте записывается соответствующее -разрядное значение сигнала Ц, подаваемое из вычислительного устройства 15 по шине данных на двунаправленные выводы ПЗУ 17. Аналогично осуществляется запись цифровых данных остальных сигналов , выбирая для каждого из них свое адресное значение М 1 и (при необходимости) свое значение . После ее выполнения ПЗУ 17, а также блоки 2 и 10 счета, ОЗУ 41-4 и цифровой коммутатор 18 переводятся в нейтральный режим. Режим записи всей системы генерирования заканчивается. 7 9564 1 2007.08.30 В режиме генерирования вначале сигналами шины управления блок 10 счета переводится в режим записи и хранения, коммутатор 18 - в режим коммутации, ОЗУ 4 (например, первое 41) - в режим записи, а ПЗУ 17 - в режим считывания информации. С помощью сигналов шины управления в параллельные регистры первого 1, третьего 9 и четвертого 10 блоков счета записываются значения соответственно М 1 ПЗУ - граничное значение адресов области памяти ПЗУ 17, где хранятся цифровые данные выбранного сигнала 1, М 1 ОЗУ - граничное значение адресов области памяти ОЗУ 4, отводимой для хранения считываемых из ПЗУ данных, и 10 - адресное значение ОЗУ 4, при котором коммутатор 3 пропускает на свои выходы цифровые данные со входов второго канала, подключая тем самымвыходов данных блока 9 счета ко входам адреса ОЗУ 4, а коммутатор 18 передает входные данные на выходы -го канала (соединяет двунаправленные выводы данных ПЗУ 17 и соответствующие двунаправленные выводы данных выбранного ОЗУ 4). Далее с помощью серии изтактовых импульсов и других управляющих сигналов, подаваемых по шине управления в блоки 1, 4, 9 и 17, в ОЗУ 4 (из ПЗУ 17) записываются-разрядных цифровых данных сигнала 1. В процессе записи числовое значение на выходах данных первого 1 блока счета последовательно принимаетсоседних значений в пределах от М 1 ПЗУ до МПЗУ, а значение на выходах данных третьего 9 блока счета - в пределах от М 1 ОЗУ до МОЗУ. На каждом -м изтактов записи они задают соответственно адрес группы изячеек памяти ПЗУ, из которых считывается -разрядное значение сигнала 1 и адрес группы изячеек памяти ОЗУ, в которые это значение,поступая через коммутатор 18, записывается. Предлагаемая система обеспечивает возможность одновременного формирования прямым цифровым синтезом двух сигналов 1 и 2. В случае такой необходимости в описанной последовательности выполняется запись в ОЗУ 4 (1,) цифровых данных второго сигнала 2, задавая для него свои адресные значения М 1 ПЗУ, М 1 ОЗУ, 0 и свою длину цикла . После записи данных в ОЗУ сигналами шины управления ПЗУ 17 и коммутатор 18 переводятся в нейтральный режим, ОЗУ 4 и 4 - в режим считывания, блок 2 счета - в режим записи и хранения (блок 10 находится в этом режиме). Для определенности предположим, что первый 1 из синтезируемых сигналов формируется на первом, а второй 2 - на третьем выходах предлагаемой системы (можно наоборот 1 - на третьем, 2 - на первом). В соответствии с этим сигналами управления по шине данных в блоки 2 и 1 счета записываются соответственно адресное значение 2 ОЗУ 4 и граничное значение М 1 ОЗУ адресов его области памяти, где хранятся цифровые данные сигнала 1, в блоки 10 и 9 счета - соответственно адресное значение ОЗУ 4 и граничное значение адресов его области памяти, где хранятся цифровые данные сигнала 2, в перестраиваемый генератор 29 и делители 30-32 частоты - данные, устанавливающие необходимые при формировании сигналов 1 и 2 значения тактовых частот 1, 2 и длин циклов 1 и 2, после чего блоки 1 и 9 счета переводятся в режим непрерывного(циклического) счета тактовых импульсов, поступающих на их счетные входы. Делением частоты колебаний с первого выхода перестраиваемого генератора 29 образуется непрерывная последовательность импульсов, поступающих с тактовой частотойна счетный вход блока 1 счета. На вход установки последнего с выхода первого 32 делителя частоты подаются импульсы установки, следующие с частотой 1/1 (тактовая частота Т 1// выбирается с запасом по условию(2,5-3,0), где Р,целые числа,- верхняя граничная частота спектра сигнала (. В результате из ОЗУ 4 циклически считываются -разрядные значения цифрового сигнала Ц 1, соответствующие отсчетным значениям 1 аналогового сигнала 1 на Р 1 периодах ТМ 1 его повторения. Они проходят через цифровой коммутатор 5 и с помощью ЦАП 6, управляемого по входу синхронизации тактовыми импульсами, и ФНЧ 7 с АЧХпреобразуются в аналоговый сигнал 1 с амплитудным спектром(см. фиг. 1). Этот сигнал в усилителе 8 усиливается и регулируется (нормируется) по уровню, тем самым превращаясь в 8 9564 1 2007.08.30 сигнал ВЫХ 1 на первом выходе системы генерирования. Аналогично, под действием тактовых импульсов с частотой Т 2 и импульсов установки с частотой 2/2, снимаемых со второго выхода генератора 29 и выхода третьего 31 делителя частоты и подаваемых соответственно на счетный вход и вход установки третьего 9 блока счета, из ОЗУ 4 циклически считываются -разрядные значения цифрового сигнала Ц 2, преобразуемые ЦАП 12 и ФНЧ 13 в аналоговый сигнал 2, который после усиления и регулирования (в усилителе 14) превращается в сигнал ВЫХ 3 на третьем выходе системы. Как показано выше, генератор 29 может формировать на своих выходах колебания кратных и некратных частот, что обеспечивает возможность одновременного синтеза двух сигналов ВЫХ 1 и ВЫХ 3 различной формы и разных (в общем случае некратных) периодов(частот) повторения. Предлагаемая система обеспечивает возможность одновременного формирования двух одинаковых сдвинутых по времени (фазе) сигналов 1 и 21(-). Для реализации этой возможности количество 1 -разрядных значений цифрового сигнала Ц 1, соответствующих отсчетным значениям 1 синтезируемого аналогового сигнала 1 напериодах ТМ его повторения, обязательно выбирается кратной количеству 2 используемых ОЗУ 41-4. Запись цифровых данных сигнала Ц 1 в ПЗУ 17 выполняется в описанной выше последовательности, а запись в ОЗУ - по-другому. Для ее осуществления 1 -разрядных значений условно разбиваются нагрупп по /2 значений в каждой группе (соответствующих 1/2 соседним отсчетным значениям сигнала 1(. Каждая группа данных записывается в соответствующее ей по номеру ОЗУ, причем во всех ОЗУ 41-4 запись происходит по одинаковым адресам (последовательность операций при записи данных в конкретное ОЗУ описана выше). После записи данных в ОЗУ сигналами шины управления ПЗУ 17 и коммутатор 18 переводятся в нейтральный режим, ОЗУ 41-4 - в режим считывания, блоки 2 и 10 - в режим записи и хранения. Сигналами управления по шине данных в блоки 2 и 10 счета записываются числовые значения соответственно 2 и 0 (как показано выше, 20 и 02(10)2-1), определяющие величинузапаздывания (опережения) сигнала 21(-) относительно сигнала 1. В предлагаемой системе абсолютная величина смещения 210/ 2 является изменяемой с шагом /2 в пределах от /2 до (2-1)/2. Далее сигналами управления по шине данных в блоки 1 и 9 счета записывается граничное значение М 1 ОЗУ адресов области памяти ОЗУ 41-4, где хранятся цифровые данные сигнала 1, в перестраиваемый генератор 29 - данные, устанавливающие (необходимые) одинаковые значения частот колебаний (1) на первом и втором выходах, в делители 30, 31 и 32 частоты - значения коэффициентов деления, равные соответственно 1, 1/2 и 1/2, после чего блоки 1, 2, 9 и 10 счета переводятся в режим непрерывного (циклического) счета тактовых импульсов,поступающих на их счетные входы. В результате первый 1 и третий 9 блоки счета синхронно формируют с тактовой частотой в двоичном коде на своихвыходах данных одинаковые совпадающие по времени числовые последовательности, принимающие в каждом цикле 1/2 соседних значений последовательности 0,1,22-1,0,1,22-1,(начиная со значения М 1 ОЗУ). По окончании каждого цикла на счетные входы второго 2 и четвертого 10 блоков счета синхронно с частотой 1/2 поступают импульсы переноса,под действием которых блоки 2 и 10 вырабатывают на своих выходах (с учетом предварительной записи в них значений 2 и 10) в -разрядном двоичном коде циклически изменяющиеся (через единицу) в пределах от 0 до 2-1 числовые последовательности,сдвинутые друг относительно друга на 2-0 позиций. Тем самым обеспечивается циклическое подключение блоков 1 и 9 счета - формирователей адресов - к каждому из ОЗУ 41-4 и одновременный доступ к двум (разным) ОЗУ, данные с которых через синхронно переключаемые коммутаторы 5 и 11 попадают на входы соответственно первого 6 и второго 12 ЦАП. Последние вместе с ФНЧ 7 и 13 преобразуют их в сигналы 1 и 1(-),9 9564 1 2007.08.30 превращающиеся после усиления и регулирования в сигналы ВЫХ 1 и ВЫХ 3 на первом и третьем выходах системы генерирования (см. фиг. 3). Сигналы ВЫХ 1 и ВЫХ 3, формируемые на первом и третьем выходах предлагаемой системы генерирования, образуются методом прямого цифрового синтеза. Максимальная верхняя граничная частотаих амплитудного спектра в основном определяется быстродействием ОЗУ 41-4 и на современном этапе составляет 50-70 МГц. Это обеспечивает возможность синтеза смодулированных сигналов различной формы, а также (относительно низкочастотных) модулированных сигналов с несущей частотой ,не превышающей значения . Предлагаемая система генерирования позволяет формировать также высокочастотные модулированные сигналы с несущей частотойв диапазоне . Для достижения этого в описанной выше последовательности вычисляются и записываются в ОЗУ 4 разрядных значений цифрового сигнала Ц, соответствующих отсчетным значениям ВПМ модулированного (периодическим сигналомс периодом повторения ТМ и амплитудным спектром ( по тому или (и) иному параметру сигнала ВПМ вспомо гательной промежуточной частотыВП , выбираемой из условияВП, на интервале времени 3/ВП (,целые числа). Генератор 29 вырабатывает на первом вы ходе колебание Г с перестраиваемой в диапазоне 0,5 частотойГ . Делением в , ицелое количество раз (делители соответственно 34, 33 и 30) частоты колебания Г образуются соответственно вспомогательное опорное колебание , опорное колебаниеи колебаниетактовой частоты 1//, значение которой с запасом выбирается из условия(2,5-3,0) П, где П - верхняя граничная частота сигнала П. В режиме непрерывного счета импульсовблоком 1 счета с помощью блоков 2, 3 и 5 в описанной последовательности из ОЗУ циклически считываются цифровые данные сигнала Ц, которые с помощью ЦАП 6 и первого ФНЧ 7 с АЧХ преобразуются в аналоговый сигнал - модулированный по тому или (и) иному параметру (по амплитуде или (и) фазе (частоте сигнал вспомогательной промежуточной частоты с амплитудным спектром АВПМ. Сигнал ВПМ во втором балансном модуляторе 20 выполняет балансную амплитудную модуляцию колебания . В результате модуляции образуется сигнал ПП, подаваемый аналоговым коммутатором 21 на первый фильтр 22 промежуточной частоты. Сигнал ПП имеет амплитудный спектр ПП,одна группа спектральных компонент которого расположена выше, другая - ниже (подавлен ной) частотыВО вспомогательного опорного колебания. Фильтр 22 с АЧХ ПМ выделяет одну из двух групп спектральных компонент ПП и тем самым образует модулированный сигнал ПМ промежуточной частоты с ее фактическим значением При формировании модулированных сигналов в диапазонечастотаВО не остается постоянной. Эти изменения можно компенсировать равными им по величине и соот ветствующими по знаку изменениями частотыВП . Учитывая это, значения параметров Р ,ивыбираются (варьируются) так, что при всех несущих частотах в диапазоне значениеП воспроизводит выбранное значение П с необходимой точностью. На выбор конкретных значений П ограничения не накладываются. Вытекает центральная частота полосы пропускания фильтра 22 совпадает с выбранной промежуточной частотой П вспомогательная промежуточная частотаВП изменяется в некотором поддиапазоне ВПВП в пределах полосы пропускания ФНЧ 7 (фиг. 2, 4). 9564 1 2007.08.30 Сигнал ПМ поступает через аналоговый коммутатор 24 на модулирующий вход балансного модулятора 25, где он выполняет балансную амплитудную модуляцию опорного колебания , подаваемого от делителя 33 частоты. В результате образуется сигнал ПП с амплитудным спектром ПП. Одна группа его спектральных компонент распо ложена выше, другая - ниже (подавленной) частотыО опорного колебания. С помощью одного из ПФ 19 с АЧХвыделяется одна из двух групп спектральных компонент сигнала ПП и тем самым образуется высокочастотный модулированный сигнална фактической несущей частоте(на фиг. 4 изображен случайПВОВП иНОП ). При этом значения параметров Р, , , ,ивыбираются (варьируются) так, что при всех несущих частотах в диапа зонезначениеН воспроизводит требуемое значениес необходимой точностью. В усилителе 28 сигналусиливается и регулируется (нормируется) по уровню, превращаясь тем самым в сигнал ВЫХ 2 на втором выходе системы генерирования. Его требуемый уровень устанавливается занесением в -разрядный параллельный регистр усилителя 28 из вычислительного устройства 15 через блок 16 управления по шине данных с помощью сигналов шины управления соответствующего числового значения. В случае использования одного ПФ 19 значение -П, т.е. не превышает значения промежуточной частоты. Если диапазончастот является более широким, то его в общем случае необходимо разбить наотдельных поддиапазонов и ввести в состав устройства не один,ПФ 191-19 (см. фиг. 3). Формирование модулированного сигнала в конкретном -м поддиапазоне достигается с помощью соответствующего ПФ 19,подключаемого первым 26 и вторым 27 аналоговыми коммутаторами. Одной из причин, ограничивающих функциональные возможности известной системы, является невозможность формирования модулированных сигналов в поддиапазоне несущих частот (П-)(П) (в окрестности промежуточной частоты) шириной примерно 2 П из-за прямого прохождения через соответствующий ПФ 19 мешающих спектральных компонент модулированного сигнала ПМ промежуточной частоты. Для исключения этого недостатка в предлагаемой системе генерирования применяются два значения П иП промежуточной частоты. Им соответствуют первый 22 и второй 23 фильтры промежуточной частоты. Формирование модулированных сигналовво всем диапазоне , за исключением поддиапазона (П-)(П), выполняется с использованием значения П и соответственно фильтра 22, а в поддиапазоне (П-)(П) - с применением фильтра 23, центральная частота полосы пропускания которого равнаП и выбирается за пределами этого поддиапазона. Рассмотренный механизм функционирования предлагаемой системы в режиме генерирования электрических сигналов соответствует неавтономному режиму работы, когда все управляющие воздействия (выбор вида сигналов 1 и 2, установка требуемых значений несущей частоты (частот повторения), задержки и уровней сигналов ВЫХ 1 ВЫХ 3,) поступают из вычислительного устройства 15. Благодаря наличию в блоке 16 управления полноценных полей набора и индикации, других необходимых блоков и выполнению системы по варианту с отдельным модулем генерирования сигналов, она может функционировать также в автономном режиме работы, когда после окончания режима записи (в ПЗУ 17) вычислительное устройство 15 отключается и подача всех управляющих воздействий осуществляется только из блока 16 управления с помощью его поля набора. Операции, выполняемые в автономном режиме работы (генерирования), полностью соответствуют операциям рассмотренного выше неавтономного режима генерирования. 9564 1 2007.08.30 Оценим максимальную абсолютную погрешность воспроизведения в предлагаемой системе генерирования сигналов требуемого значениянесущей частоты и выбранного значения П промежуточной частоты. С этой целью для определенности предположим, что модулирующий сигналимеет период ТМ повторения, а несущая частота формируется по варианту (см. фиг. 4)НОПО( ВОВП ) Тогда для получения требуемого значенияс учетом выполняемых над сигналами операций частота колебания Г с перестраиваемой частотой должна иметь значение а частоты опорного, вспомогательного опорногоколебаний и колеба ния ВП вспомогательной промежуточной частоты - значения соответственноГ//,/ и ВПП-ВО(ПП)/(РТМ),где , , , , , П - целые числа,0,5 ,П 0,5 . Их подстановка в выражение гдеП, //П,0,5 ,- целое число. На интервале времени Т 3 РТМ должно укладываться целое количество периодов тактовой частоты и целое количество периодов колебания вспомогательной промежуточной частоты. С учетом этого и соотношений (4) и (5) фактические значения частот колебаний Г,и ВО составляютГ/ ( ) ,/ ( ) ,ВО/ ( ) , что обеспечивает фактическое значение несущей частоты и с учетом выражения (8) максимальную абсолютную погрешность воспроизведения тре буемого значения несущей частоты 1 / (2 ) . Последняя даже в худ шем случае (Р 1) имеет малое значение (например, при М 1/ТМ 1 кГц НВ 500 Гц) и может быть дополнительно уменьшена посредством увеличения параметра Р. Учитывая , что выбранноеП и фактическоеП значения промежуточной частоты составляют ( см . (6)-(9 ПВОВП/( ПП )/,ПВОВП/ ( )/ ( ) , их разность равнаПП(/ ) / ( ) . Это соответствует максимальной абсолютной погрешности воспроизведения промежу(1/) / (2 )(1/), которая, как следуточной частотыППП ет, также мала, хотя и несколько больше, чем НВ. Отметим важную особенность предлагаемой системы генерирования. Из соотношений(4) и (5) следует, что при неизменной частотеГ колебания Г с перестраиваемой частотой и неизменных параметрах , ,ипосредством изменения параметравозможно генерирование модулированных сигналовна несущих частотах, располо женных вокруг определяемой соотношением (5) частотыи образующих сетку частот с 9564 1 2007.08.30 шагом 1/(РТМ). Такая возможность в некоторых случаях является исключительно полезной, поскольку обычно величинаоказывается намного меньшей шага сетки формируемых частот колебания Г с перестраиваемой частотой. Оценим стабильность несущей частотыгенерируемых модулированных сигналов. Для этого, как и при анализе известной системы генерирования, предположим, что перестраиваемый генератор 29 (см. фиг . 3) обладает относительной нестабильностью Г /Г , а модулированный сигнал формируется по вариантуПВОВП и НОПОВОВП . Колебания ,и ВП образуются из одного колебания Г и их частоты в соответствии с уравнениями (4) и (5) представляются в виде 1 1. С учетом последнего предположим, что в некоторый момент времени частота колебаний генератора 29 приняла значениеГГ . Ему отвечает мгновенное значение несущей частоты 1 1 и, значит, относительная нестабильность последней/. Это означает, что на любой несущей частотеН , независимо от ее абсолютного значения, обеспечивается одинаковая относительная нестабильность, равная относительной нестабильности колебания перестраиваемого генератора 29 и существенно меньшая, чем в известной системе генерирования. Источники информации Фиг. 4 Национальный центр интеллектуальной собственности. 220034, г. Минск, ул. Козлова, 20.

МПК / Метки

МПК: H03L 7/00

Метки: диапазоне, генерирования, широком, система, электрических, сигналов, частот

Код ссылки

<a href="https://by.patents.su/13-9564-sistema-generirovaniya-elektricheskih-signalov-v-shirokom-diapazone-chastot.html" rel="bookmark" title="База патентов Беларуси">Система генерирования электрических сигналов в широком диапазоне частот</a>

Предыдущий патент: Способ аутовенозной пломбировки большой подкожной вены на голени при лечении трофических язв венозной этиологии

Следующий патент: Нагревательная кольцевая печь для нагрева трубных заготовок под прошивку

Случайный патент: Разъединитель высоковольтный